半导体结构及其制备方法与流程

本发明涉及集成电路领域,尤其涉及一种半导体结构及其制备方法。

背景技术:

1、随着半导体关键尺寸缩减,晶体管会出现短沟道效应(short-channel effects),该短沟道效应包括晶体管的阈值电压随着沟道长度降低而降低、漏致势垒降低等现象。目前,业界采用在半导体结构中设置埋入式栅极来增加沟道长度,以降低短沟道效应。

2、同时,随着半导体关键尺寸的不断缩小,高介电常数金属栅极(high k metalgate,hkmg)技术几乎已经成为45nm以下制程的必备技术。采用hkmg技术制造的晶体管结构和原来的平面晶体管结构相同,只是以high-k绝缘层代替传统的sio2氧化层,并以金属材料栅极代替原来的硅材料栅极,其优势是可以提高晶体管的开关速度,并减小栅极的漏电流。

3、但是,结合埋入式栅极和hkmg两者的新型埋入式高介电常数金属栅极存在导电插塞(pc)与高介电常数金属栅极短接或者产生寄生电容的问题,因此,如何解决该些问题成为目前研究的重点。

技术实现思路

1、本公开实施例所要解决的技术问题是,提供一种半导体结构及其制备方法,其能够避免高介电常数金属栅极与导电插塞短接或者产生寄生电容,进而提高半导体结构的可靠性。

2、为了解决上述技术问题,本公开实施例提供一种半导体结构的制备方法,所述制备方法包括:提供衬底,所述衬底内设置有源区,所述有源区具有第一沟槽;在所述第一沟槽侧壁及所述衬底表面形成高介电常数材料层;去除所述衬底表面的所述高介电常数材料层,保留所述第一沟槽侧壁的所述高介电常数材料层,以作为高介电常数介质层,在垂直所述衬底表面的方向,所述高介电常数介质层的表面与所述衬底的表面平齐,或者低于所述衬底的表面;形成导电层,所述导电层覆盖所述高介电常数介质层且填满所述第一沟槽,所述导电层与所述高介电常数介质层共同作为高介电常数金属栅极。

3、在一实施例中,去除所述衬底表面的所述高介电常数材料层,保留所述第一沟槽侧壁的所述高介电常数材料层的步骤包括:在所述第一沟槽内形成第一掩膜层,所述第一掩膜层覆盖所述高介电常数材料层的表面;以所述第一掩膜层作为遮挡,去除所述衬底表面的所述高介电常数材料层。

4、在一实施例中,在所述第一沟槽内形成第一掩膜层的步骤包括:形成第一掩膜材料层,所述第一掩膜材料层填满所述第一沟槽,且覆盖所述衬底上的所述高介电常数材料层的表面;去除所述衬底上的所述高介电常数材料层表面的所述第一掩膜材料层,所述高介电常数材料层作为刻蚀停止层,保留位于所述第一沟槽内的所述第一掩膜材料层,以作为所述第一掩膜层。

5、在一实施例中,去除所述衬底表面的所述第一掩膜材料层的步骤包括:过刻蚀所述第一掩膜材料层,以去除所述第一沟槽内的部分所述第一掩膜材料层,在垂直所述衬底表面的方向,所述第一掩膜层表面低于所述高介电常数材料层表面。

6、在一实施例中,在垂直所述衬底表面的方向,所述第一掩膜层表面低于所述衬底表面。

7、在一实施例中,所述第一掩膜层表面与所述高介电常数材料层表面的高度差为所述高介电常数材料层厚度的1/2~1倍。

8、在一实施例中,去除所述衬底表面的所述第一掩膜材料层的步骤之前还包括:对所述第一掩膜材料层的表面进行平坦化处理。

9、在一实施例中,以所述第一掩膜层作为遮挡,去除所述衬底表面的所述高介电常数材料层的步骤中,采用刻蚀工艺去除所述衬底表面的所述高介电常数材料层,且刻蚀物质对所述高介电常数材料层的刻蚀速率大于对所述第一掩膜层的刻蚀速率。

10、在一实施例中,形成导电层的步骤包括:在所述衬底表面及所述第一沟槽内形成导电材料层;去除部分所述导电材料层,剩余的所述导电材料层作为所述导电层,所述高介电常数金属栅极包括设置在所述第一沟槽内的第一区域及高于所述衬底表面的第二区域,所述导电层位于所述第一区域及所述第二区域,且在所述第一区域,所述导电层覆盖所述高介电常数介质层并填满所述第一沟槽。

11、本公开实施例提供的半导体结构的制备方法,在形成导电层之前先形成高介电常数介质层,在垂直所述衬底表面的方向,所述高介电常数介质层的表面与所述衬底的表面平齐,或者低于所述衬底的表面;在形成所述导电层后,所述导电层能够覆盖所述高介电常数介质层未与所述衬底接触的全部表面,能够避免所述高介电常数介质层存在未被所述衬底或所述导电层覆盖的表面,进而避免高介电常数介质层与导电插塞短接或者产生寄生电容,即避免了高介电常数金属栅极与导电插塞短接或者产生寄生电容,大大提高了半导体结构的可靠性;同时由于在形成所述导电层之前先去除部分高介电常数材料层而形成高介电常数介质层,可提高高介电常数介质层的均匀性,进而提高了半导体结构的栅极阈值电压的稳定性。

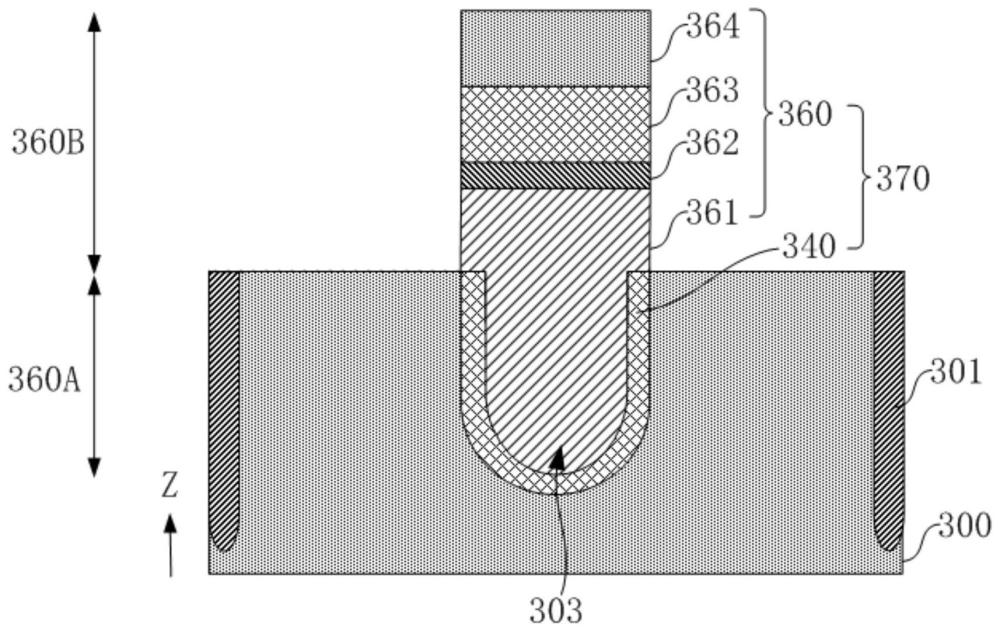

12、本公开实施例还提供了一种采用上述制备方法制备的半导体结构,包括:衬底,所述衬底内设置有源区,所述有源区具有第一沟槽;高介电常数金属栅极,包括设置在所述第一沟槽内的第一区域及高于所述衬底表面的第二区域,所述高介电常数金属栅极包括高介电常数介质层及导电层,所述高介电常数介质层设置在所述第一区域且位于所述第一沟槽侧壁,所述导电层位于所述第一区域及所述第二区域,且在所述第一区域,所述导电层覆盖所述高介电常数介质层并填满所述第一沟槽在垂直所述衬底表面的方向上,所述高介电常数介质层的表面与所述衬底的表面平齐,或者低于所述衬底的表面。

13、在一实施例中,在所述高介电常数介质层的表面与所述衬底的表面平齐时,位于所述第二区域的所述导电层还覆盖所述高介电常数介质层的表面;在所述高介电常数介质层的表面低于所述衬底的表面时,位于所述第一区域的所述导电层还覆盖所述高介电常数介质层的表面。

14、在一实施例中,所述导电层包括多晶硅层、金属阻挡层、金属层及绝缘盖层,所述多晶硅层位于所述第一区域及所述第二区域,且在所述第一区域,所述多晶硅层覆盖所述高介电常数介质层并填满所述第一沟槽,所述金属阻挡层位于所述第二区域且覆盖所述多晶硅层,所述金属层位于所述第二区域且覆盖所述金属阻挡层,所述绝缘盖层位于所述第二区域且覆盖所述金属层。

15、本公开实施例提供的半导体结构中,所述高介电常数介质层被所述衬底及所述导电层覆盖,避免了高介电常数介质层与导电插塞之间的短接或产生寄生电容,即避免了高介电常数金属栅极与导电插塞短接或者产生寄生电容,大大提高了半导体结构的可靠性;同时,所述高介电常数介质层均匀性好,提高了半导体结构的栅极阈值电压的稳定性。

技术特征:

1.一种半导体结构的制备方法,其特征在于,包括:

2.根据权利要求1所述的半导体结构的制备方法,其特征在于,去除所述衬底表面的所述高介电常数材料层,保留所述第一沟槽侧壁的所述高介电常数材料层的步骤包括:

3.根据权利要求2所述的半导体结构的制备方法,其特征在于,在所述第一沟槽内形成第一掩膜层的步骤包括:

4.根据权利要求3所述的半导体结构的制备方法,其特征在于,去除所述衬底表面的所述第一掩膜材料层的步骤包括:过刻蚀所述第一掩膜材料层,以去除所述第一沟槽内的部分所述第一掩膜材料层,在垂直所述衬底表面的方向,所述第一掩膜层表面低于所述高介电常数材料层表面。

5.根据权利要求4所述的半导体结构的制备方法,其特征在于,在垂直所述衬底表面的方向,所述第一掩膜层表面低于所述衬底表面。

6.根据权利要求4所述的半导体结构的制备方法,其特征在于,所述第一掩膜层表面与所述高介电常数材料层表面的高度差为所述高介电常数材料层厚度的1/2~1倍。

7.根据权利要求3所述的半导体结构的制备方法,其特征在于,去除所述衬底表面的所述第一掩膜材料层的步骤之前还包括:对所述第一掩膜材料层的表面进行平坦化处理。

8.根据权利要求2~7任意一项所述的半导体结构的制备方法,其特征在于,以所述第一掩膜层作为遮挡,去除所述衬底表面的所述高介电常数材料层的步骤中,采用刻蚀工艺去除所述衬底表面的所述高介电常数材料层,且刻蚀物质对所述高介电常数材料层的刻蚀速率大于对所述第一掩膜层的刻蚀速率。

9.根据权利要求1~7任意一项所述的半导体结构的制备方法,其特征在于,形成导电层的步骤包括:

10.一种采用权利要求1~9任意一项所述的制备方法制备的半导体结构,其特征在于,包括:

11.根据权利要求10所述的半导体结构,其特征在于,在所述高介电常数介质层的表面与所述衬底的表面平齐时,位于所述第二区域的所述导电层还覆盖所述高介电常数介质层的表面;在所述高介电常数介质层的表面低于所述衬底的表面时,位于所述第一区域的所述导电层还覆盖所述高介电常数介质层的表面。

12.根据权利要求10或11所述的半导体结构,其特征在于,所述导电层包括多晶硅层、金属阻挡层、金属层及绝缘盖层,所述多晶硅层位于所述第一区域及所述第二区域,且在所述第一区域,所述多晶硅层覆盖所述高介电常数介质层并填满所述第一沟槽,所述金属阻挡层位于所述第二区域且覆盖所述多晶硅层,所述金属层位于所述第二区域且覆盖所述金属阻挡层,所述绝缘盖层位于所述第二区域且覆盖所述金属层。

技术总结

一种半导体结构的制备方法包括:提供衬底,衬底内设置有源区,有源区具有第一沟槽;在第一沟槽侧壁及衬底表面形成高介电常数材料层;去除衬底表面的高介电常数材料层,保留第一沟槽侧壁的高介电常数材料层,以作为高介电常数介质层,在垂直衬底表面的方向,高介电常数介质层的表面与衬底的表面平齐,或者低于衬底的表面;形成导电层,导电层覆盖高介电常数介质层且填满第一沟槽,导电层与高介电常数介质层共同作为高介电常数金属栅极。该制备方法能够避免高介电常数介质层与导电插塞短接或者产生寄生电容,大大提高了半导体结构的可靠性;同时能够提高高介电常数介质层的均匀性,进而提高了半导体结构的栅极阈值电压的稳定性。

技术研发人员:邵波,贺珍发,陈骑龙,王震

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/12/12

- 还没有人留言评论。精彩留言会获得点赞!