三极管产品晶圆黑边不打点的版图结构及其制造方法与流程

本发明涉及半导体,具体涉及版图结构及其制造方法。

背景技术:

1、随着晶圆制造技术的成熟,客户对成本的要求是越来越高,对晶圆的黑边设计时,首先是要避免黑边(晶圆上的无效区域)上进行打点,一旦黑边打点时,墨水点的20-40微米的高度,会导致晶圆在减薄的加工中受力不均匀,产生较大比例的碎片。

2、当然也可以采用黑边全部保留氧化层的设计方案,但是,黑边全部保留氧化层会增加划片刀的损耗32%左右,因此,采用本方案的设计也是不成熟的。

3、也可以采用无效黑边区域版图上设计开划片槽的设计,此项设计可以改善划片刀的损耗问题,但是会带来背面减薄腐蚀时,由于存在氧化层与硅的台阶差异,蓝膜无法提供完整的保护,导致腐蚀的酸液顺着台阶处侵入(虹吸效应)有效管芯区域腐蚀金属层、导致聚酰亚胺光刻胶脱胶问题。

4、综上,目前缺乏一种黑边不打点的版图结构及其制备方法。

技术实现思路

1、针对现有技术存在的问题,本发明提供三极管产品晶圆黑边不打点的版图结构,已解决上述至少一个技术问题。

2、本发明提供三极管产品晶圆黑边不打点的版图结构的制造方法,已解决上述至少一个技术问题。

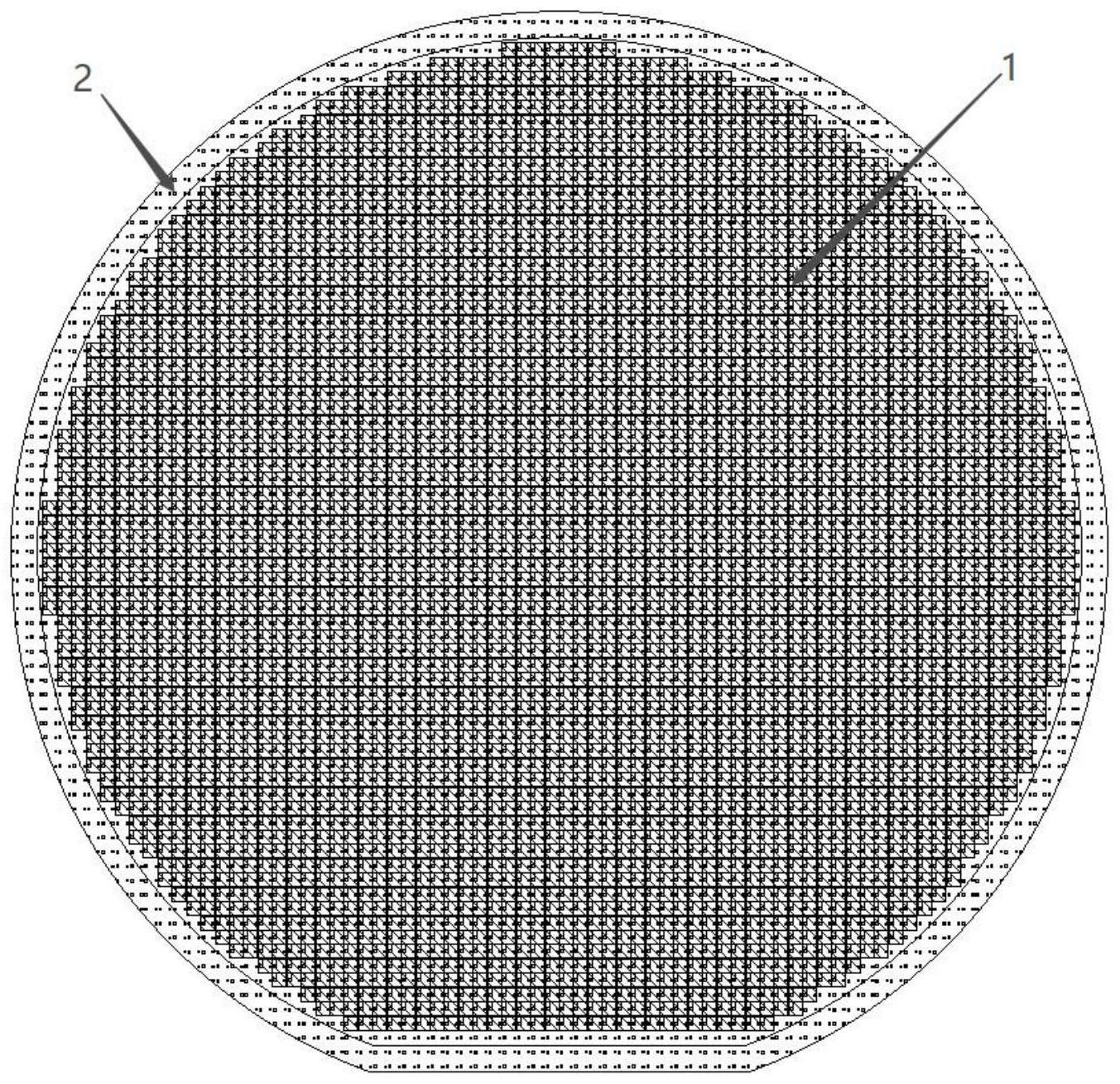

3、本发明的技术方案是:三极管产品晶圆黑边不打点的版图结构,包括芯片有效管芯区,所述芯片有效管芯区为晶圆的中心区域,其特征在于,当晶圆为5寸晶圆时,所述芯片有效管芯区是一直径为120-123mm的圆形区域;

4、当晶圆为6寸晶圆时,所述芯片有效管芯区是一直径为140-145mm圆形区域;

5、在所述芯片有效管芯区根据三极管的芯片尺寸大小进行阵列排布,当三极管的任意一条边长在所述芯片有效管芯区外时,删除三极管,以位于所有保留的三极管的图形的外围区域为黑边区域。

6、进一步优选的,所述芯片有效管芯区设置有矩阵式排布的三极管成型区;

7、所述黑边区域设置有等间隔排布的黑边成型区;

8、每个三极管成型区均包括基区测试区以及发射区测试区;

9、每个黑边成型区均包括发射区扎针区域以及基区扎针区域;

10、所述基区测试区与所述基区扎针区域位置一一对应;

11、所述发射区测试区与所述发射区扎针区域位置一一对应;

12、所述黑边成型区的发射区扎针区域设置有与所述基区测试区一致的基区结构,所述黑边成型区的基区扎针区域设置有与所述发射区测试区一致的发射区结构。

13、进一步优选的,所述三极管成型区形成pn结,所述黑边成型区形成反向的np结。

14、采用普通的矩形测试时,探针测试芯片有效管芯区与黑边区域时,被测试的器件或区域是相反的结构。便于无需打点,即可直接的对黑边区域以及芯片有效管芯区进行有效的区分。

15、进一步优选的,所述黑边区域的顶部无氧化层、无金属,且无钝化层。

16、扎针测试时直接测试在硅的表面。

17、三极管产品晶圆黑边不打点的版图结构的制备方法,其特征在于,包括如下步骤:

18、步骤一,三极管的版图设计完成后,将三极管进行阵列排布,形成三极管的图形区域;

19、对于5寸的晶圆,三极管的排布的范围的直径不小于130mm,同时,绘制直径为120-123mmmm的圆形参考区域;

20、对于6寸的晶圆,三极管的排布的范围的直径不小于160mm,同时,绘制直径为140-145mm的圆形参考区域;

21、以直径大于圆形参考区域的部分为黑边区域;

22、步骤二、删除符合条件的三极管,条件包括三极管的任意一个边长位于圆形参考区域之外,以所有保留的三极管的图形区域为芯片有效管芯区;

23、以位于所有保留的三极管的图形的外围区域为黑边区域,以黑边区域为无效的黑边管芯区域;

24、步骤三、在黑边区域设置有等间隔排布的黑边成型区;

25、所述有效管芯区设置有等间隔排布的三极管成型区;

26、每个三极管成型区均包括基区测试区,所述基区测试区与所述黑边成型区上对应的基区测试区位置的掺杂类型相反;

27、每个三极管成型区均包括发射区测试区,所述发射区测试区与所述黑边成型区上对应的发射区测试区位置的掺杂类型相反。

28、进一步优选的,步骤三中,所述基区测试区与所述黑边成型区上对应的发射区测试区位置同步掺杂。

29、进一步优选的,步骤三中,所述发射区测试区与所述黑边成型区上对应的基区测试区位置同步掺杂。

30、进一步优选的,步骤三中,光刻形成第一掺杂窗口,掺入剂量大于103的硼杂质,经过大于1000℃以上的高温炉管氧化扩散,形成氧化层厚度大于2000埃,结深大于2.0μm的柱状区域,位于芯片有效管芯区的柱状区域为基区测试区,位于黑边区域的柱状区域为发射区扎针区域;

31、随后在发射区光刻后形成第二掺杂窗口,并向其中掺入剂量大于104的磷或砷杂质,经过大于900℃以上的高温炉管氧化扩散,形成氧化层厚度大于2000埃,结深大于1.0μm的柱状区域,位于芯片有效管芯区的柱状区域为发射区测试区,位于黑边区域的柱状区域为基区扎针区域;

32、基区测试区以及发射区扎针区域的结深相同;

33、发射区测试区以及基区扎针区域的结深相同;

34、且所述基区测试区的结深大于所述发射区测试区的结深。

35、进一步优选的,步骤四,芯片有效管芯区的上方设置有氧化层、金属层以及钝化层;

36、黑边区域的上方无氧化层、金属层以及钝化层。

37、进一步优选的,测试时,根据电压差异确定当前三极管产品位于黑边区域还是芯片有效管芯区;

38、芯片有效管芯区的三极管产品的电压小于1v;

39、黑边区域的三极管产品的电压大于5v。

40、实现黑边区域不打点。

41、本发明的积极进步效果在于:

42、在不增加成本的基础上设计了晶圆的黑边与有效管芯区域的反向pn结结构,可通过矩形测试识别pn结的正向和击穿特性来分别有效管芯区域还是黑边区域,从而对黑边区域不打点,降低圆片碎片率,同时黑边区域完全不保留氧化层就可以做到不增加划片刀的损耗的同时黑边区域不存在台阶,不会产生酸液侵入有效管芯区域腐蚀金属层、导致聚酰亚胺光刻胶脱胶问题。

技术特征:

1.三极管产品晶圆黑边不打点的版图结构,包括芯片有效管芯区,所述芯片有效管芯区为晶圆的中心区域,其特征在于,当晶圆为5寸晶圆时,所述芯片有效管芯区是一直径为120-123mm的圆形区域;

2.根据权利要求1所述的三极管产品晶圆黑边不打点的版图结构,其特征在于:所述芯片有效管芯区设置有矩阵式排布的三极管成型区;

3.根据权利要求2所述的三极管产品晶圆黑边不打点的版图结构,其特征在于:所述三极管成型区形成pn结,所述黑边成型区形成反向的np结。

4.根据权利要求1所述的三极管产品晶圆黑边不打点的版图结构,其特征在于:所述黑边区域的顶部无氧化层、无金属,且无钝化层。

5.三极管产品晶圆黑边不打点的版图结构的制备方法,其特征在于,包括如下步骤:

6.根据权利要求5所述的三极管产品晶圆黑边不打点的版图结构的制备方法,其特征在于:步骤三中,所述基区测试区与所述黑边成型区上对应的发射区测试区位置同步掺杂。

7.根据权利要求5所述的三极管产品晶圆黑边不打点的版图结构的制备方法,其特征在于:步骤三中,所述发射区测试区与所述黑边成型区上对应的基区测试区位置同步掺杂。

8.根据权利要求5所述的三极管产品晶圆黑边不打点的版图结构的制备方法,其特征在于:步骤三中,光刻形成第一掺杂窗口,掺入剂量大于103的硼杂质,经过大于1000℃以上的高温炉管氧化扩散,形成氧化层厚度大于2000埃,结深大于2.0μm的柱状区域,位于芯片有效管芯区的柱状区域为基区测试区,位于黑边区域的柱状区域为发射区扎针区域;

9.根据权利要求5所述的三极管产品晶圆黑边不打点的版图结构的制备方法,其特征在于:步骤四,芯片有效管芯区的上方设置有氧化层、金属层以及钝化层;

10.根据权利要求5所述的三极管产品晶圆黑边不打点的版图结构的制备方法,其特征在于:测试时,根据电压差异确定当前三极管产品位于黑边区域还是芯片有效管芯区;

技术总结

本发明公开了三极管产品晶圆黑边不打点的版图结构及其制造方法。三极管产品晶圆黑边不打点的版图结构,包括芯片有效管芯区,所述芯片有效管芯区为晶圆的中心区域,当晶圆为5寸晶圆时,所述芯片有效管芯区是一直径为120‑123mm的圆形区域;当晶圆为6寸晶圆时,所述芯片有效管芯区是一直径为140‑145mm圆形区域;在所述芯片有效管芯区根据三极管的芯片尺寸大小进行阵列排布,当三极管的任意一条边长在所述芯片有效管芯区外时,删除三极管,以位于所有保留的三极管的图形的外围区域为黑边区域。

技术研发人员:许柏松,陈烨,赵飞,陈磊,朱瑞

受保护的技术使用者:江苏新顺微电子股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!