一种超结器件及电子器件的制作方法

本申请涉及半导体,尤其涉及一种超结器件及电子器件。

背景技术:

1、相对于传统mosfet (金属氧化物半导体场效应晶体管,metal oxidesemiconductor field effect transistor),超结mosfet在n-漂移区中引入了交替排列的n型柱、p型柱,如此,在正向导通阶段,p型柱与n型柱之间能够形成横向电场,即所谓电荷平衡;但是超结mosfet本质上仍为mosfet,其内部依然存在寄生体二极管(简称体二极管),超结mosfet的源极为体二极管的阳极,漏极为体二极管的阴极。

2、在超结mosfet开关过程中,由于超结结构中的p柱和n柱仅需要较低的vds(voltage of drain-source,源漏电压)就会分别耗尽,导致超结mosfet的cgd(capacitance of gate-drain,栅漏电容)在几十伏的漏源电压下出现一个急剧的下降,并在此后维持一个较小值,极易造成栅极电压震荡,这种震荡会影响系统的稳定性和emi(electromagnetic interference,电磁干扰噪声)特性,产生较为严重的emi,限制了超结mosfet等器件的大范围使用。

技术实现思路

1、本申请提供了一种超结器件及电子器件,以大幅减小超结器件的开关震荡,降低超结器件的电磁干扰噪声。

2、为解决上述技术问题,本申请采用如下技术方案:

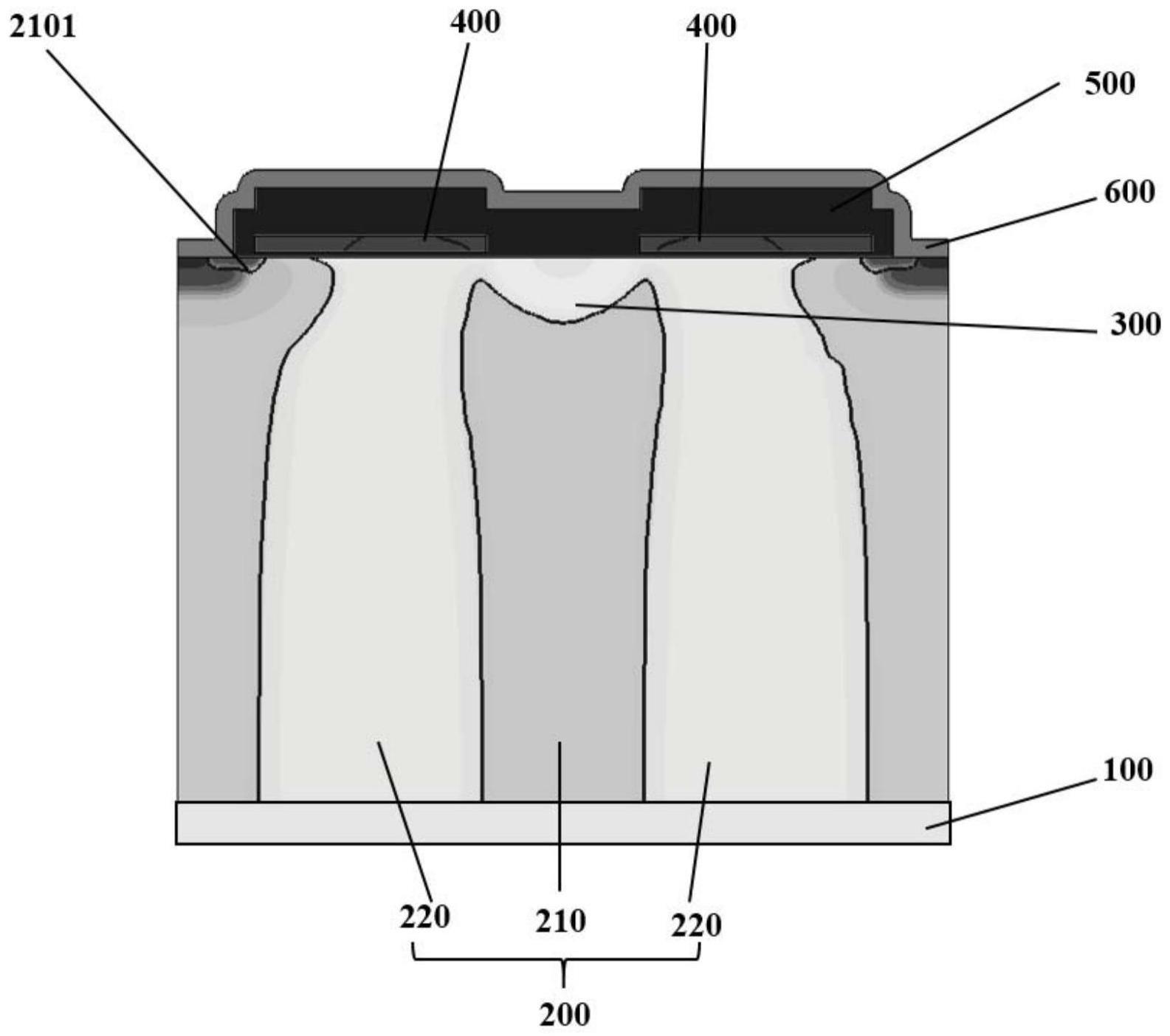

3、本申请第一方面的实施例提出了一种超结器件,超结器件包括cell区和位于所述cell区两侧的终端区,所述超结器件还包括:

4、衬底,所述衬底为第一导电类型;

5、外延层,所述外延层位于所述衬底的一侧,所述外延层的cell区包括多个第一导电类型柱及多个第二导电类型柱,所述多个第一导电类型柱与所述多个第二导电类型柱依次交替排列;

6、反形层,所述反形层设置于部分第一导电类型柱远离所述衬底的一侧,所述反形层为第二导电类型,所述反形层的两侧分别与相邻的两个第二导电类型柱电连接。

7、根据本申请实施例提供的超结器件,外延层的cell区中设有多个第一导电类型柱和多个第二导电类型柱,第一导电类型与第二导电类型的导电类型相反,以第一导电类型为p型,第二导电类型为n型为例,多个p型柱中部分p型柱远离衬底的一侧设置有反形层,反形层的导电类型与n柱相同,且反形层的两侧分别和与该反形层相邻的两个n柱相连接。本申请实施例中,由于部分相邻的n柱通过反形层连通,相当于反形层使得部分n柱的宽度增加。又由于cgd (栅漏电容)与n柱的宽度呈正相关,通过设置反形层使得部分n柱的宽度增加,以此增大cgd,进而使开关过程中电流变化率di/dt和电压变化率dv/dt降低,如此,能够大幅减小超结器件的开关震荡,降低超结器件的电磁干扰噪声。

8、此外,根据本申请实施例中的超结器件还可以具有以下技术特征:

9、在本申请的一些实施例中,设有所述反形层的多个第一导电类型柱与未设有所述反形层的多个第一导电类型柱依次交替排列。

10、在本申请的一些实施例中,沿所述反形层的中部至相邻的第二导电类型柱的方向上,所述反形层的厚度逐渐减小。

11、在本申请的一些实施例中,所述反形层的导电离子浓度小于与所述反形层相邻的第二导电类型柱的导电离子浓度。

12、在本申请的一些实施例中,所述衬底及所述第一导电类型柱为p型,所述第二导电类型柱为n型。

13、在本申请的一些实施例中,所述超结器件还包括p-body层,所述p-body层位于未设有所述反形层的第一导电类型柱远离所述衬底的一侧,所述p-body层与所述反形层同层设置。

14、在本申请的一些实施例中,所述p-body层的导电离子浓度小于所述第一导电类型柱的导电离子浓度。

15、在本申请的一些实施例中,所述超结器件还包括位于所述多个第二导电类型柱上且沿远离所述衬底的方向依次层叠设置的第一氧化层、栅极多晶硅层、第二氧化层及金属层,所述栅极多晶硅层与所述终端区的栅极金属层连接;未设有所述反形层的第一导电类型柱上设有两个源极区,所述金属层与所述两个源极区连接。

16、本申请第二方面的实施例提出了一种电子器件,包括第一方面任一实施例中的超结器件。

17、根据本申请实施例中的电子器件,由于其具有第一方面任一实施例中的超结器件,因此其也具备第一方面任一实施例的有益效果,此处不再赘述。

技术特征:

1.一种超结器件,所述超结器件包括cell区和位于所述cell区两侧的终端区,其特征在于,所述超结器件还包括:

2.根据权利要求1所述的超结器件,其特征在于,设有所述反形层的多个第一导电类型柱与未设有所述反形层的多个第一导电类型柱依次交替排列。

3.根据权利要求1所述的超结器件,其特征在于,沿所述反形层的中部至相邻的第二导电类型柱的方向上,所述反形层的厚度逐渐减小。

4.根据权利要求1所述的超结器件,其特征在于,所述反形层的导电离子浓度小于与所述反形层相邻的第二导电类型柱的导电离子浓度。

5.根据权利要求1所述的超结器件,其特征在于,所述衬底及所述第一导电类型柱为p型,所述第二导电类型柱为n型。

6.根据权利要求5所述的超结器件,其特征在于,所述超结器件还包括p-body层,所述p-body层位于未设有所述反形层的第一导电类型柱远离所述衬底的一侧,所述p-body层与所述反形层同层设置。

7.根据权利要求6所述的超结器件,其特征在于,所述p-body层的导电离子浓度小于所述第一导电类型柱的导电离子浓度。

8.根据权利要求1所述的超结器件,其特征在于,所述超结器件还包括位于所述多个第二导电类型柱上且沿远离所述衬底的方向依次层叠设置的第一氧化层、栅极多晶硅层、第二氧化层及金属层,所述多晶硅层与所述终端区的栅极金属层连接;未设有所述反形层的第一导电类型柱上设有两个源极区,所述金属层与所述两个源极区连接。

9.一种电子器件,其特征在于,包括权利要求1至8中任一项所述的超结器件。

技术总结

本申请的实施例提出了一种超结器件及电子器件。超结器件包括cell区和位于所述cell区两侧的终端区,超结器件还包括衬底、外延层和反形层,其中,衬底为第一导电类型;外延层位于衬底的一侧,外延层的cell区包括多个第一导电类型柱及多个第二导电类型柱,多个第一导电类型柱与多个第二导电类型柱依次交替排列;反形层设置于部分第一导电类型柱远离衬底的一侧,反形层为第二导电类型,反形层的两侧分别与相邻的两个第二导电类型柱电连接。本申请的超结器件能够使部分第二导电类型柱的宽度增加,从而增大栅漏电容,进而使开关过程中电流变化率和电压变化率降低,如此,能够大幅减小超结器件的开关震荡,降低超结器件的电磁干扰噪声。

技术研发人员:栗终盛,柴展,罗杰馨

受保护的技术使用者:上海功成半导体科技有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!