半导体装置的制作方法

示例实施例涉及半导体装置。更具体地,示例实施例涉及具有隔离图案的半导体装置。

背景技术:

1、隔离层可被形成在基底上以限定有源区域,并且晶体管可被形成在有源区域上。由于半导体装置具有高集成度,因此在隔离层的背对侧处的邻近有源区域之间的电绝缘特性可被劣化。

技术实现思路

1、示例实施例提供具有增强的特性的半导体装置。

2、根据示例实施例,提供一种半导体装置。所述半导体装置可包括:第一隔离结构,延伸穿过基底的上部并限定第一有源区域;第一栅极结构,在基底上;以及第一源极/漏极区域,在与第一栅极结构邻近的第一有源区域的上部处。第一隔离结构可包括上隔离图案结构和下隔离图案。上隔离图案结构可包括第一隔离图案和覆盖第一隔离图案的侧壁的第二隔离图案。下隔离图案可被形成在上隔离图案结构的下方并接触上隔离图案结构,并且下隔离图案的宽度可大于上隔离图案结构的宽度。

3、根据示例实施例,提供一种半导体装置。所述半导体装置可包括:第一隔离结构、杂质区域、第一栅极结构、第一源极/漏极区域、第二隔离结构、第二栅极结构和第二源极/漏极区域。基底可包括第一区域和第二区域。第一隔离结构可延伸穿过基底的第一区域的上部,并且可限定第一有源区域。杂质区可被形成在基底中的第一隔离结构的下方。第一栅极结构可被形成在基底的第一区域上。第一源极/漏极区域可被形成在与第一栅极结构邻近的第一有源区域的上部处。第二隔离结构可延伸穿过基底的第二区域的上部,并且可限定第二有源区域。第二栅极结构可被形成在基底的第二区域上。第二源极/漏极区域可被形成在与第二栅极结构邻近的第二有源区域的上部处。第一隔离结构可包括上隔离图案结构和在上隔离图案结构的下方并接触上隔离图案结构的下隔离图案。下隔离图案的宽度可大于上隔离图案结构的宽度。

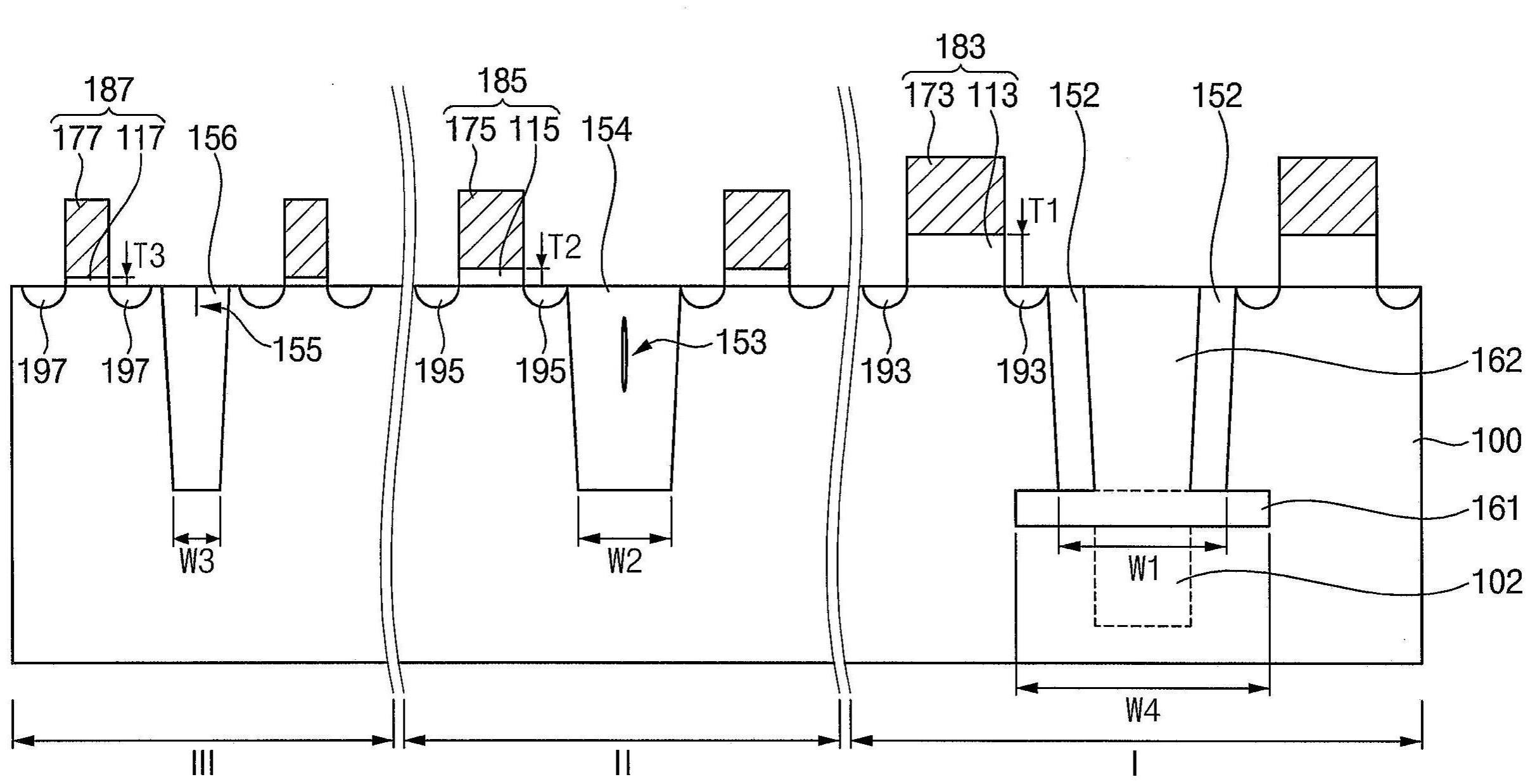

4、根据示例实施例,提供一种半导体装置。所述半导体装置可包括:第一隔离结构,延伸穿过基底的第一区域的上部,并且限定第一有源区域,基底包括第一区域、第二区域和第三区域;杂质区域,在基底中的第一隔离结构的下方;第一栅极结构,在基底的第一区域上;第一源极/漏极区域,在与第一栅极结构邻近的第一有源区域的上部处;第二隔离结构,延伸穿过基底的第二区域的上部,并且限定第二有源区域;第二栅极结构,在基底的第二区域上;第二源极/漏极区域,在与第二栅极结构邻近的第二有源区域的上部处;第三隔离结构,延伸穿过基底的第三区域的上部,并且限定第三有源区域;第三栅极结构,在基底的第三区域上;以及第三源极/漏极区域,在与第三栅极结构邻近的第三有源区域的上部处。第一隔离结构可包括上隔离图案结构和在上隔离图案结构的下方并接触上隔离图案结构的下隔离图案。下隔离图案的宽度可大于上隔离图案结构的宽度。

5、在根据示例实施例的制造半导体装置的方法中,当用于形成隔离结构的沟槽被形成在基底中时,离子注入工艺可被执行以增强隔离特性。附加地,隔离图案可被形成在沟槽的侧壁上,并且可用作离子注入掩模的一部分,并且可通过离子注入工艺形成的杂质区域的宽度可通过隔离图案的厚度而被控制。

6、此外,在离子注入工艺之后,具有大于沟槽的宽度的宽度的附加沟槽可被形成在沟槽的下方,并且隔离结构可被形成在沟槽和附加沟槽中。因此,可防止杂质区域中的杂质扩散到邻近的有源区域中。因此,有源区域上的晶体管的阈值电压的变化可减小。

技术特征:

1.一种半导体装置,包括:

2.根据权利要求1所述的半导体装置,其中,下隔离图案的下表面具有弯曲且向下凸出的形状。

3.根据权利要求1所述的半导体装置,其中,下隔离图案包括与第一隔离图案的材料相同的材料。

4.根据权利要求1所述的半导体装置,其中,第一隔离图案和第二隔离图案以及下隔离图案包括氧化硅。

5.根据权利要求1所述的半导体装置,还包括:杂质区域,在基底中的下隔离图案的下方。

6.根据权利要求5所述的半导体装置,其中,杂质区域的宽度小于上隔离图案结构的宽度。

7.根据权利要求1至6中任一项所述的半导体装置,其中:

8.根据权利要求7所述的半导体装置,其中,第三隔离图案包括与第二隔离图案的材料相同的材料。

9.根据权利要求7所述的半导体装置,其中,第三隔离图案的宽度小于上隔离图案结构的宽度。

10.根据权利要求7所述的半导体装置,其中,第三隔离图案的下表面与上隔离图案结构的下表面共面。

11.根据权利要求7所述的半导体装置,其中,空隙或缝隙被形成在第三隔离图案中。

12.根据权利要求7所述的半导体装置,其中:

13.根据权利要求7所述的半导体装置,其中,第一栅极结构和第一源极/漏极区域形成第一晶体管,并且第二栅极结构和第二源极/漏极区域形成第二晶体管,并且

14.一种半导体装置,包括:

15.根据权利要求14所述的半导体装置,其中,上隔离图案结构包括:

16.根据权利要求15所述的半导体装置,其中,第二隔离结构包括与第二隔离图案的材料相同的材料,并且下隔离图案包括与第一隔离图案的材料相同的材料。

17.根据权利要求14至16中任一项所述的半导体装置,其中,杂质区域的宽度小于上隔离图案结构的宽度。

18.根据权利要求14至16中任一项所述的半导体装置,其中,第二隔离结构的宽度小于上隔离图案结构的宽度。

19.一种半导体装置,包括:

20.根据权利要求19所述的半导体装置,其中,第二隔离结构的宽度大于第三隔离结构的宽度,并且第一隔离结构的宽度大于第二隔离结构的宽度。

技术总结

提供半导体装置。所述半导体装置包括:第一隔离结构,延伸穿过基底的上部并限定第一有源区域;第一栅极结构,在基底上;以及第一源极/漏极区域,在与第一栅极结构邻近的第一有源区域的上部处。第一隔离结构包括上隔离图案结构和下隔离图案。上隔离图案结构包括第一隔离图案和覆盖第一隔离图案的侧壁的第二隔离图案。下隔离图案被形成在上隔离图案结构的下方并接触上隔离图案结构,并且下隔离图案的宽度大于上隔离图案结构的宽度。

技术研发人员:李东镇,林濬熙,尹康五,李素贤

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!