半导体器件的制作方法

本公开总体上涉及一种半导体器件,并且更具体地,涉及一种包括多桥沟道场效应晶体管(mbcfettm)的半导体器件。

背景技术:

1、包括在衬底上呈鳍形形状和/或纳米线形状的多个硅体且在硅体的表面上形成栅极的多沟道晶体管已经被建议作为用于增加半导体器件的密度的缩放技术。

2、此类多沟道晶体管可以使用三维沟道结构,该三维沟道结构可以促进多沟道晶体管的缩放。备选地或附加地,即使不增加多沟道晶体管的栅极长度,也可以提高多沟道晶体管的电流控制能力。此外,可以抑制沟道区的电势受漏极电压影响的短沟道效应(sce)。

技术实现思路

1、本公开可以提供一种半导体器件,其中,在上栅电极堆叠在底部栅电极的结构中,栅极切割的用于隔离上栅电极的部分的宽度大于栅极切割的用于隔离底部栅电极的另一部分的宽度。为此,可以形成连接到底部源/漏接触部的通孔,该通孔在水平方向上不与上栅电极重叠,并且因此,可以防止在上栅电极和通孔之间发生短路。

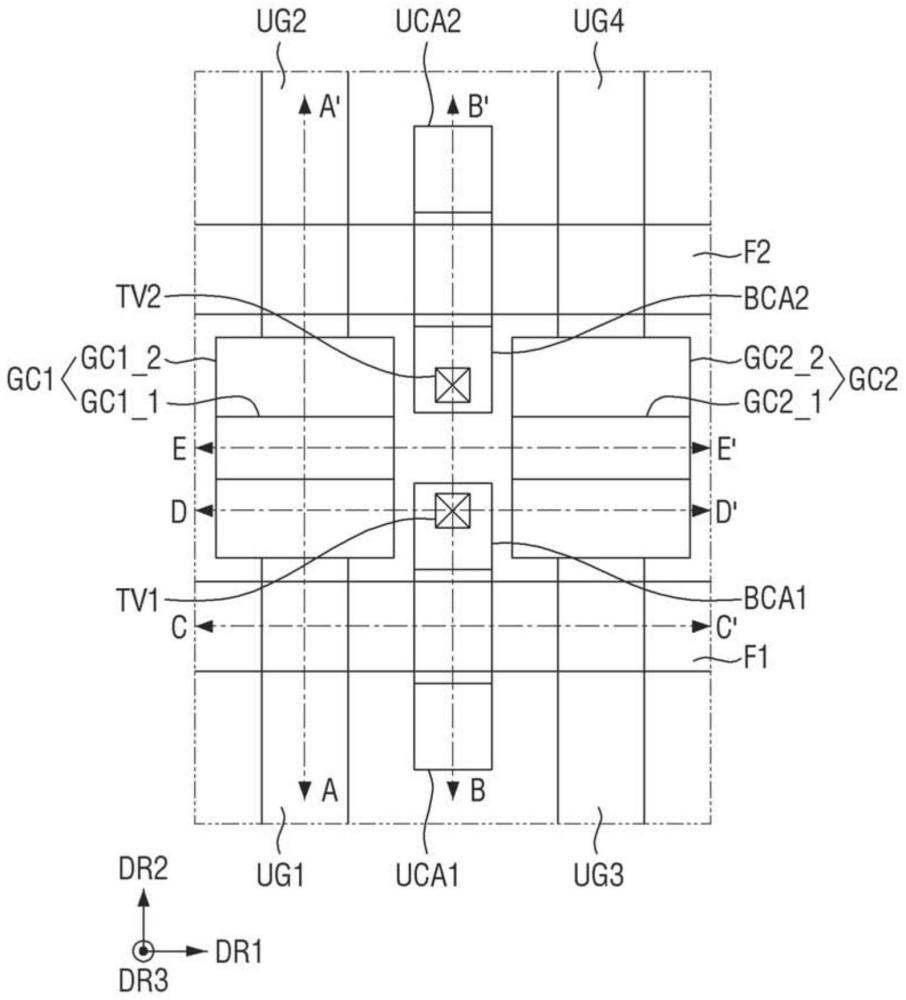

2、根据本公开的一个方面,提供了一种半导体器件。该半导体器件包括在衬底上沿第一水平方向延伸的第一有源图案。该半导体器件还包括在衬底上沿第一水平方向延伸的第二有源图案。第二有源图案在与第一水平方向不同的第二水平方向上与第一有源图案间隔开。半导体器件还包括在第一有源图案上沿第二水平方向延伸的第一底部栅电极。半导体器件还包括在第一底部栅电极上沿第二水平方向延伸的第一上栅电极。第一上栅电极在竖直方向上与第一底部栅电极间隔开。半导体器件还包括在第二有源图案上沿第二水平方向延伸的第二底部栅电极。第二底部栅电极在第二水平方向上与第一底部栅电极间隔开。半导体器件还包括在第二底部栅电极上沿第二水平方向延伸的第二上栅电极。第二上栅电极在竖直方向上与第二底部栅电极间隔开。第二上栅电极在第二水平方向上与第一上栅电极间隔开。半导体器件还包括第一栅极切割,该第一栅极切割包括第一部分和第二部分,第一部分将第一底部栅电极与第二底部栅电极隔离,第二部分将第一上栅电极与第二上栅电极隔离。第一栅极切割的第二部分在第二水平方向上的宽度超过第一栅极切割的第一部分在第二水平方向上的宽度。第一栅极切割的第二部分在竖直方向上与第一底部栅电极和第二底部栅电极中的至少一个重叠。

3、根据本公开的一个方面,提供了一种半导体器件。该半导体器件包括在衬底上沿第一水平方向延伸的第一有源图案。该半导体器件还包括在衬底上沿第一水平方向延伸的第二有源图案。第二有源图案在与第一水平方向不同的第二水平方向上与第一有源图案间隔开。半导体器件还包括在第一有源图案上沿第二水平方向延伸的第一底部栅电极。半导体器件还包括在第一底部栅电极上沿第二水平方向延伸的第一上栅电极。第一上栅电极在竖直方向上与第一底部栅电极间隔开。半导体器件还包括在第二有源图案上沿第二水平方向延伸的第二底部栅电极。第二底部栅电极在第二水平方向上与第一底部栅电极间隔开。半导体器件还包括在第二底部栅电极上沿第二水平方向延伸的第二上栅电极。第二上栅电极在竖直方向上与第二底部栅电极间隔开。第二上栅电极在第二水平方向上与第一上栅电极间隔开。半导体器件还包括设置在第一有源图案上且在第一底部栅电极的一侧的第一底部源/漏区。半导体器件还包括被配置为覆盖第一底部源/漏区的层间绝缘层。半导体器件还包括设置在层间绝缘层内并耦接到第一底部源/漏区的第一底部源/漏接触部。半导体器件还包括通过在竖直方向上穿过层间绝缘层耦接到第一底部源/漏接触部的第一通孔。第一通孔在第一水平方向上与第一上栅电极不重叠。第一上栅电极和第二上栅电极之间的在第二水平方向上的间距超过第一底部栅电极和第二底部栅电极之间的在第二水平方向上的间距。

4、根据本公开的一个方面,提供了一种半导体器件。该半导体器件包括在衬底上沿第一水平方向延伸的第一有源图案。该半导体器件还包括在衬底上沿第一水平方向延伸的第二有源图案。第二有源图案在与第一水平方向不同的第二水平方向上与第一有源图案间隔开。半导体器件还包括在竖直方向上彼此间隔开地堆叠在第一有源图案上的多个第一底部纳米片。半导体器件还包括在竖直方向上彼此间隔开地堆叠在多个第一底部纳米片上的多个第一上纳米片。半导体器件还包括在竖直方向上彼此间隔开地堆叠在第二有源图案上的多个第二底部纳米片。半导体器件还包括在竖直方向上彼此间隔开地堆叠在多个第二底部纳米片上的多个第二上纳米片。半导体器件还包括在第一有源图案上沿第二水平方向延伸的第一底部栅电极。第一底部栅电极围绕多个第一底部纳米片。半导体器件还包括在第一底部栅电极上沿第二水平方向延伸的第一上栅电极。第一上栅电极在竖直方向上与第一底部栅电极间隔开。第一上栅电极围绕多个第一上纳米片。半导体器件还包括在第二有源图案上沿第二水平方向延伸的第二底部栅电极。第二底部栅电极在第二水平方向上与第一底部栅电极间隔开。第二底部栅电极围绕多个第二底部纳米片。半导体器件还包括在第二底部栅电极上沿第二水平方向延伸的第二上栅电极。第二上栅电极在竖直方向上与第二底部栅电极间隔开。第二上栅电极在第二水平方向上与第一上栅电极间隔开。第二上栅电极围绕多个第二上纳米片。半导体器件还包括栅极切割,该栅极切割包括第一部分和第二部分,第一部分将第一底部栅电极与第二底部栅电极隔离,第二部分将第一上栅电极与第二上栅电极隔离。半导体器件还包括设置在第一有源图案上且在第一底部栅电极的一侧的底部源/漏区。半导体器件还包括被配置为覆盖底部源/漏区的层间绝缘层。半导体器件还包括设置在层问绝缘层内并耦接到底部源/漏区的底部源/漏接触部。半导体器件还包括通过在竖直方向上穿过层间绝缘层耦接到底部源/漏接触部的通孔。通孔在第一水平方向上与栅极切割的第二部分重叠。栅极切割的第二部分在第二水平方向上的宽度超过栅极切割的第一部分在第二水平方向上的宽度。

5、本公开的目的不限于以上提及的那些,并且本领域技术人员将根据本公开的以下描述清楚地理解本文中未提及的本公开的附加目的。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,还包括:

3.根据权利要求2所述的半导体器件,还包括:

4.根据权利要求2所述的半导体器件,其中,所述第一栅极切割的所述第二部分与所述多个第一上纳米片和所述多个第二上纳米片中的每一个接触。

5.根据权利要求1所述的半导体器件,还包括:

6.根据权利要求1所述的半导体器件,还包括:

7.根据权利要求6所述的半导体器件,还包括:

8.根据权利要求6所述的半导体器件,还包括:

9.根据权利要求1所述的半导体器件,其中,所述第一栅极切割的所述第二部分的下表面与所述第一底部栅电极和所述第二底部栅电极中的每一个接触。

10.根据权利要求1所述的半导体器件,其中,所述第一栅极切割的所述第一部分的第一材料与所述第一栅极切割的所述第二部分的第二材料不同。

11.根据权利要求10所述的半导体器件,其中,所述第一栅极切割的所述第一部分的上表面与所述第一栅极切割的所述第二部分的下表面接触。

12.根据权利要求10所述的半导体器件,其中,所述第一栅极切割的所述第二部分围绕所述第一栅极切割的在所述第一上栅电极和所述第二上栅电极之间的所述第一部分的侧壁。

13.根据权利要求1所述的半导体器件,其中,所述第一栅极切割的与所述第一底部栅电极接触的所述第一部分的第一侧壁具有相对于所述第一栅极切割的与所述第一上栅电极接触的所述第二部分的第二侧壁倾斜的轮廓。

14.一种半导体器件,包括:

15.根据权利要求14所述的半导体器件,还包括:

16.根据权利要求15所述的半导体器件,还包括:

17.根据权利要求15所述的半导体器件,其中,所述栅极切割的所述第二部分的下表面与所述第一底部栅电极和所述第二底部栅电极中的每一个接触。

18.根据权利要求15所述的半导体器件,其中,所述栅极切割的所述第一部分的第一材料与所述栅极切割的所述第二部分的第二材料不同。

19.根据权利要求14所述的半导体器件,还包括:

20.一种半导体器件,包括:

技术总结

在一些实施例中,一种半导体器件包括:第一有源图案,在衬底上沿第一水平方向延伸;第二有源图案,在衬底上沿第一水平方向延伸;第一底部栅电极,在第一有源图案上沿第二水平方向延伸;第一上栅电极,在第一底部栅电极上沿第二水平方向延伸;第二底部栅电极,在第二有源图案上沿第二水平方向延伸;第二上栅电极,在第二底部栅电极上沿第二水平方向延伸;以及第一栅极切割,包括第一部分和第二部分,第一部分将第一底部栅电极与第二底部栅电极隔离,第二部分将第一上栅电极与第二上栅电极隔离。第二部分的宽度超过第一部分的宽度。

技术研发人员:黄东勋,宋昇珉,郭玟灿

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!