一种7mask半导体阵列基板制造方法与流程

本发明属于显示装置中的tft阵列基板的制备,具体是指一种7mask半导体阵列基板制造方法。

背景技术:

1、液晶显示面板的工作原理是在两片平行的玻璃基板当中放置液晶分子,两片玻璃基板中间有许多垂直和水平的细小电线,通过通电与否来控制液晶分子改变方向,将背光模组的光线折射出来产生画面。通常液晶显示面板由彩膜(cf,colorfilter)基板、薄膜晶体管(tft,thinfilmtransistor)基板、夹于彩膜基板与薄膜晶体管基板之间的液晶(lc,liquidcrystal)及密封胶框(sealant)组成。

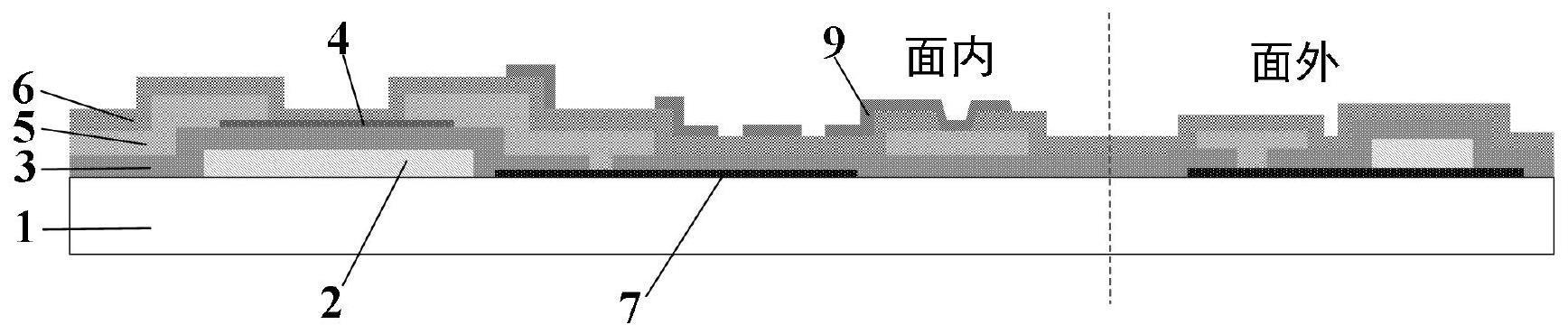

2、现有的in-cell技术是指将触摸面板功能嵌入到液晶像素中的方法,从而实现触摸面板部件与液晶面板一体化的设计。目前市场主流的阵列基板(tft)设计主要围绕的是9道mask的topcomincell技术,如图1所示为9道mask的阵列基板结构示意图,这种topcom的设计主要是通过在sd制程同时形成tpline和dataline,不仅制程稳定,同时还具有主动笔功能。

3、由于市场竞争越发激烈以及各面板制程工艺的稳定,高良率表现,如何提高产品竞争力显得尤为重要,特别是不同工艺设计的面板价格,为此,如何优化工艺及降低成本情况下,并保证高良率逐步成为产品开发的主要目标。

技术实现思路

1、本发明所要解决的技术问题在于提供一种7mask半导体阵列基板制造方法。

2、本发明是这样实现的:

3、一种7mask半导体阵列基板制造方法,包括如下步骤:

4、第一步:采用pvd方式在玻璃基板上沉积第一透明电极层,并进行图案化,作为像素电极;

5、第二步:采用pvd方式沉积并图案化形成第一金属层,为栅极金属层,;

6、第三步:采用cvd方式沉积一层第一绝缘层,为栅极绝缘层;

7、第四步:采用pvd方式沉积一层有源层,并进行图案化;

8、第五步:对面内、面外的绝缘层进行开孔,包括:像素电极与源漏极搭接孔、像素电极桥接面外第二金属走线孔;

9、第六步:采用pvd方式沉积并图案化形成第二金属层,为源漏极金属层;

10、第七步:采用cvd方式沉积一层第二绝缘层,为钝化绝缘层;

11、第八步:对面内绝缘层进行开孔,为公共电极与面内触控层搭接孔;

12、第九步:图案化第二透明电极层,为公共电极。

13、进一步地,所述第一步中,所述第一透明电极层选用ito。

14、进一步地,所述第二步中,所述第一金属层选用mo/al/mo。

15、进一步地,所述第三步中,所述第一绝缘层选用siox。

16、进一步地,所述第四步中,所述有源层选用igzo。

17、进一步地,所述第六步中,所述第二金属层选用mo/al/mo。

18、进一步地,所述第七步中,所述第二绝缘层选用siox。

19、本发明的优点在于:

20、1、基于现有的top-com设计原理的情况下,通过工艺优化,生产上减少两道mask及对应的制程,9mask阵列基板减少两道mask至7mask,其中一道mask为原gip区域(面外,提供栅极驱动信号)第一金属走线/第二金属走线搭接过孔mask,共用第二绝缘层的开孔光罩,用像素电极来桥接面外的第一金属走线和第二金属走线,起到传输信号的作用;另一道mask为有机平坦层。

21、2、变更像素电极、第一金属层和第二金属层的成膜顺序,优先图案化像素电极ito,减少了ito爬坡孔与孔之间的距离,处于最平整的位置。

22、3、减少一道第三绝缘层的成膜(原设计的像素电容层),以第二绝缘层作为现有的像素电容层。

23、4、本发明的方法达到降低生产成本,提高生产效益的目的。

技术特征:

1.一种7mask半导体阵列基板制造方法,其特征在于:包括如下步骤:

2.如权利要求1所述的一种7mask半导体阵列基板制造方法,其特征在于:所述第一步中,所述第一透明电极层选用ito。

3.如权利要求1所述的一种7mask半导体阵列基板制造方法,其特征在于:所述第二步中,所述第一金属层选用mo/al/mo。

4.如权利要求1所述的一种7mask半导体阵列基板制造方法,其特征在于:所述第三步中,所述第一绝缘层选用siox。

5.如权利要求1所述的一种7mask半导体阵列基板制造方法,其特征在于:所述第四步中,所述有源层选用igzo。

6.如权利要求1所述的一种7mask半导体阵列基板制造方法,其特征在于:所述第六步中,所述第二金属层选用mo/al/mo。

7.如权利要求1所述的一种7mask半导体阵列基板制造方法,其特征在于:所述第七步中,所述第二绝缘层选用siox。

技术总结

一种7mask半导体阵列基板制造方法,包括:在玻璃基板上沉积第一透明电极层,并进行图案化;沉积并图案化形成第一金属层;沉积一层第一绝缘层;沉积一层有源层,并进行图案化;对面内、面外的绝缘层进行开孔,包括:像素电极与源漏极搭接孔、像素电极桥接面外第二金属走线孔;沉积并图案化形成第二金属层;沉积一层第二绝缘层;对面内绝缘层进行开孔,为公共电极与面内触控层搭接孔;图案化第二透明电极层,为公共电极。本发明通过工艺优化,9Mask阵列基板减少两道Mask至7Mask,变更像素电极、第一金属层和第二金属层的成膜顺序,优先图案化像素电极ITO,减少了ITO爬坡孔与孔之间的距离,处于最平整的位置。

技术研发人员:陈伟,潜垚

受保护的技术使用者:华映科技(集团)股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!