一种芯片的三维堆叠结构和堆叠方法与流程

本发明涉及芯片封装,特别涉及一种芯片的三维堆叠结构和堆叠方法。

背景技术:

1、近年来,随着人工智能技术行业的迅猛发展,芯片逐渐向小尺寸、高集成度、大算力和低功耗方向发展,为了满足芯片的发展需求,三维堆叠封装技术应运而生,三维堆叠封装被认为是超越摩尔定律和开发高密度、小体积和多功能化器件的首选技术解决方案。

2、三维堆叠封装的核心是硅通孔技术,硅通孔技术需要通过在芯片等硅介质中刻蚀导电通孔,在形成绝缘层后再沉积如铜、钨等导电材料,从而实现各芯片间的短距离垂直互连。三维堆叠封装具有高性能、宽带宽、低功耗、低信号延迟、小尺寸等特点,然而由于三维堆叠封装的高集成度,芯片的热密度也更高,使得三维堆叠封装过程中的热问题愈发严峻;并且芯片在工作时硅通孔结构会产生较高的热量,该热量使得芯片中的有源器件的载流子迁移率发生改变,严重时甚至导致芯片的工作性能失效。因此,为了解决上述问题,有必要研究一种热应力小,散热性能好,且能够保证芯片工作性能的三维堆叠方法和堆叠结构。

技术实现思路

1、本发明实施例提供了一种芯片的三维堆叠结构及堆叠方法,能够减小芯片封装过程中热应力的累积,且能够有效增强芯片封装的散热能力,保证芯片的正常工作性能。

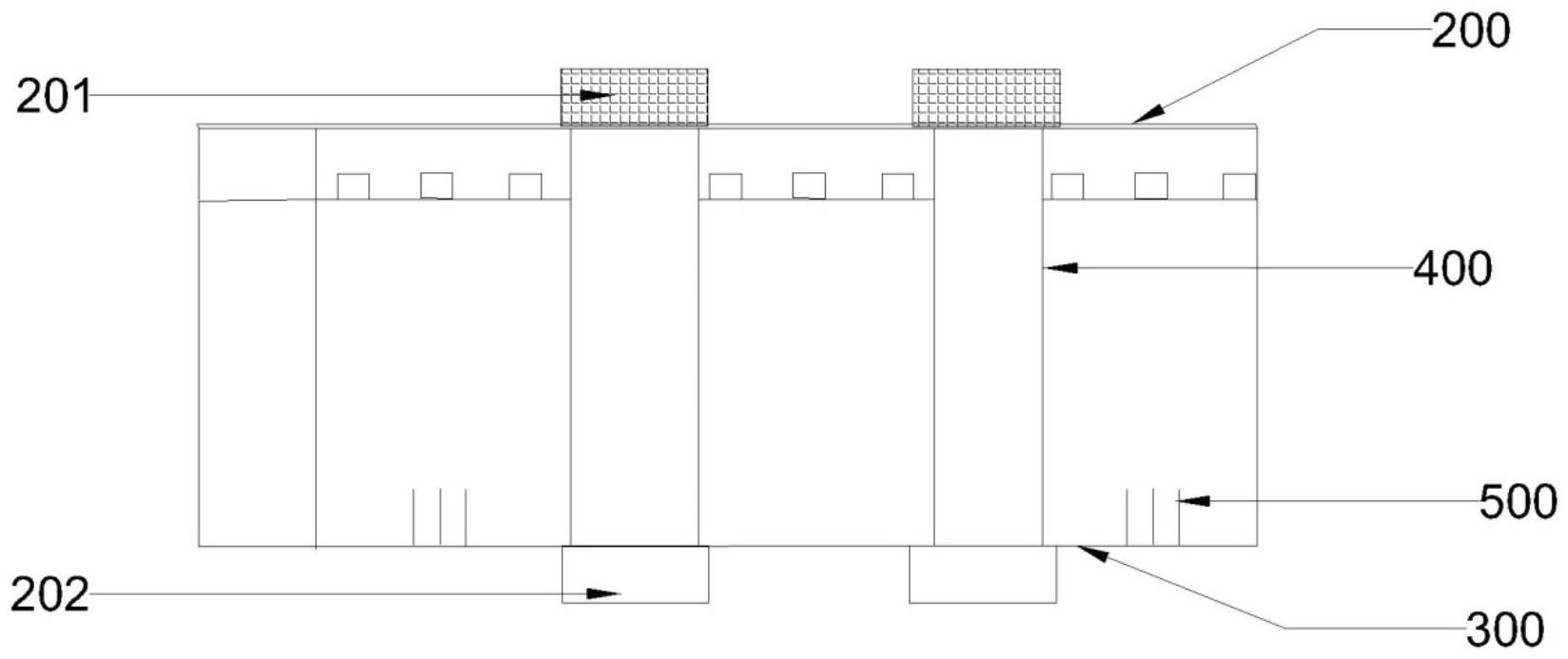

2、第一方面,本发明提供了一种芯片的三维堆叠结构,其特征在于,包括:至少两个芯片层;

3、每个芯片层包括厚度方向相对的功能面和非功能面;

4、所述功能面上设有多个硅通孔结构,所述硅通孔结构贯穿每个芯片层的功能面和非功能面,各硅通孔结构在所述功能面上呈菱形阵列排布,所述功能面上设有金属布线层,所述硅通孔结构的其中一端与所述金属布线层相连接;

5、所述非功能面上设有多个纳米孔,所述纳米孔用于对每个芯片层进行散热;

6、每个芯片层的功能面上设有焊盘,非功能面上设有键合焊盘,所述焊盘与所述功能面上的金属布线层相连接,所述键合焊盘与所述非功能面上的硅通孔结构相连接,所述至少两个芯片层中的第一芯片和第二芯片通过所述焊盘和所述键合焊盘相键合。

7、优选地,所述硅通孔结构的半径为5~10μm,深度为50~100μm,相邻硅通孔之间的间隔为18~20μm。

8、优选地,所述硅通孔结构包括从内向外依次设置的圆柱形导电层、第一环形介质层、环形导电层和第二环形介质层,所述圆柱形导电层、第一环形介质层、环形导电层和第二环形介质层的圆心相同;其中,所述第一环形介质层包括第一扇环介质层和第二扇环介质层,所述第一扇环介质层中填充为聚合物材料,所述第二扇环介质层为空心。

9、优选地,所述圆柱形导电层的半径为0.5~1μm,所述第一环形介质层的宽度为0.1~0.8μm;所述环形导电层的宽度为2~5μm;所述第二环形介质层的宽度为2.4~4μm。

10、优选地,所述聚合物为su-8光刻胶、聚碳酸亚丙酯或苯并环丁烯中的至少一种;

11、所述第一扇环介质层和所述第二扇环介质层均由两个相对设置的扇环组成,其中填充聚合物材料的扇环所对应的圆心角为45°~150°。

12、第二方面,本发明还提供了一种上述第一方面任一项所述的三维堆叠结构的堆叠方法,该堆叠方法包括如下步骤:

13、(1)提供硅晶圆,所述硅晶圆包括厚度方向相对的功能面和非功能面,从所述功能面的表面向所述非功能面的方向刻蚀多个硅通孔结构,并使得各硅通孔在所述功能面的表面呈菱形阵列排布;

14、(2)在所述功能面上形成金属布线层,并对所述非功能面进行减薄,直至漏出硅通孔结构;

15、(3)在所述非功能面上设置多个纳米孔,得到第一芯片层;

16、(4)重复步骤(1)至(3)得到第二芯片层将所述第一芯片层的非功能面和所述第二芯片层的功能面对准键合,完成芯片的堆叠。

17、优选地,步骤(1)包括如下子步骤:

18、(11)在所述硅晶圆表面需要刻蚀硅通孔的区域生长掩膜层,利用深度反应离子刻蚀在所述掩膜层上进行刻蚀,形成硅盲孔;

19、(12)向所述硅盲孔内填充聚合物溶液后,依次进行离心和固化将所述聚合物溶液沉积到所述硅盲孔的底部和侧壁,形成第二环形介质层;

20、(13)在所述第二环形介质层中填充聚合物材料,并在填充聚合物材料区域的中心位置和边缘位置分别刻蚀圆柱形通孔和环形通孔,利用自下而上镀铜工艺在所述圆柱形通孔和环形通孔的底部和侧壁内沉积金属铜,分别形成圆柱形导电层和环形导电层;

21、(14)在所述圆柱形导电层的外侧刻蚀两个相对的扇形通孔,分别形成第一扇环介质层和第二扇环介质层,完成硅通孔结构的制备。

22、优选地,在所述步骤(12)中,所述聚合物溶液为聚酰胺酸溶液,所述聚酰胺酸溶液的粘度为1500~3000mp·s;

23、所述离心的转速为3500~4500rpm,离心的时间为25~30s;

24、所述固化的温度为100~300℃,固化时间为1~2h。

25、优选地,在所述步骤(12)中,向所述硅盲孔内填充聚合物溶液后,先将其进行真空处理,再依次进行离心和固化;

26、所述真空处理的真空度为40~50pa,时间为5~10min。

27、优选地,在所述步骤(13)中,在沉积金属铜之前,还包括分别在圆柱形通孔和环形通孔的底部和侧壁上顺序沉积阻挡层和种子层的步骤;所述阻挡层为金属钛或金属钽,所述种子层为金属铜。

28、本发明与现有技术相比至少具有如下有益效果:

29、(1)本发明中,通过在功能面上刻蚀多个硅通孔结构,并使得各硅通孔结构在功能面上呈菱形阵列排布,通过硅通孔结构将第一芯片层和第二芯片层之间进行互连,不仅能够保证第一芯片层和第二芯片层之间的信号传输,而且能够有效防止芯片层中各硅通孔结构之间的热应力叠加,有利于保证芯片的工作的可靠性;

30、(2)本发明中通过在芯片层的非功能面上设置纳米孔结构,纳米孔结构位于硅通孔结构的周围区域,如此能够使得硅通孔结构产生的热量或芯片层间的热量通过散热孔结构进行扩散,从而降低热量对芯片性能的损伤,进一步提高了芯片工作的可靠性;

31、(3)在本发明一些优选的实施方式中,本发明实现了一种新型的硅通孔结构的制备,本发明中通过改变硅通孔结构中圆柱形导电层和环形导电层的内外径比例以及第一环形介质层中聚合物材料的填充角度,能够改变硅通孔结构的阻抗特性,改善带宽,并能够在一定程度上减小硅通孔结构产生的热机械应力。

技术特征:

1.一种芯片的三维堆叠结构,其特征在于,包括:至少两个芯片层;

2.根据权利要求1所述的三维堆叠结构,其特征在于,

3.根据权利要求1所述的三维堆叠结构,其特征在于,

4.根据权利要求3所述的三维堆叠结构,其特征在于,

5.根据权利要求3所述的三维堆叠结构,其特征在于,

6.一种根据权利要求1至5中任一项所述的三维堆叠结构的堆叠方法,其特征在于,所述堆叠方法包括如下步骤:

7.根据权利要求6所述的堆叠方法,其特征在于,步骤(1)包括如下子步骤:

8.根据权利要求7所述的堆叠方法,其特征在于,在步骤(12)中,

9.根据权利要求7所述的堆叠方法,其特征在于,在步骤(12)中,

10.根据权利要求7所述的堆叠方法,其特征在于,在步骤(13)中,

技术总结

本发明提供了一种芯片的三维堆叠结构和堆叠方法,属于芯片封装技术领域,该结构包括:至少两个芯片层;每个芯片层包括功能面和非功能面,功能面上设有多个硅通孔结构,硅通孔结构贯穿每个芯片层的功能面和非功能面,各硅通孔结构在所述功能面上呈菱形阵列排布,功能面上设有金属布线层,硅通孔结构的其中一端与金属布线层相连接;非功能面上设有多个纳米孔,纳米孔用于对每个芯片层进行散热;每个芯片层的功能面上设有焊盘,非功能面上设有键合焊盘,焊盘与功能面上的金属布线层相连接,键合焊盘与非功能面上的硅通孔结构相连接,芯片层中的第一芯片和第二芯片通过焊盘和键合焊盘相连接。本发明能够减小芯片中热应力的累积,增强芯片的散热能力。

技术研发人员:王嘉诚,张少仲,张栩

受保护的技术使用者:中诚华隆计算机技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!