一种具有闸流体抑制层的半导体元件的制作方法

本发明涉及半导体光电器件,具体而言,涉及一种具有闸流体抑制层的半导体元件。

背景技术:

1、半导体元件特别是半导体发光元件具有可调范围广泛的波长范围,发光效率高,节能环保,可使用超过10万小时的长寿命、尺寸小、应用场景多、可设计性强等因素,已逐渐取代白炽灯和荧光灯,成长普通家庭照明的光源,并广泛应用新的场景,如户内高分辨率显示屏、户外显屏、mini-led、micro-led、手机电视背光、背光照明、路灯、汽车大灯、车日行灯、车内氛围灯、手电筒等应用领域。

2、传统氮化物半导体使用蓝宝石衬底生长,晶格失配和热失配大,导致较高的缺陷密度和极化效应,产生非辐射复合中心,降低半导体发光元件的发光效率;同时,传统氮化物半导体的空穴离化效率远低于电子离化效率,导致空穴浓度低于电子浓度2个数量级以上,过量的电子会从多量子阱溢出至第二导电型半导体产生非辐射复合,空穴离化效率低会导致第二导电型半导体的空穴难以有效注入多量子阱中,空穴注入多量子阱的效率低,导致多量子阱的发光效率低;氮化物半导体结构具有非中心对称性,沿c轴方向会产生较强的自发极化,叠加晶格失配的压电极化效应,形成本征极化场;该本征极化场沿(001)方向,使多量子阱层产生较强的量子限制stark效应,引起能带倾斜和电子空穴波函数空间分离,降低电子空穴的辐射复合效率,进而影响半导体发光元件的发光效率。传统氮化物半导体发光元件的缺陷延伸至量子阱,产生深能级缺陷中心,出现pn相互交错产生结间电容形成闸流体,导致发光二极管在使用过程中,导通电压上升,而在二极管点亮之后,电压又出现下降的问题,导致正常与异常芯片的导通电压不一致,在使用过程中产生点亮不致的问题。

技术实现思路

1、本发明的目的在于提供一种具有闸流体抑制层的半导体元件,解决了现有技术中存在的的问题。

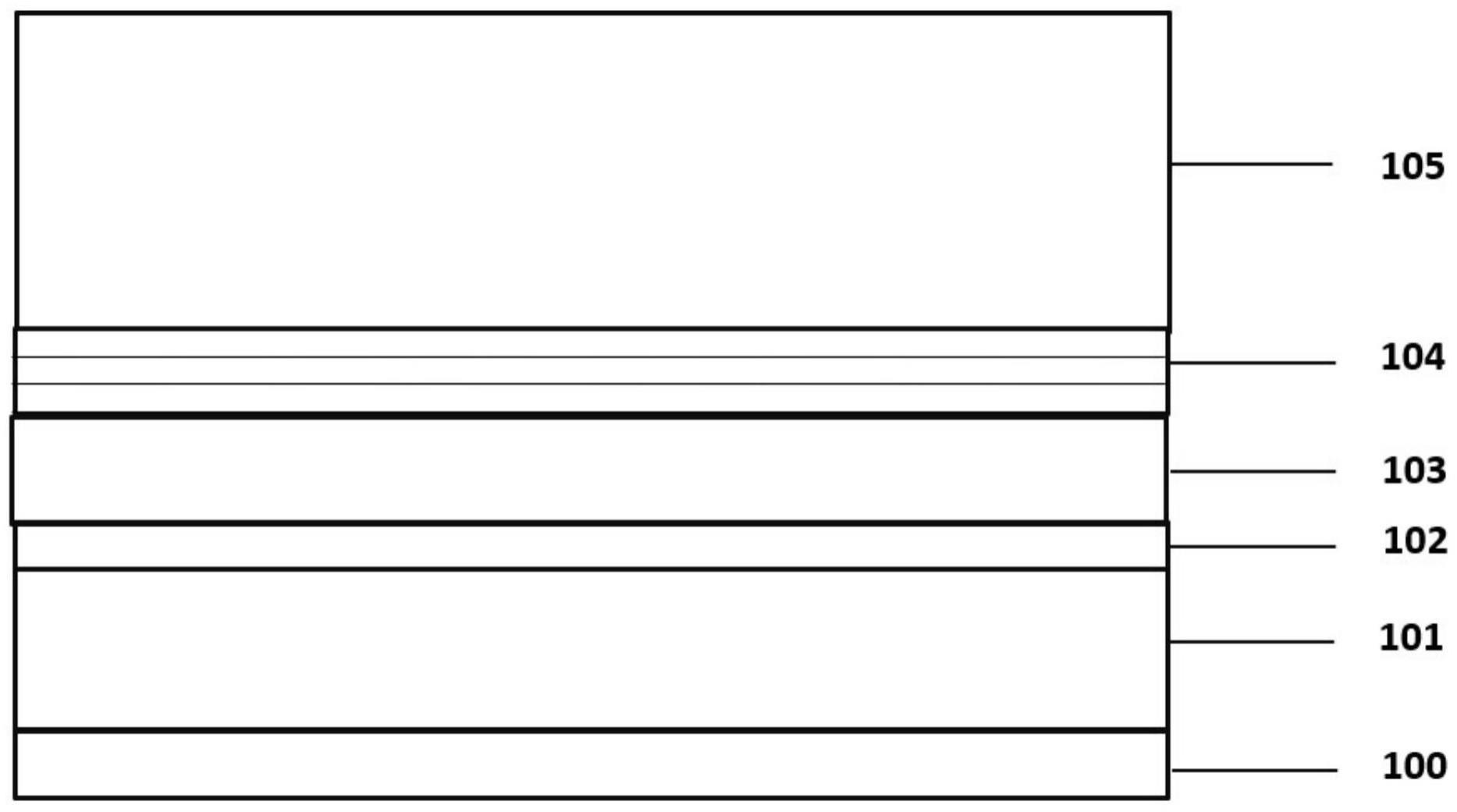

2、一种具有闸流体抑制层的半导体元件,包括从下至上依次设置的衬底、第一n型半导体层、第二n型半导体层、闸流体抑制层、量子阱层和p型半导体层。

3、作为本发明优选的技术方案,所述闸流体抑制层由第一闸流体抑制层、第二闸流体抑制层和第三闸流体抑制层自下而上组成。

4、作为本发明优选的技术方案,所述第二闸流体抑制层往第一闸流体抑制层的c含量呈双台阶下降趋势,包含第一c含量下降台阶和第二c含量下降台阶;所述第一c含量下降台阶角度为α:60°≥α≥15°,第二c含量下降台阶角度为β:90°≥β≥30°。

5、作为本发明优选的技术方案,所述第二闸流体抑制层往第三闸流体抑制层的c含量呈双台阶下降趋势,包含第三c含量下降台阶和第四c含量下降台阶;所述第三c含量下降台阶角度为γ:80°≥γ≥20°,第四c含量下降台阶角度为θ:90°≥θ≥30°。

6、作为本发明优选的技术方案,所述第二c含量下降台阶角度β≥第四c含量下降台阶角度θ≥第三c含量下降台阶角度γ≥第一c含量下降台阶角度α。

7、作为本发明优选的技术方案,所述第二闸流体抑制层的c含量浓度保持恒定,c含量浓度为1e17~5e18cm-3;所述第二闸流体抑制层的si掺杂浓度保持恒定为5e17~5e18cm-3,所述第一闸流体抑制层的si掺杂浓度呈山峰状,峰值si掺浓度为1e18~2e19cm-3,所述第三闸流体抑制层的si掺杂浓度呈山峰状,峰值si掺浓度为8e17~5e18cm-3;所述第一闸流体抑制层、第二闸流体抑制层和第三闸流体抑制层的si掺杂浓度大于c含量浓度。

8、进一步地,所述第二闸流体抑制层往第一闸流体抑制层的c含量呈双台阶下降趋势,包含第一c含量下降台阶和第二c含量下降台阶,第一c含量下降台阶的c含量浓度从5e17~5e18cm-3下降1e17~5e17cm-3,第二c含量下降台阶的c含量浓度从1e17~5e17cm-3下降至1e16~1e17cm-3;所述第二闸流体抑制层往第三闸流体抑制层的c含量呈双台阶下降趋势,包含第三c含量下降台阶和第四c含量下降台阶,第三c含量下降台阶的c含量浓度从5e17~5e18cm-3下降1e17~5e17cm-3,第四c含量下降台阶的c含量浓度从1e17~5e17cm-3下降至1e16~1e17cm-3。

9、作为本发明优选的技术方案,所述第一闸流体抑制层、第二闸流体抑制层和第三闸流体抑制层的h含量保持恒定,h含量浓度为1e17~1e18cm-3,所述第一闸流体抑制层103a、第二闸流体抑制层和第三闸流体抑制层103c的o含量保持恒定,o含量浓度为1e16~17e17cm-3。

10、作为本发明优选的技术方案,第一n型半导体层、第二n型半导体层、闸流体抑制层、量子阱层、和p型半导体层为gan、algan、ingan、alingan、aln、inn、alinn的任意一种或任意组合。

11、作为本发明优选的技术方案,所述量子阱层为由阱层和垒层组成的周期结构,所述量子阱层的周期数为x:5≤x≤20,所述量子阱层的阱层厚度为a:20埃米≤a≤60埃米,所述量子阱层104的垒层厚度b:20埃米≤b≤150埃米。

12、与现有技术相比,本发明的有益效果:

13、在本发明的方案中:

14、相比于现有技术,本发明通过设计闸流体抑制层,在闸流体抑制层中设计三层不同c含量浓度、c含量呈双台阶下降趋势以及si掺杂浓度、h含量浓度和o含量浓度的半导体结构结合,抑制深能级缺陷中心,抑制pn相互交错产生结间电容,使闸流体的产生概率从1~5%比例下降至0,解决半导体发光元件使用过程中产生点亮不一致问题。

技术特征:

1.一种具有闸流体抑制层的半导体元件,其特征在于,包括从下至上依次设置的衬底(100)、第一n型半导体层(101)、第二n型半导体层(102)、闸流体抑制层(103)、量子阱层(104)和p型半导体层(105)。

2.根据权利要求(1)所述的具有闸流体抑制层的半导体元件,其特征在于,所述闸流体抑制层(103)由第一闸流体抑制层(103a)、第二闸流体抑制层(103b)和第三闸流体抑制层(103c)自下而上组成。

3.根据权利要求2所述的具有闸流体抑制层的半导体元件,其特征在于,所述第二闸流体抑制层(103b)往第一闸流体抑制层(103a)的c含量呈双台阶下降趋势,包含第一c含量下降台阶和第二c含量下降台阶;所述第一c含量下降台阶角度为α:60°≥α≥15°,第二c含量下降台阶角度为β:90°≥β≥30°。

4.根据权利要求2所述的具有闸流体抑制层的半导体元件,其特征在于,所述第二闸流体抑制层(103b)往第三闸流体抑制层(103c)的c含量呈双台阶下降趋势,包含第三c含量下降台阶和第四c含量下降台阶;所述第三c含量下降台阶角度为γ:80°≥γ≥20°,第四c含量下降台阶角度为θ:90°≥θ≥30°。

5.根据权利要求4所述的具有闸流体抑制层的半导体元件,其特征在于,所述第二c含量下降台阶角度β≥第四c含量下降台阶角度θ≥第三c含量下降台阶角度γ≥第一c含量下降台阶角度α。

6.根据权利要求5所述的具有闸流体抑制层的半导体元件,其特征在于,所述第二闸流体抑制层(103b)的c含量浓度保持恒定,c含量浓度为1e17~5e18cm-3;所述第二闸流体抑制层(103b)的si掺杂浓度保持恒定为5e17~5e18cm-3,所述第一闸流体抑制层(103a)的si掺杂浓度呈山峰状,峰值si掺浓度为1e18~2e19cm-3,所述第三闸流体抑制层(103c)的si掺杂浓度呈山峰状,峰值si掺浓度为8e17~5e18cm-3;所述第一闸流体抑制层(103a)、第二闸流体抑制层(103b)和第三闸流体抑制层(103c)的si掺杂浓度大于c含量浓度。

7.根据权利要求6所述的具有闸流体抑制层的半导体元件,其特征在于,所述第二闸流体抑制层(103b)往第一闸流体抑制层(103a)的c含量呈双台阶下降趋势,包含第一c含量下降台阶和第二c含量下降台阶,第一c含量下降台阶的c含量浓度从5e17~5e18cm-3下降1e17~5e17cm-3,第二c含量下降台阶的c含量浓度从1e17~5e17cm-3下降至1e16~1e17cm-3;所述第二闸流体抑制层(103b)往第三闸流体抑制层(103c)的c含量呈双台阶下降趋势,包含第三c含量下降台阶和第四c含量下降台阶,第三c含量下降台阶的c含量浓度从5e17~5e18cm-3下降1e17~5e17cm-3,第四c含量下降台阶的c含量浓度从1e17~5e17cm-3下降至1e16~1e17cm-3。

8.根据权利要求2所述的具有闸流体抑制层的半导体元件,其特征在于,所述第一闸流体抑制层(103a)、第二闸流体抑制层(103b)和第三闸流体抑制层(103c)的h含量保持恒定,h含量浓度为1e17~1e18cm-3,所述第一闸流体抑制层(103a)、第二闸流体抑制层(103b)和第三闸流体抑制层(103c)的o含量保持恒定,o含量浓度为1e16~17e17cm-3。

9.根据权利要求1所述的具有闸流体抑制层的半导体元件,其特征在于,第一n型半导体层(101)、第二n型半导体层(102)、闸流体抑制层(103)、量子阱层(104)和p型半导体层(105)为gan、algan、ingan、alingan、aln、inn、alinn的任意一种或任意组合。

10.根据权利要求1所述的具有闸流体抑制层的半导体元件,其特征在于,所述量子阱层(104)为由阱层和垒层组成的周期结构,所述量子阱层(104)的周期数为x:5≤x≤20,所述量子阱层(104)的阱层厚度为a:20埃米≤a≤60埃米,所述量子阱层(104)的垒层厚度b:20埃米≤b≤150埃米。

技术总结

本发明提供了一种具有闸流体抑制层的半导体元件,涉及半导体光电器件技术领域,包括从下至上依次设置的衬底、第一n型半导体层、第二n型半导体层、闸流体抑制层、量子阱层和p型半导体层;所述闸流体抑制层由第一闸流体抑制层、第二闸流体抑制层和第三闸流体抑制层自下而上组成;通过插入闸流体抑制层,在闸流体抑制层中设计三层不同C含量浓度、C含量呈双台阶下降趋势以及Si掺杂浓度、H含量浓度和O含量浓度的半导体结构结合,抑制深能级缺陷中心,抑制PN相互交错产生结间电容,使闸流体的产生概率从1~5%比例下降至0,解决半导体发光元件使用过程中产生点亮不一致问题。

技术研发人员:张江勇,王星河,李水清,蔡鑫,陈婉君,刘紫涵,胡志勇,张会康,请求不公布姓名

受保护的技术使用者:安徽格恩半导体有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!