具有应力降低特征的化合物半导体基装置的制作方法

本申请涉及半导体装置制造及集成电路,尤其涉及包括化合物半导体基装置的结构以及形成此类结构的方法。

背景技术:

1、化合物半导体基装置(例如高电子迁移率晶体管)可被部署于高压功率电子装置中。化合物半导体的特征在于可以利用的材料属性,例如载流子迁移率大于硅的载流子迁移率,以及与硅相比较宽的带隙。化合物半导体可包括第iii族元素(例如,铝、镓,及/或铟)以及与第iii族元素组合的第v族元素(例如,氮、磷、砷,及/或锑)。用于构造化合物半导体基装置的常见宽带隙化合物半导体是氮化镓。高电子迁移率晶体管可包括具有不同带隙的晶体化合物半导体材料之间的异质结,例如二元氮化镓与三元氮化铝镓之间的异质结。在操作期间,二维电子气形成于该异质结处的界面附近,并定义该高电子迁移率晶体管的沟道。

2、化合物半导体基装置可包括在衬底上通过异质外延生长的化合物半导体层堆叠。该些层经优化以管理由例如该衬底与位于该衬底上的该外延化合物半导体层之间的热膨胀系数的不同而引起的应力。由于热膨胀系数的不同及其它应力,在后续制程期间的热步骤可能导致开裂及/或断裂。

3、需要改进的包括第iii-v族化合物半导体基装置的结构以及形成此类结构的方法。

技术实现思路

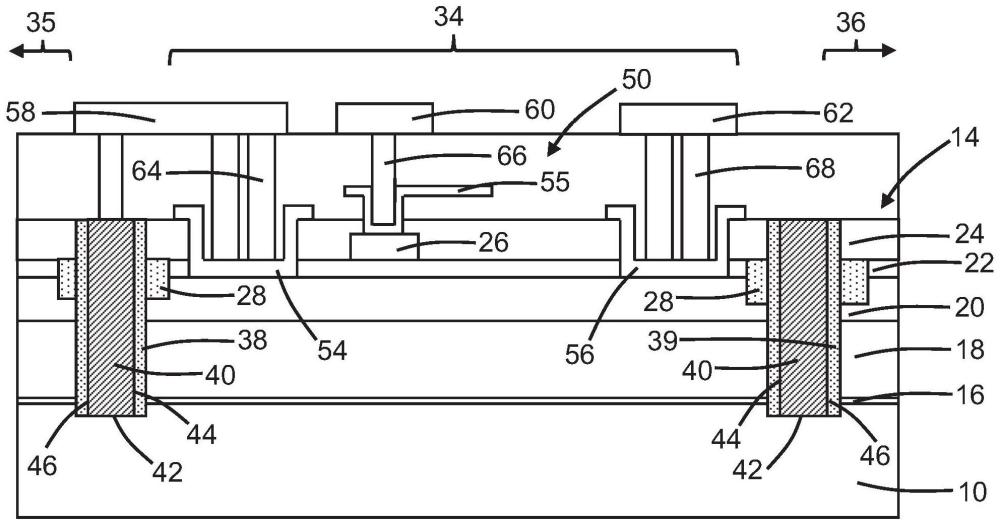

1、在本发明的一个实施例中,一种结构包括位于衬底上的层堆叠,沿垂直方向完全穿过该层堆叠延伸至该衬底的导电接触,以及包括源极欧姆接触及漏极欧姆接触的装置结构。该层堆叠包括多个半导体层,各半导体层包括化合物半导体材料,该导电接触布置于该层堆叠中,以将该层堆叠的第一部分与该层堆叠的第二部分隔开,以及该源极欧姆接触及该漏极欧姆接触与该层堆叠的该第一部分的该多个半导体层的至少其中之一具有接触关系。

2、在本发明的一个实施例中,一种方法包括在衬底上形成层堆叠,形成沿垂直方向完全穿过该层堆叠延伸至该衬底的导电接触,以及形成包括源极欧姆接触及漏极欧姆接触的装置结构。该层堆叠包括多个半导体层,各半导体层包括化合物半导体材料,该导电接触布置于该层堆叠中,以将该层堆叠的第一部分与该层堆叠的第二部分隔开,以及该源极欧姆接触及该漏极欧姆接触与该层堆叠的该第一部分的该多个半导体层的至少其中之一呈接触关系。

技术特征:

1.一种结构,其特征在于,包括:

2.如权利要求1所述的结构,其特征在于,该导电接触完全围绕该层堆叠的该第一部分。

3.如权利要求1所述的结构,其特征在于,该导电接触沿横向方向设置于该层堆叠的该第一部分与该层堆叠的该第二部分间作为隔件。

4.如权利要求1所述的结构,其特征在于,该装置结构为高电子迁移率晶体管,其包括位于该层堆叠的该第一部分上的栅极。

5.如权利要求1所述的结构,其特征在于,该衬底包括重掺杂半导体材料。

6.如权利要求1所述的结构,其特征在于,该多个半导体层的至少其中之一的该化合物半导体材料包括氮化镓。

7.如权利要求1所述的结构,其特征在于,还包括:

8.如权利要求7所述的结构,其特征在于,该导电接触形成于穿过该介电层及该层堆叠至该衬底的沟槽中,该沟槽具有内侧壁及外侧壁,且还包括:

9.如权利要求1所述的结构,其特征在于,该导电接触具有与该衬底直接接触的端部。

10.如权利要求1所述的结构,其特征在于,该导电接触包括钨。

11.如权利要求1所述的结构,其特征在于,该导电接触包括掺杂多晶硅。

12.如权利要求1所述的结构,其特征在于,该导电接触形成于穿过该层堆叠至该衬底的沟槽中,该沟槽具有内侧壁及外侧壁,且还包括:

13.如权利要求12所述的结构,其特征在于,该导电接触、该第一介电间隔件,以及该第二介电间隔件完全围绕该层堆叠的该第一部分。

14.如权利要求12所述的结构,其特征在于,该导电接触、该第一介电间隔件,以及该第二介电间隔件沿横向方向设置于该层堆叠的该第一部分与该层堆叠的该第二部分间作为隔件。

15.如权利要求1所述的结构,其特征在于,还包括:

16.如权利要求15所述的结构,其特征在于,该导电接触及该隔离区完全围绕该层堆叠的该第一部分。

17.如权利要求15所述的结构,其特征在于,该导电接触及该隔离区沿横向方向设置于该层堆叠的该第一部分与该层堆叠的该第二部分间作为隔件。

18.一种方法,其特征在于,包括:

19.如权利要求18所述的方法,其特征在于,该导电接触形成于穿过该层堆叠至该衬底的沟槽中,该沟槽具有内侧壁及外侧壁,且还包括:

20.如权利要求18所述的方法,其特征在于,该导电接触形成于穿过该层堆叠至该衬底的沟槽中,且在形成该装置结构前形成该沟槽。

技术总结

本发明涉及具有应力降低特征的化合物半导体基装置,提供包括集成于半导体衬底上的化合物半导体基装置及硅基装置的结构以及形成此类结构的方法。该结构包括位于衬底上的层堆叠、沿垂直方向完全穿过该层堆叠延伸至该衬底的导电接触,以及包括源极欧姆接触及漏极欧姆接触的装置结构。该层堆叠包括多个半导体层,各半导体层包括化合物半导体材料,该导电接触布置于该层堆叠中,以将该层堆叠的第一部分与该层堆叠的第二部分隔开,以及该源极欧姆接触及该漏极欧姆接触与该层堆叠的该第一部分的该多个半导体层的至少其中之一具有接触关系。

技术研发人员:L·S·素赛,H·利内威赫,F·赫伯特,H·马里奥,S·L·奇瓦

受保护的技术使用者:新加坡商格罗方德半导体私人有限公司

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!