本发明属于集成电路,具体涉及一种低关断电流芯片输出管脚保护电路。

背景技术:

1、随着电子设备的发展,芯片在电子设备中的应用越来越广泛。在电路设计中,芯片的输出管脚是连接芯片与其他电路元件之间的重要接口。然而,在某些情况下,如电源电压波动、信号干扰、过载等,输出管脚可能会受到过压或负压的影响,导致芯片受损或无法正常工作。

2、过压是指输出管脚电压高于芯片规格中所指定的最大值。当输出管脚电压受外界影响超过芯片规格时,芯片可能会因为过载而受损,导致设备无法正常工作,甚至出现严重的事故。负压则是指输出管脚电压低于零电压的情况。这可能会导致芯片内部器件出现反向偏置,损坏芯片。

3、现阶段,实现芯片输出管脚保护通常采用过压保护二极管或串联限流电阻的方法。现有的两种方法都有它们的局限性。在过压保护二极管方案中,只能选择对过压或负压的一种进行保护,而不能实现双向保护。而且,由于二极管导通时存在压降,这种方案不适用模拟输出管脚的保护。在串联限流电阻方案中,具体保护电压的高低由串联电阻的阻值决定。由于在正常工作时,当串联电阻后所接电路不是高阻时,在此串联电阻上会有压降,因此这种方法不适用于模拟管脚输出或有上拉或下拉电阻的数字通信应用。同时,这两种方案所提供的保护电压值都不够精确,保护时仍然有较大的电流流过芯片输出管脚,时间较长仍会使管脚器件损坏。

技术实现思路

1、为此,本发明提供一种低关断电流芯片输出管脚保护电路,以有效保护芯片免受过压和负压的损害,提高电子设备的可靠性和稳定性。

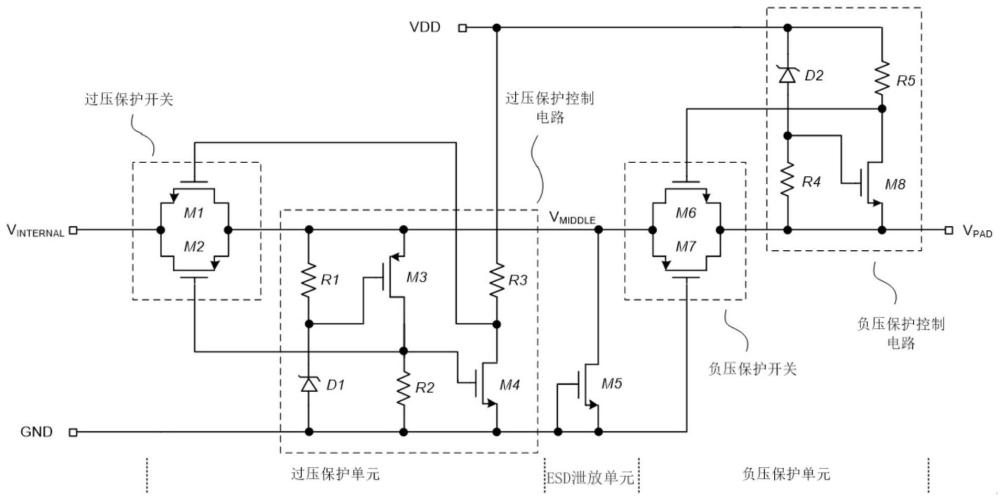

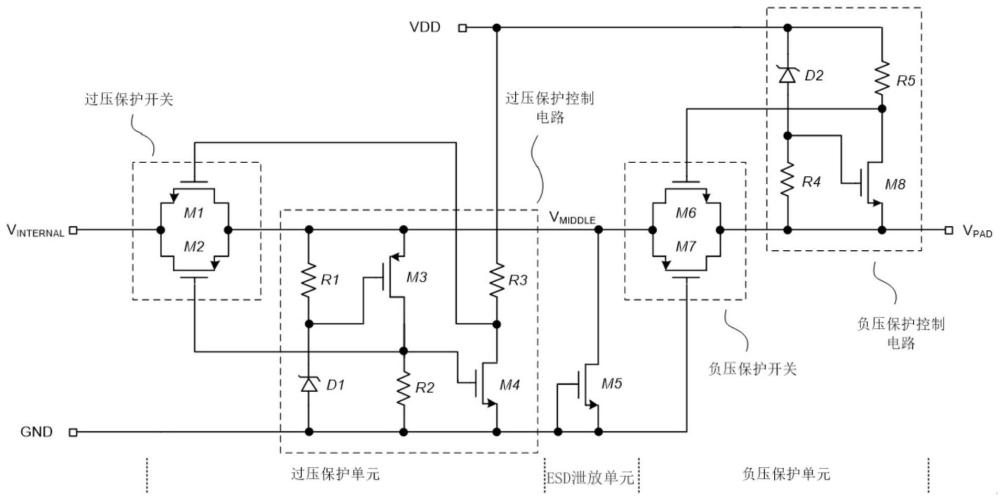

2、为了实现上述目的,本发明提供如下技术方案:一种低关断电流芯片输出管脚保护电路,包括过压保护单元、负压保护单元和esd泄放单元,还包括电源端vdd、信号输入端vinternal、芯片管脚端vpad和接地端gnd

3、所述过压保护单元包括过压保护开关和过压保护控制电路;所述负压保护单元包括负压保护开关和负压保护控制电路;

4、所述芯片管脚端vpad电压位于所述电源端vdd电压和所述接地端gnd电压之间,所述过压保护开关和所述负压保护开关处于导通状态,所述信号输入端vinternal信号被输出到所述芯片管脚端vpad,所述芯片管脚端vpad上释放的静电利用所述过压保护开关和所述esd泄放单元泄放所述接地端gnd;

5、当所述芯片管脚端vpad电压被拉高大于所述电源端vdd电压时,所述过压保护单元的所述过压保护开关关断;

6、当所述芯片管脚端vpad电压被拉低小于所述接地端gnd电压时,所述负压保护单元的所述负压保护开关关断。

7、作为低关断电流芯片输出管脚保护电路优选方案,所述过压保护单元的一端与所述信号输入端vinterna电连接,所述过压保护单元的另外一端和所述负压保护单元电连接,所述过压保护单元的另外一端还和所述esd泄放单元电连接,所述负压保护单元和所述芯片管脚端vpad电连接,所述esd泄放单元和所述接地端gnd电连接。

8、作为低关断电流芯片输出管脚保护电路优选方案,所述过压保护开关包括pmos管m2、nmos管m1;所述过压保护控制电路包括稳压二极管d1、电阻r1、电阻r2、电阻r3、pmos管m3和nmos管m4;

9、pmos管m2的栅极与pmos管m3的漏极相连,pmos管m2的源极与节点vmiddle相连,pmos管m2的漏极与所述信号输入端vinternal相连;nmos管m1的栅极与电阻r3的负极相连,nmos管m1的栅极还与nmos管m4的漏极相连,nmos管m1的源极与所述信号输入端vinternal相连,nmos管m1的漏极与节点vmiddle相连;

10、稳压二极管d1的阳极与所述接地端gnd相连,稳压二极管d1的阴极与电阻r1负极相连,稳压二极管d1的阴极还与pmos管m3的栅极相连,电阻r1的正极与节点vmiddle相连;

11、pmos管m3的源极与节点vmiddle相连,pmos管m3的漏极与电阻r2的正极相连;电阻r2的负极与所述接地端gnd相连;

12、电阻r3的正极与电源vdd相连,电阻r3的负极与nmos管m4的漏极相连;nmos管m4的栅极与电阻r2的正极相连,nmos管m4的源极与接地端gnd相连。

13、作为低关断电流芯片输出管脚保护电路优选方案,所述esd泄放单元包括nmos管m5,nmos管m5的栅极与接地端gnd相连,nmos管m5的源极与接地端gnd相连,nmos管m5的漏极与节点vmiddle相连。

14、作为低关断电流芯片输出管脚保护电路优选方案,所述负压保护开关包括pmos管m7和nmos管m6;所述负压保护控制电路包括稳压二极管d2、电阻r4、电阻r5和nmos管m8;

15、pmos管m7的栅极与接地端gnd相连,pmos管m7的源极与节点vmiddle相连,pmos管m7的漏极与芯片管脚端vpad相连;

16、nmos管m6的栅极与电阻r5的负极相连,nmos管m6的栅极还与nmos管m8的漏极相连,nmos管m6的源极与芯片管脚端vpad相连,nmos管m6的漏极与节点vmiddle相连;

17、稳压二极管d2的阳极与电阻r4的正极相连,稳压二极管d2的阳极还与nmos管m8的栅极相连;稳压二极管d2的阴极与电源端vdd相连;

18、电阻r4的正极与稳压二极管d2的阴极相连,电阻r4的负极与芯片管脚端vpad相连,电阻r4的负极还与nmos管m8的源极相连;

19、电阻r5的正极与电源端vdd相连,电阻r5的负极还与nmos管m8的漏极相连;nmos管m8的源极与芯片管脚端vpad相连。

20、本发明具有如下有益效果,过压保护单元包括过压保护开关和过压保护控制电路;负压保护单元包括负压保护开关和负压保护控制电路;芯片管脚端vpad电压位于电源端vdd电压和接地端gnd电压之间,过压保护开关和负压保护开关处于导通状态,信号输入端vinternal信号被输出到芯片管脚端vpad,芯片管脚端vpad上释放的静电利用过压保护开关和esd泄放单元泄放接地端gnd;当芯片管脚端vpad电压被拉高大于电源端vdd电压时,过压保护单元的过压保护开关关断;当芯片管脚端vpad电压被拉低小于接地端gnd电压时,负压保护单元的负压保护开关关断。本发明实现了在芯片输出管脚电压过高或反接时对芯片内部电路的保护,正常工作时仅增加几微安的电流,并且关断时关断电流很小,可以有效保护芯片免受过压和负压的损害,提高电子设备的可靠性和稳定性。

技术特征:1.一种低关断电流芯片输出管脚保护电路,其特征在于,包括过压保护单元、负压保护单元和esd泄放单元,还包括电源端vdd、信号输入端vinternal、芯片管脚端vpad和接地端gnd

2.根据权利要求1所述的一种低关断电流芯片输出管脚保护电路,其特征在于,所述过压保护单元的一端与所述信号输入端vinterna电连接,所述过压保护单元的另外一端和所述负压保护单元电连接,所述过压保护单元的另外一端还和所述esd泄放单元电连接,所述负压保护单元和所述芯片管脚端vpad电连接,所述esd泄放单元和所述接地端gnd电连接。

3.根据权利要求2所述的一种低关断电流芯片输出管脚保护电路,其特征在于,所述过压保护开关包括pmos管m2、nmos管m1;所述过压保护控制电路包括稳压二极管d1、电阻r1、电阻r2、电阻r3、pmos管m3和nmos管m4;

4.根据权利要求3所述的一种低关断电流芯片输出管脚保护电路,其特征在于,所述esd泄放单元包括nmos管m5,nmos管m5的栅极与接地端gnd相连,nmos管m5的源极与接地端gnd相连,nmos管m5的漏极与节点vmiddle相连。

5.根据权利要求4所述的一种低关断电流芯片输出管脚保护电路,其特征在于,所述负压保护开关包括pmos管m7和nmos管m6;所述负压保护控制电路包括稳压二极管d2、电阻r4、电阻r5和nmos管m8;

技术总结一种低关断电流芯片输出管脚保护电路,包括过压保护单元、负压保护单元和ESD泄放单元;芯片管脚端V<subgt;PAD</subgt;电压位于电源端VDD电压和接地端GND电压之间,过压保护开关和负压保护开关处于导通状态,信号输入端V<subgt;INTERNAL</subgt;信号被输出到芯片管脚端V<subgt;PAD</subgt;,芯片管脚端V<subgt;PAD</subgt;上释放的静电利用过压保护开关和ESD泄放单元泄放接地端GND;当芯片管脚端V<subgt;PAD</subgt;电压被拉高大于电源端VDD电压时,过压保护单元的过压保护开关关断;当芯片管脚端V<subgt;PAD</subgt;电压被拉低小于接地端GND电压时,负压保护单元的负压保护开关关断。本发明有效保护芯片免受过压和负压的损害,提高电子设备可靠性和稳定性。

技术研发人员:江山,黄小振

受保护的技术使用者:上海芯攀微电子科技有限公司

技术研发日:技术公布日:2024/4/17