一种高电流均匀性VDMOS器件的制造方法与流程

本发明涉及半导体功率器件,特别涉及一种高电流均匀性vdmos器件的制造方法。

背景技术:

1、vdmos产品因其工艺流程简单,对工艺线的能力要求不高等优点,应用领域在不断扩大,随之而来的业界对产品各项要求也越来越高。

2、目前vdmos主要应用在中高电压档位,某些应用场景要求vdmos具有较强的过电流能力与抗动态雪崩能力。在目前的工艺条件下,由于光刻精度有限,接触孔光刻存在套偏问题,接触孔覆盖两侧的源极长度不一致,导致电流密度不均匀,从而影响vdmos器件的过大电流能力与可靠性;而且接触孔光刻套偏不受控制,不同批次间的vdmos器件良率与参数一致性也会受到影响。

技术实现思路

1、本发明的目的在于提供一种高电流均匀性vdmos器件的制造方法,以解决目前工艺在接触孔光刻存在套偏,导致接触孔不能居中覆盖两侧源极区域的问题。

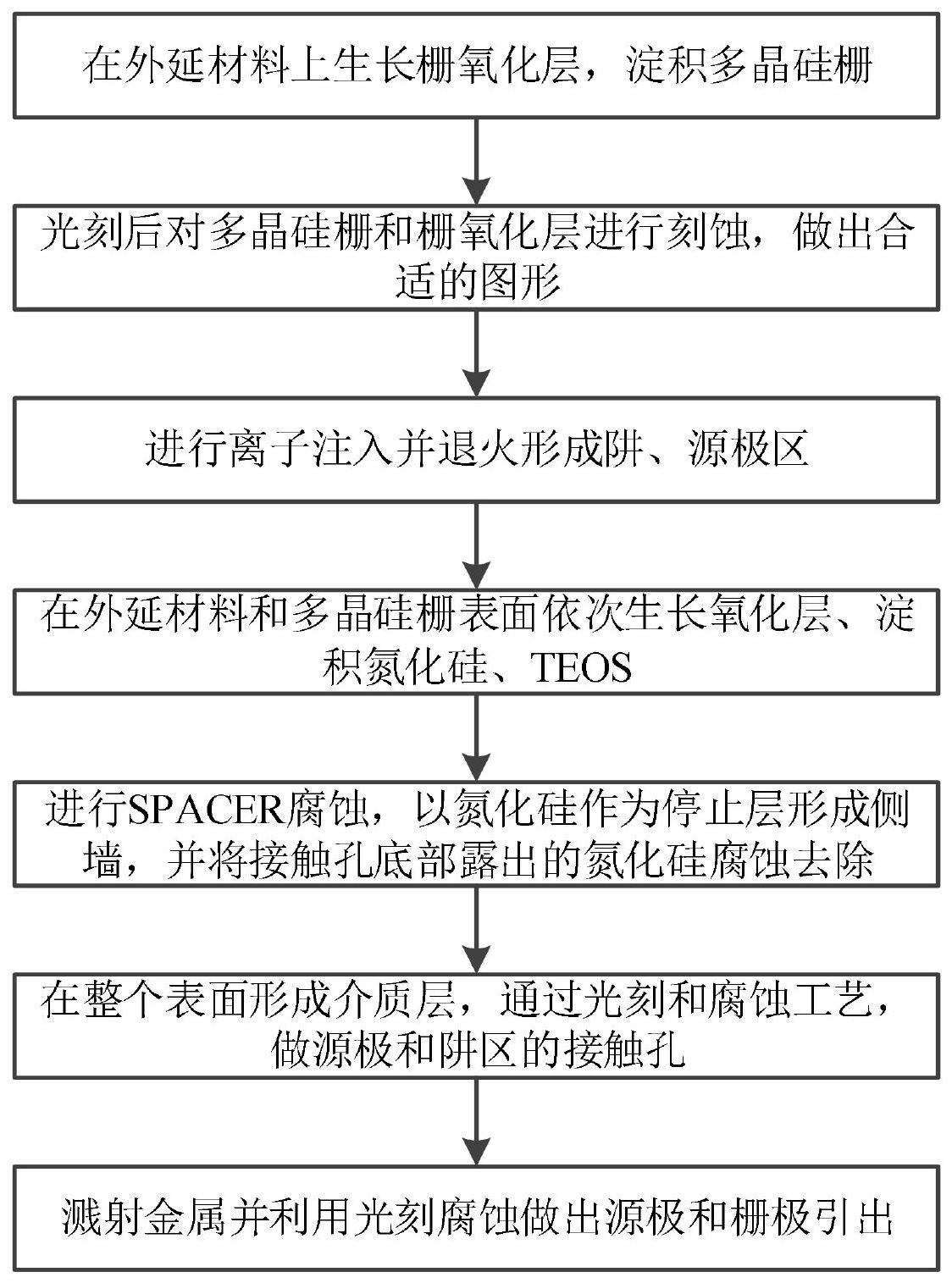

2、为解决上述技术问题,本发明提供了一种高电流均匀性vdmos器件的制造方法,包括:

3、在外延材料上生长栅氧化层,淀积多晶硅栅;

4、光刻后对多晶硅栅和栅氧化层进行刻蚀,做出合适的图形;

5、进行离子注入并退火形成阱、源极区;

6、在外延材料和多晶硅栅表面依次生长氧化层、淀积氮化硅、teos;

7、进行spacer腐蚀,以氮化硅作为停止层形成侧墙,并将接触孔底部露出的氮化硅腐蚀去除;

8、在整个表面形成介质层,通过光刻和腐蚀工艺,做源极和阱区的接触孔;

9、溅射金属并利用光刻腐蚀做出源极和栅极引出。

10、在一种实施方式中,在溅射金属并利用光刻腐蚀做出源极和栅极引出之后,该制造方法还包括:在器件整体淀积钝化介质,并光刻腐蚀,除栅极和源极需要打线引出的区域外,其他区域覆盖上钝化层。

11、在一种实施方式中,进行离子注入并退火形成阱、源极区包括:生长氧化层作为阻挡层,注入的离子能量为20kev~200kev,退火激活的温度为800℃~1200℃;在形成阱、源极区后再腐蚀去除该阻挡层。

12、在一种实施方式中,所述栅氧化层为通过干法氧化或湿法氧化形成的sio2材料,其厚度为所述多晶硅栅的厚度为

13、在一种实施方式中,所述薄氧化层的厚度为所述氮化硅的厚度为所述teos的厚度为

14、在一种实施方式中,所述栅氧化层和多晶硅栅两侧的侧墙左右对称。

15、在一种实施方式中,所述介质层由依次淀积的usg、bpsg、teos共同形成;所述介质层完全包覆形成的侧墙、薄氧化层、以及多晶硅栅和栅氧化层。

16、在一种实施方式中,所述金属完全包覆整个器件的表面,其中金属是ti+tin+alsicu的合金。

17、本发明提供的一种高电流均匀性vdmos器件的制造方法,在栅氧化层和多晶硅栅光刻腐蚀后,依次进行多晶硅氧化,淀积氮化硅和teos,然后进行spacer刻蚀,对接触孔底部氮化硅进行刻蚀,淀积介质层后进行接触孔光刻腐蚀,最后溅射金属完成栅和源极引出。本发明利用spacer腐蚀,形成左右两边对称的侧墙结构,并以此来定义接触孔的位置,保证接触孔能对称覆盖两侧的源极区域,避免光刻精度不足引起的接触孔左右偏移,从而优化了vdmos器件的电流均匀性和可靠性。

技术特征:

1.一种高电流均匀性vdmos器件的制造方法,其特征在于,包括:

2.如权利要求1所述的高电流均匀性vdmos器件的制造方法,其特征在于,在溅射金属并利用光刻腐蚀做出源极和栅极引出之后,该制造方法还包括:在器件整体淀积钝化介质,并光刻腐蚀,除栅极和源极需要打线引出的区域外,其他区域覆盖上钝化层。

3.如权利要求1所述的高电流均匀性vdmos器件的制造方法,其特征在于,进行离子注入并退火形成阱、源极区包括:生长氧化层作为阻挡层,注入的离子能量为20kev~200kev,退火激活的温度为800℃~1200℃;在形成阱、源极区后再腐蚀去除该阻挡层。

4.如权利要求1所述的高电流均匀性vdmos器件的制造方法,其特征在于,所述栅氧化层为通过干法氧化或湿法氧化形成的sio2材料,其厚度为所述多晶硅栅的厚度为

5.如权利要求1所述的高电流均匀性vdmos器件的制造方法,其特征在于,所述薄氧化层的厚度为所述氮化硅的厚度为所述teos的厚度为

6.如权利要求1所述的高电流均匀性vdmos器件的制造方法,其特征在于,所述栅氧化层和多晶硅栅两侧的侧墙左右对称。

7.如权利要求1所述的高电流均匀性vdmos器件的制造方法,其特征在于,所述介质层由依次淀积的usg、bpsg、teos共同形成;所述介质层完全包覆形成的侧墙、薄氧化层、以及多晶硅栅和栅氧化层。

8.如权利要求1所述的高电流均匀性vdmos器件的制造方法,其特征在于,所述金属完全包覆整个器件的表面,其中金属是ti+tin+alsicu的合金。

技术总结

本发明公开一种高电流均匀性VDMOS器件的制造方法,属于半导体功率器件领域。在外延材料上生长栅氧化层,淀积多晶硅栅;光刻后对多晶硅栅和栅氧化层进行刻蚀,做出合适的图形;进行离子注入并退火形成阱、源极区;在表面依次生长氧化层、淀积氮化硅、TEOS;进行SPACER腐蚀,以氮化硅作为停止层形成侧墙,并将接触孔底部露出的氮化硅腐蚀去除;在表面形成介质层,通过光刻和腐蚀工艺,做源极和阱区的接触孔;溅射金属并利用光刻腐蚀做出源极和栅极引出。本发明利用SPACER腐蚀,形成左右两边对称的侧墙结构,以此来定义接触孔的位置,保证接触孔能对称覆盖两侧的源极区域,避免光刻精度不足引起的接触孔左右偏移,从而优化了VDMOS器件的电流均匀性和可靠性。

技术研发人员:唐新宇,洪根深,谢儒彬,张庆东,徐海铭,廖远宝

受保护的技术使用者:中国电子科技集团公司第五十八研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!