菱形的晶片级芯片尺寸封装的制作方法

背景技术:

1、本公开涉及菱形的晶片级芯片尺寸封装。更具体地,本公开涉及一种菱形的晶片级芯片尺寸封装,其与以往矩形或正方形芯片封装相比,芯片大小可以减小约5%至12%,使用以往的半导体制造装备便可制作。

2、最近,随着诸如手机的便携电子设备的迅速发展,电子设备间的融合和复合化正在快速进行。例如手机,在照相机功能、mp3播放功能、dmb功能等多样功能日益复杂的同时还升级为高性能。

3、但是,便携电子设备为了容易携带而需要小巧、轻便,但这与如前所述的多功能化和复合化矛盾。即,便携电子设备的大小随着多功能化和复合化的进行而必然增加。在该问题的解决方案中,部件的小型化会对解决方案提供很大帮助。

4、芯片尺寸封装(csp)是指其大小为半导体芯片大小的约1.2倍的封装。

5、在通常的芯片尺寸封装制造方法中,将通过半导体工序完成的晶片切割成单个半导体芯片后对单个半导体芯片进行封装。随着部件的小型化和大量生产趋势,晶片级芯片尺寸封装(wlcsp)登场。

6、晶片级芯片尺寸封装是为了对电路进行再分配,通过在晶片状态下执行封装工序或执行倒装芯片凸点以完成封装结构后进行切割,从而完成封装。因此,晶片级芯片尺寸封装为小型,与半导体芯片的大小几乎相同,所有封装工序在晶片级上执行,能够实现量产,从而可以节省制造费用。

7、另一方面,根据以往技术,应用的方法是在矩形或四边形半导体芯片的一面上排列焊球后,将焊球连接于印刷电路基板,因而存在的问题是在减小半导体芯片大小方面存在局限。

8、下面参照图1和图2,详细描述这种问题。

9、图1是示例性示出以往技术的正方形晶片级芯片尺寸封装的图,图2是示例性示出以往技术的构成正方形晶片级芯片尺寸封装的焊球阵列的具体的、示例性排列的图。

10、参照图1和图2,以往技术的晶片级芯片尺寸封装1具有在正方形或矩形形态半导体芯片2的一面形成有焊球阵列3的结构,所述焊球阵列3由连接并排列于印刷电路基板的焊球构成。在相应附图中示出了16个焊球,但这只是作为一个示例而提示的。

11、构成焊球阵列3的各个焊球为了防止与相邻焊球短路而需彼此保持既定距离,位于焊球阵列3外侧的焊球sb1、sb2、sb3、sb4、sb5、sb8、sb9、sb12、sb13、sb14、sb15及sb16之间的间隔也需保持恒定。

12、因此,即使设计上能够缩小作为半导体芯片基本结构的半导体裸片的大小,由于关于焊球之间需保持的间隔和外侧焊球与半导体芯片边缘之间需保持的间隔的规则,存在无法减小半导体芯片大小的问题。

13、[以往技术文献]

14、[专利文献]

15、ptl 1:韩国公开专利公报第10-2015-0116308号(公布日:2015年10月15日,名称:半导体封装及半导体器件封装方法(semiconductor package and semiconductor devicepackaging method))

16、ptl 2:韩国公开专利公报第10-2010-0047540号(公布日:2010年5月10日,名称:扇出晶片级封装及其制造方法(fan-out wafer level package and its manufacturingmethod))

技术实现思路

1、本公开提供一种相比以往矩形或正方形芯片封装,芯片大小能够减小约5%至12%的菱形的晶片级芯片尺寸封装。

2、另外,本公开提供一种使用以往半导体制造装备便能够制造的菱形的晶片级芯片尺寸封装。

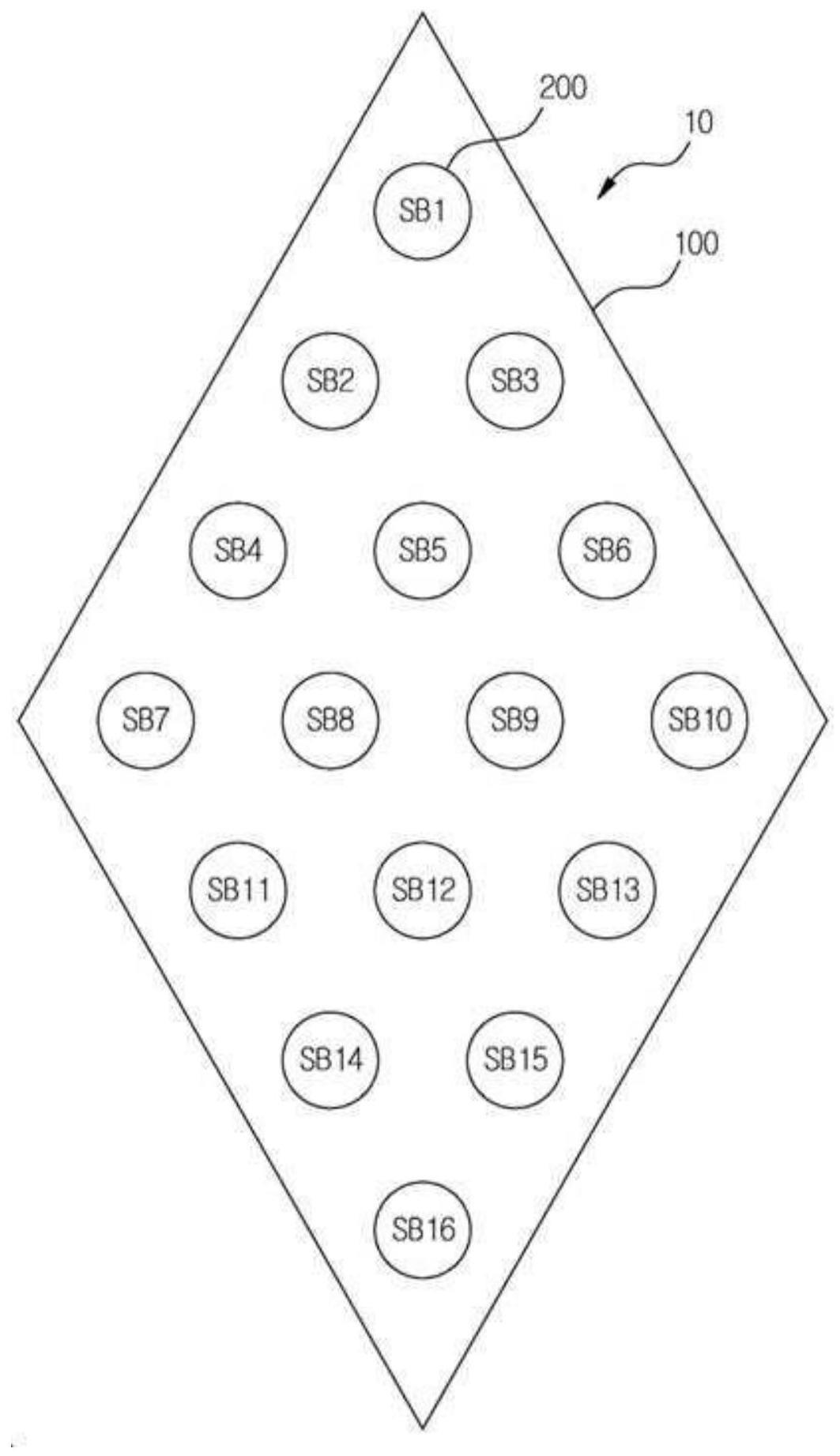

3、根据本发明一个示例性实现例,菱形的晶片级芯片尺寸封装包括:菱形的半导体芯片;及焊球阵列,所述焊球阵列由在半导体芯片的一面上形成的多个焊球构成;其中,半导体芯片的4个内角中,沿短对角线方向相向的2个内角约为120°,沿长对角线方向相向的2个内角约为60°。

4、在菱形的晶片级芯片尺寸封装中,构成焊球阵列的各焊球之间的间隔距离可以相同。

5、在菱形的晶片级芯片尺寸封装中,半导体芯片可以具有由2个等边三角形结合而成的平面形状,构成焊球阵列的多个焊球可以相对于半导体芯片的短对角线和长对角线,对称排列于半导体芯片的一面上。

6、在菱形的晶片级芯片尺寸封装中,中心点可以位于与半导体芯片的一面相应的2个等边三角形区域之一,连接彼此相邻的3个焊球的中心点的3条线段可以形成等边三角形。

7、在菱形的晶片级芯片尺寸封装中,n个焊球可以排列于半导体芯片的短对角线上,在半导体芯片的短对角线的上部和下部区域,焊球数可以以从n个焊球起逐个递减直至为一个焊球时为止的方式交替排列。

技术特征:

1.一种菱形的晶片级芯片尺寸封装,包括:

2.根据权利要求1所述的菱形的晶片级芯片尺寸封装,其中,

3.根据权利要求2所述的晶片级芯片尺寸封装,其特征在于,

4.根据权利要求3所述的晶片级芯片尺寸封装,其中,

5.根据权利要求4所述的晶片级芯片尺寸封装,其特征在于,

技术总结

本公开涉及一种菱形的晶片级芯片尺寸封装。本公开包括:菱形的半导体芯片;及焊球阵列,所述焊球阵列由在所述半导体芯片的一面上形成的多个焊球构成;其中,所述半导体芯片的4个内角中,沿短对角线方向相向的2个内角约为120°,沿长对角线方向相向的2个内角约为60°。根据本公开,菱形的晶片级芯片尺寸封装的提供,相比以往矩形或正方形芯片封装,芯片大小可以减小约5%至12%,具有使用以往的半导体制造装备便可制作的效果。

技术研发人员:洪志勳

受保护的技术使用者:矽致微有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!