半导体器件的终端结构的制作方法

本申请涉及半导体器件,尤其涉及一种半导体器件的终端结构。

背景技术:

1、功率半导体器件的设计除了元胞设计很重要外终端的设计也不能忽视,好的终端设计能有效的提高器件耐压、可靠性等特性。一个优化的终端设计应该使表面的电场峰值尽量最小化或者转移到体内,在超结功率半导体器件中,高的外延层浓度会带来终端性能的不稳定,导致低电压下的终端提前发生击穿。在传统的终端技术中,通常采用场限环、场板和结终端延伸等技术削弱器件主结的曲率效应,最后达到提高器件耐压能力的目的。由于超结结构特点,传统功率半导体器件的终端结构不再适用超结功率半导体器件。目前应用最广泛的超结功率半导体器件终端结构是采用和元胞相同的超结结构,具体地,在超结功率半导体器件终端表面为多个交替的p/n结。而此种结构导致现有的超结功率半导体器件终端尺寸较大,生产成本高,性价比较低。

技术实现思路

1、本申请实施例提供的半导体器件的终端结构,能够有效降低终端结构的尺寸。

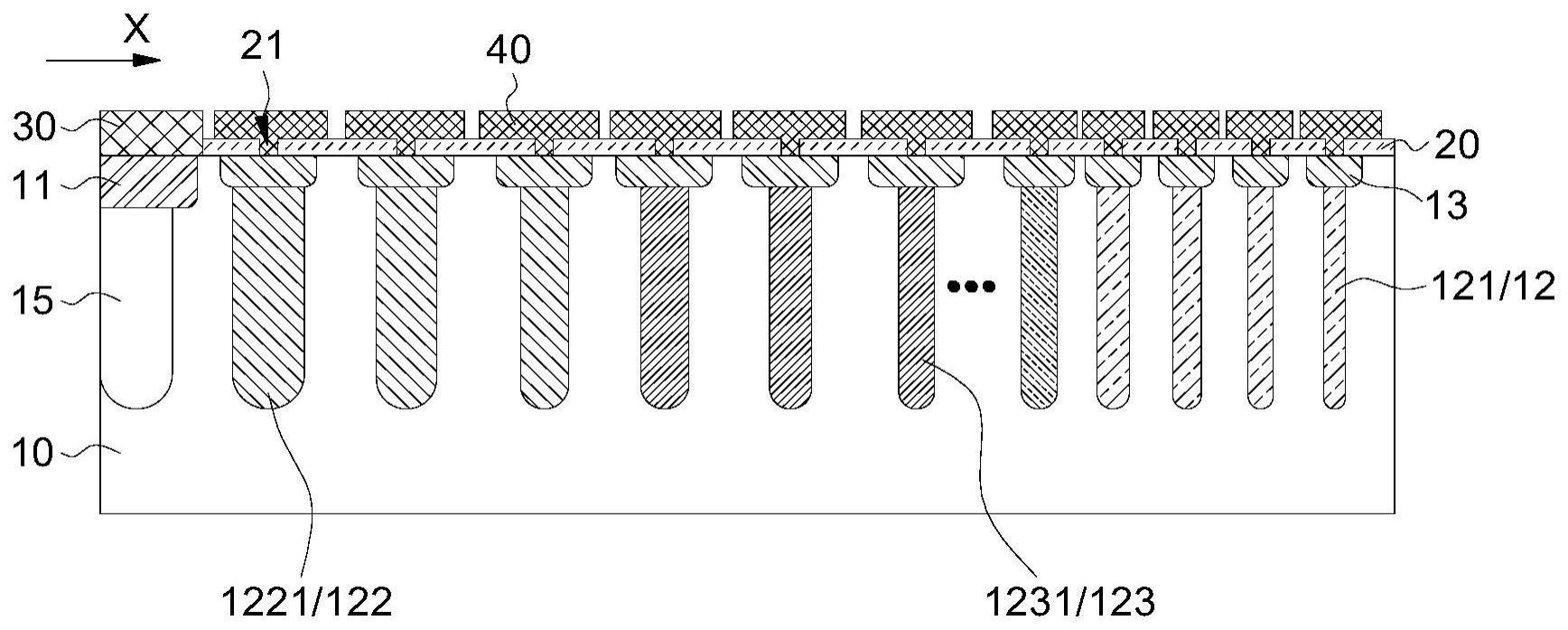

2、一方面,根据本申请实施例提出了一种半导体器件的终端结构,包括:外延层,包括相对设置的第一表面和第二表面,外延层为第一掺杂类型,外延层包括元胞区半导体部、多个掺杂部以及终端区半导体部,元胞区半导体部、多个掺杂部以及终端区半导体部均为第二掺杂类型,元胞区半导体部与终端区半导体部均位于第一表面朝向第二表面的一侧,且元胞区半导体部与终端区半导体部沿第一方向间隔设置,多个掺杂部至少位于终端区半导体部背向第一表面的一侧。绝缘层,位于第一表面,且绝缘层至少覆盖终端区半导体部设置。第一金属层,位于第一表面,且第一金属层至少覆盖元胞区半导体部设置。其中,各掺杂部均包括m个子掺杂部,各掺杂部内,第n个子掺杂部沿第一方向上的尺寸以及第n个子掺杂部与第n-1个子掺杂部沿第一方向之间的距离之和为预定值,多个预定值相等,沿元胞区半导体部指向终端区半导体部的方向上,多个子掺杂部沿第一方向上的尺寸呈递减趋势,m≥2,n为m中的任意自然数。第一方向与外延层的厚度方向相交设置。

3、根据本申请实施例的一个方面,掺杂部包括相邻设置的第一掺杂部和第二掺杂部,第一掺杂部包括多个第一子掺杂部,第n个第一子掺杂部沿第一方向上的尺寸以及第n个第一子掺杂部与第n-1个第一子掺杂部沿第一方向之间的距离之和为第一预定值。第二掺杂部包括多个第二子掺杂部,第n个第二子掺杂部沿第一方向上的尺寸以及第n个第二子掺杂部与第n-1个第二子掺杂部沿第一方向之间的距离之和为第二预定值。

4、根据本申请实施例的一个方面,第一预定值大于第二预定值。

5、根据本申请实施例的一个方面,第一预定值小于或等于第二预定值。

6、根据本申请实施例的一个方面,第m个第一子掺杂部沿第一方向上的尺寸大于第一个第二子掺杂部沿第一方向上的尺寸。

7、根据本申请实施例的一个方面,第m个第一子掺杂部沿第一方向上的尺寸小于或等于第一个第二子掺杂部沿第一方向上的尺寸。

8、根据本申请实施例的一个方面,终端区半导体部的掺杂浓度大于掺杂部的掺杂浓度。

9、根据本申请实施例的一个方面,还包括第二金属层,第二金属层至少位于绝缘层背向第一表面的一侧,第二金属层与终端区半导体部电接触。

10、根据本申请实施例的一个方面,终端区半导体部的数量包括多个,各终端区半导体部与各子掺杂部一一对应设置,绝缘层设有多个通孔,第二金属层通过各通孔与各终端区半导体部电连接。

11、根据本申请实施例的一个方面,外延层还包括多个凹槽,凹槽由第一表面向第二表面的方向凹陷形成,子掺杂部至少位于凹槽内壁背向凹槽的凹陷空间的一侧。

12、根据本申请提供的半导体器件的终端结构中,半导体器件的终端结构包括外延层、绝缘层以及第一金属层。外延层包括多个掺杂部,多个掺杂部中均包括m个子掺杂部,使得将子掺杂部分成多个组别,降低了子掺杂部在制作过程中,子掺杂部之间的间距误差对器件耐压性能的影响,增加了工艺容差,降低了制作难度,并且减小了制作过程中间距误差在元胞区主结或终端区边缘产生局部峰值电场问题,提高了器件的耐压性能和可靠性。在每个掺杂部内,多个预定值相等,有利于保证每个掺杂部的可靠性,多个子掺杂部沿第一方向上的尺寸呈递减趋势,可以减小每个掺杂部的总尺寸,从而减小每个掺杂部在终端结构中占用的空间,从而降低终端结构的总尺寸,降低了器件成本。

技术特征:

1.一种半导体器件的终端结构,其特征在于,包括:

2.根据权利要求1所述的半导体器件的终端结构,其特征在于,所述掺杂部包括相邻设置的第一掺杂部和第二掺杂部,所述第一掺杂部包括多个第一子掺杂部,第n个所述第一子掺杂部沿所述第一方向上的尺寸以及第n个所述第一子掺杂部与第n-1个所述第一子掺杂部沿所述第一方向之间的距离之和为第一预定值;

3.根据权利要求2所述的半导体器件的终端结构,其特征在于,所述第一预定值大于所述第二预定值。

4.根据权利要求2所述的半导体器件的终端结构,其特征在于,所述第一预定值小于或等于所述第二预定值。

5.根据权利要求2所述的半导体器件的终端结构,其特征在于,第m个所述第一子掺杂部沿所述第一方向上的尺寸大于第一个所述第二子掺杂部沿所述第一方向上的尺寸。

6.根据权利要求2所述的半导体器件的终端结构,其特征在于,第m个所述第一子掺杂部沿所述第一方向上的尺寸小于或等于第一个所述第二子掺杂部沿所述第一方向上的尺寸。

7.根据权利要求1所述的半导体器件的终端结构,其特征在于,所述终端区半导体部的掺杂浓度大于所述掺杂部的掺杂浓度。

8.根据权利要求1所述的半导体器件的终端结构,其特征在于,还包括第二金属层,所述第二金属层至少位于所述绝缘层背向所述第一表面的一侧,所述第二金属层与所述终端区半导体部电接触。

9.根据权利要求8所述的半导体器件的终端结构,其特征在于,所述终端区半导体部的数量包括多个,各所述终端区半导体部与各所述子掺杂部一一对应设置,所述绝缘层设有多个通孔,所述第二金属层通过各所述通孔与各所述终端区半导体部电连接。

10.根据权利要求1所述的半导体器件的终端结构,其特征在于,所述外延层还包括多个凹槽,所述凹槽由所述第一表面向第二表面的方向凹陷形成,所述子掺杂部至少位于所述凹槽内壁背向凹槽的凹陷空间的一侧。

技术总结

本申请涉及一种半导体器件的终端结构,半导体器件的终端结构包括外延层、绝缘层以及第一金属层。外延层包括相对设置的第一表面和第二表面。外延层包括元胞区半导体部、多个掺杂部以及终端区半导体部。多个掺杂部至少位于终端区半导体部背向第一表面的一侧。其中,各掺杂部均包括M个子掺杂部。各掺杂部内,第N个子掺杂部沿第一方向上的尺寸以及第N个子掺杂部与第N‑1个子掺杂部沿第一方向之间的距离之和为预定值,多个预定值相等。各掺杂部内,沿元胞区半导体部指向终端区半导体部的方向上,多个子掺杂部沿第一方向上的尺寸呈递减趋势,M≥2,N为M中的任意自然数。本申请能够有效降低终端结构的尺寸。

技术研发人员:兰金龙,祁金伟

受保护的技术使用者:苏州华太电子技术股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!