量子比特的制造方法及量子芯片与流程

本申请属于量子信息领域,尤其是量子计算,特别地,本申请涉及一种量子比特的制造方法及量子芯片。

背景技术:

1、量子芯片是量子计算机的核心部件。超导物理体系的量子芯片,其基本结构是:将由约瑟夫森结并联形成的超导量子干涉装置squid,与额外构建的电容极板并联,基于该并联结构形成的超导量子比特电路即作为量子芯片上执行量子计算的基本单元——量子比特。约瑟夫森结(josephson junction),一般是由两块超导体夹以某种很薄的势垒层(厚度≤cooper电子对的相干长度)而构成的结构,例如s(超导材料层)—i(半导体或绝缘体材料层)—s(超导材料层)结构。超导量子干涉装置squid的性能质量直接决定量子比特性能的好坏,因此必须进行测试来确认是否合格。

2、发明创造内容

3、本申请的实施例提供一种量子比特的制造方法及量子芯片,以实现对超导量子干涉装置squid的高效电学检测。

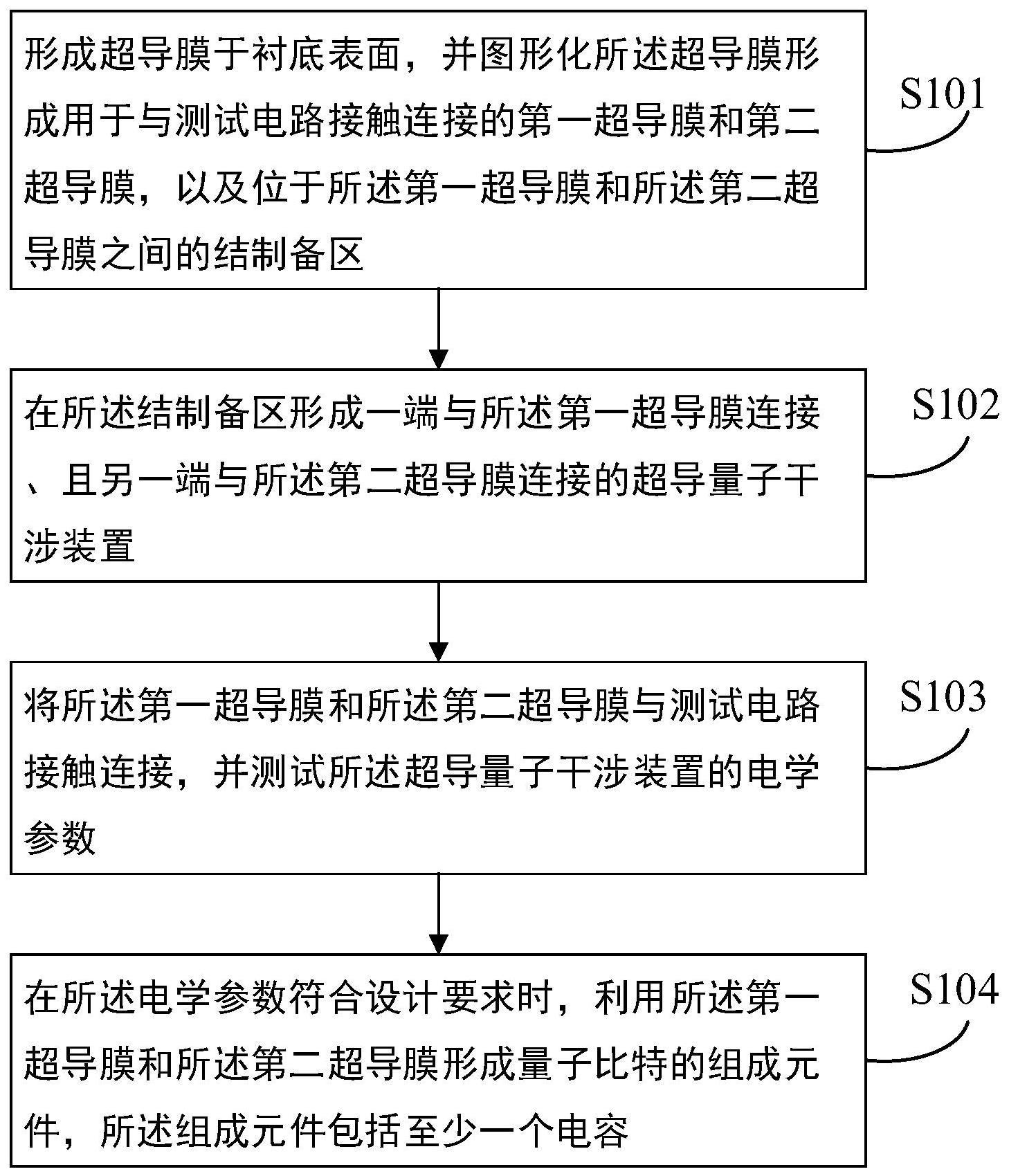

4、本申请的一个实施例提供了一种量子比特的制造方法,包括:

5、形成超导膜于衬底表面,并图形化所述超导膜形成用于与测试电路接触连接的第一超导膜和第二超导膜,以及位于所述第一超导膜和所述第二超导膜之间的结制备区;

6、在所述结制备区形成一端与所述第一超导膜连接、且另一端与所述第二超导膜连接的超导量子干涉装置;

7、将所述第一超导膜和所述第二超导膜与测试电路接触连接,并测试所述超导量子干涉装置的电学参数;

8、在所述电学参数符合设计要求时,利用所述第一超导膜和所述第二超导膜形成量子比特的组成元件,所述组成元件包括至少一个电容。

9、如上所述的制造方法,在一些实施方式中,所述利用所述第一超导膜和所述第二超导膜形成量子比特的组成元件的步骤,包括:图形化所述第一超导膜形成电容,并图形化所述第二超导膜形成地,且所述电容与所述超导量子干涉装置的一端连接,所述地与所述超导量子干涉装置的另一端连接。

10、如上所述的制造方法,在一些实施方式中,所述利用所述第一超导膜和所述第二超导膜形成量子比特的组成元件的步骤,包括:图形化所述第一超导膜形成第一电容,并图形化所述第二超导膜形成第二电容,且所述第一电容与所述超导量子干涉装置的一端连接,所述第二电容与所述超导量子干涉装置的另一端连接。

11、如上所述的制造方法,在一些实施方式中,所述超导量子干涉装置包括至少两个约瑟夫森结,且所述约瑟夫森结形成并联。

12、如上所述的制造方法,在一些实施方式中,所述约瑟夫森结的数量为奇数。

13、如上所述的制造方法,在一些实施方式中,所述约瑟夫森结的临界电流不相同。

14、如上所述的制造方法,在一些实施方式中,所述约瑟夫森结为隧道结、点接触、或者其他呈现约瑟夫森效应的结构。

15、如上所述的制造方法,在一些实施方式中,还包括:在所述电学参数不符合设计要求时,去除所述超导量子干涉装置,并返回所述在所述结制备区形成一端与所述第一超导膜连接、且另一端与所述第二超导膜连接的超导量子干涉装置的步骤。

16、如上所述的制造方法,在一些实施方式中,所述电学参数包括电阻值。

17、本申请的另一个实施例提供了一种量子芯片,它包括根据如上所述制造方法制造的量子比特。

18、与现有技术相比,本申请提供的量子比特的制造方法,通过形成超导膜于衬底表面,并图形化所述超导膜形成用于与测试电路接触连接的第一超导膜和第二超导膜,以及位于所述第一超导膜和所述第二超导膜之间的结制备区;然后在所述结制备区形成一端与所述第一超导膜连接、且另一端与所述第二超导膜连接的超导量子干涉装置;再将所述第一超导膜和所述第二超导膜与测试电路接触连接,并测试所述超导量子干涉装置的电学参数;最后在所述电学参数符合设计要求时,利用所述第一超导膜和所述第二超导膜形成量子比特的组成元件,所述组成元件包括至少一个电容。本申请提出的方案,先利用第一超导膜、第二超导膜与测试电路接触连接实现超导量子干涉装置的电学参数测量,再针对第一超导膜、第二超导膜上实施图形化工艺等,从而可以在第一超导膜、第二超导膜基础上形成量子比特的组成元件。本申请利用超导膜直接构建出方便超导量子干涉装置测试时实现接触连接的区域,有助于实现对超导量子干涉装置squid的高效电学检测。

技术实现思路

技术特征:

1.一种量子比特的制造方法,其特征在于,包括:

2.根据权利要求1所述的制造方法,其特征在于,所述利用所述第一超导膜和所述第二超导膜形成量子比特的组成元件的步骤,包括:

3.根据权利要求1所述的制造方法,其特征在于,所述利用所述第一超导膜和所述第二超导膜形成量子比特的组成元件的步骤,包括:

4.根据权利要求1至3任一项所述的制造方法,其特征在于,所述超导量子干涉装置包括至少两个约瑟夫森结,且所述约瑟夫森结形成并联。

5.根据权利要求4所述的制造方法,其特征在于,所述约瑟夫森结的数量为奇数。

6.根据权利要求4所述的制造方法,其特征在于,所述约瑟夫森结的临界电流不相同。

7.根据权利要求4所述的制造方法,其特征在于,所述约瑟夫森结为隧道结、点接触、或者其他呈现约瑟夫森效应的结构。

8.根据权利要求1至3、5至7所述的制造方法,其特征在于,还包括:

9.根据权利要求1至3、5至7所述的制造方法,其特征在于,所述电学参数包括电阻值。

10.一种量子芯片,其特征在于,包括根据权利要求1至9中任一项所述制造方法制造的量子比特。

技术总结

本申请公开了一种量子比特的制造方法及量子芯片,属于量子计算技术领域。本申请提出的方案,先利用第一超导膜、第二超导膜与测试电路接触连接实现超导量子干涉装置的电学参数测量,再针对第一超导膜、第二超导膜上实施图形化工艺等,在第一超导膜、第二超导膜的基础上即可形成量子比特的组成元件。本申请利用超导膜直接构建出方便超导量子干涉装置测试时实现接触连接的区域,有助于实现对超导量子干涉装置squid的高效电学检测。

技术研发人员:请求不公布姓名,请求不公布姓名,张辉

受保护的技术使用者:本源量子计算科技(合肥)股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!