提升锗硅机台WPH的方法与流程

本发明涉及半导体制造,特别是涉及一种提升锗硅机台wph的方法。

背景技术:

1、随着mosfet的缩小,为了提高mosfet的性能,pmos引入嵌入式锗硅工艺,该工艺通过施加应力来提高空穴的迁移率,从而提高pmos器件性能。嵌入式锗硅工艺被广泛应用于90nm及以下技术中的应力工程,利用锗、硅晶格常数的不同所产生的应力,嵌入在源漏区,提高pmos空穴的迁移率和饱和电流。

2、在版图设计中,现有28nm工艺通过对低压(lv)区域的pmos进行sige应变材料的源漏嵌入来提升芯片的运行效率,而sige应变材料的生长方式为外延生长,故原则上的sige图形越多,其生长的速度越快。但若sig额图形密度过高,又会因为生长负载(loading)过大使得制程时间较长,从而导致机台产能利用率降低,因此,从而工厂厂能角度出发,需要对sige图形密度进行合理控制。现有的28hv工艺,sige图形仅存在于lv区域,而lv区域占比较低,因此,sige图形密度较低,从而导致sige材料生长较慢,制程时间过长,继而造成机台产能损失。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种锗硅机台wph的方法,用于解决现有的因sige图形密度较低导致机台产能受到影响的问题。

2、为实现上述目的及其他相关目的,本发明提供一种锗硅机台wph的方法,所述方法包括:

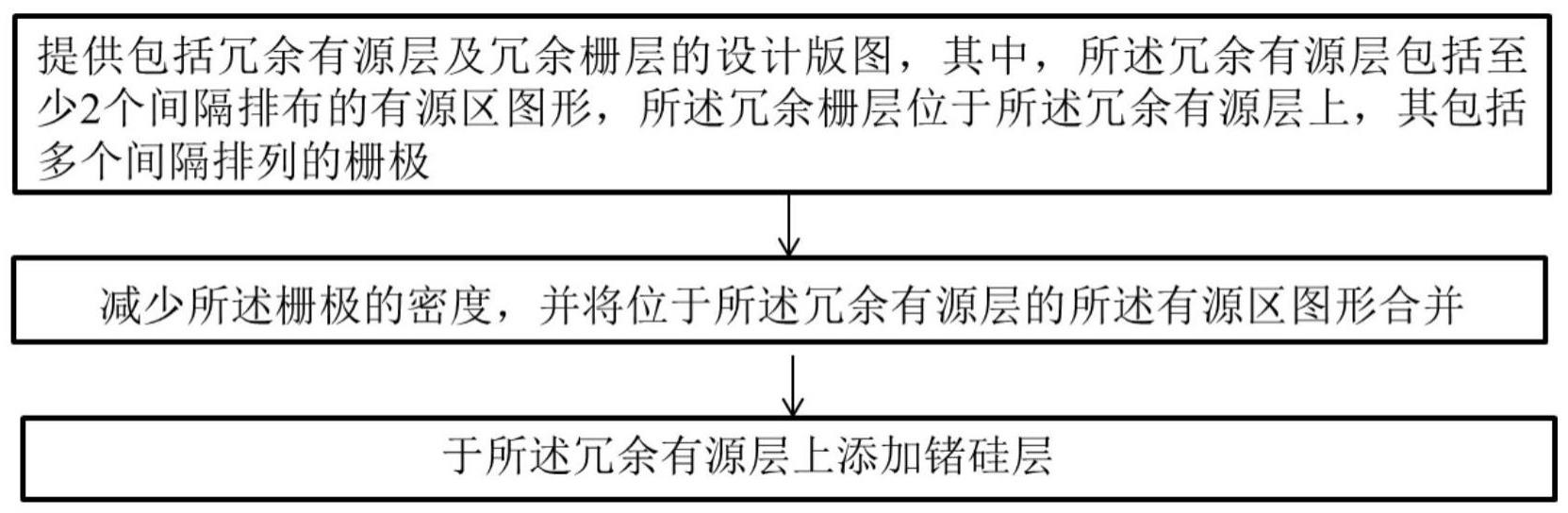

3、提供包括冗余有源层及冗余栅层的设计版图,其中,所述冗余有源层包括至少2个间隔排布的有源区图形,所述冗余栅层位于所述冗余有源层上,其包括多个间隔排列的栅极;

4、减少所述栅极的密度,并将所述有源区图形合并;

5、于所述冗余有源层上添加锗硅层。

6、可选地,所述栅极的个数为4。

7、可选地,减少所述栅极的密度的方法包括:将所述栅极的个数由4减少为2。

8、可选地,所述锗硅层添加于所述有源区图形未被所述栅极覆盖的全部区域上。

9、可选地,所述设计版图包括伪栅,所述伪栅形成于所述有源区图形的两侧,且与所述栅极平行。

10、可选地,所述冗余有源层位于切割道。

11、可选地,所述冗余有源层包括普通冗余有源区及测试冗余有源区,其中,所述测试冗余有源区用于形成测试用器件结构,此时,所述普通冗余有源区及所述测试冗余有源区均包括至少2个所述有源区图形。

12、如上所述,本发明的提升锗硅机台wph的方法,通过减少栅极的密度并将有源区图形合并,以增加sige图形的可添加范围,使得sige图形密度由6%提升至7%,从而减少sige图形生长时间,缩短工艺时间,将wph(每小时的出片量)由原来的1.6pcs/chamber提高至1.8pcs/chamber,提高机台产能。

技术特征:

1.一种提升锗硅机台wph的方法,其特征在于,所述方法包括:

2.根据权利要求1所述的提升锗硅机台wph的方法,其特征在于,所述栅极的个数为4。

3.根据权利要求2所述的提升锗硅机台wph的方法,其特征在于,减少所述栅极的密度的方法包括:将所述栅极的个数由4减少为2。

4.根据权利要求1~3任一项所述的提升锗硅机台wph的方法,其特征在于,所述锗硅层添加于所述有源区图形未被所述栅极覆盖的全部区域上。

5.根据权利要求1所述的提升锗硅机台wph的方法,其特征在于,所述设计版图包括伪栅,所述伪栅形成于所述有源区图形的两侧,且与所述栅极平行。

6.根据权利要求1所述的提升锗硅机台wph的方法,其特征在于,所述冗余有源层位于切割道。

7.根据权利要求1所述的提升锗硅机台wph的方法,其特征在于,所述冗余有源层包括普通冗余有源区及测试冗余有源区,其中,所述测试冗余有源区用于形成测试用器件结构,此时,所述普通冗余有源区及所述测试冗余有源区均包括至少2个所述有源区图形。

技术总结

本发明提供一种提升锗硅机台WPH的方法,所述方法包括:提供包括冗余有源层及冗余栅层的设计版图,其中,所述冗余有源层包括至少2个间隔排布的有源区图形,所述冗余栅层位于所述冗余有源层上,其包括多个间隔排列的栅极;减少所述栅极的密度,并将位于所述冗余有源层的所述有源区图形合并;于所述冗余有源层上添加锗硅层。通过本发明解决了现有的因SiGe图形密度较低导致机台产能受到影响的问题。

技术研发人员:刘晓梅,彭翔,程器,张婷,唐小亮

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!