半导体结构及其形成方法与流程

本申请的实施例涉及半导体,更具体地,涉及半导体结构及其形成方法。

背景技术:

1、半导体集成电路(ic)行业经历了快速增长。在ic发展过程中,当几何尺寸(即,可以使用制造工艺创建的最小部件(或线))减小时,功能密度(即,每芯片面积的互连器件的数量)通常增加。这种按比例缩小的工艺通常通过提高生产效率和降低相关成本而提供益处。然而,这种按比例缩小还伴随着增加设计和制造包含这些ic的器件的复杂性,为了实现这些进步,需要在器件制造方面有类似的发展。

2、例如,随着集成电路(ic)技术朝着更小的技术节点发展,引入了多栅极金属氧化物半导体场效应晶体管(多栅极mosfet或多栅极器件),以通过增加栅极沟道耦合、降低截止电流和降低短沟道效应(sce)来改善栅极控制。多栅极器件通常指具有栅极结构或其部分的器件,栅极结构设置在沟道区的多于一侧上。鳍状场效应晶体管(finfet)和多桥沟道(mbc)晶体管是多栅极器件的示例,它们已成为高性能和低泄漏应用的热门和有前途的候选器件。finfet具有升高的沟道,升高的沟道由位于多于一侧上的栅极包裹(例如,栅极包裹从衬底延伸的半导体材料“鳍”的顶部和侧壁)。mbc晶体管具有的该栅极结构可以部分地或完全地围绕沟道区延伸,以提供对两侧或更多侧上的沟道区的接入。因为其栅极结构围绕沟道区,所以mbc晶体管也可以被称为环绕栅极晶体管(sgt)或全环栅(gaa)晶体管。

3、自对准接触技术有助于形成连接更小的多栅极晶体管结构的接触件。为了允许接触结构的自对准形成,可以在多栅极器件的高k金属栅极结构上方形成自对准帽层。这种自对准帽层的形成可以包括使栅极结构凹陷以形成凹陷并在凹陷中沉积帽介电层。这一制程并非没有挑战。在一些技术中,帽介电层包括高k介电材料,其倾向于增加有效电容。在一些技术中,凹陷被限定在至少一个栅极间隔件层中。源极/漏极接触件开口的形成可以破坏至少一个栅极间隔件层以导致电短路。虽然现有的自对准接触件形成工艺通常足以达到其预期目的,但它们并不是在所有方面都令人满意。

技术实现思路

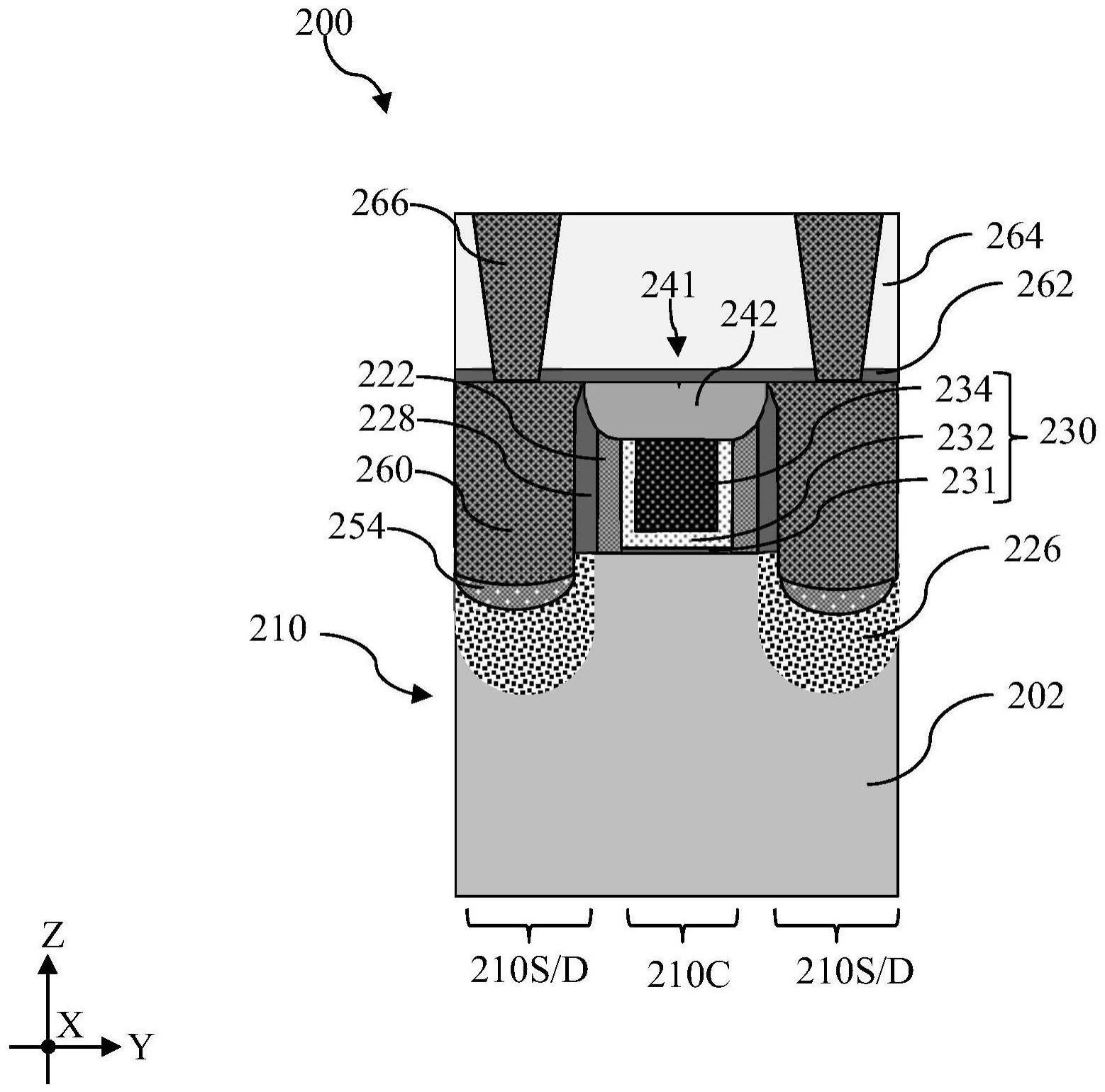

1、根据本申请的实施例的一个方面,提供了一种半导体结构,包括:有源区,包括沟道区和源极/漏极区;栅极结构,位于沟道区上方;栅极间隔件层,设置在沟道区上方并且沿着栅极结构的侧壁延伸;外延源极/漏极部件,位于源极/漏极区上方;接触蚀刻停止层(cesl),设置在外延源极/漏极部件上并且沿着栅极间隔件层的侧壁延伸;源极/漏极接触件,设置在外延源极/漏极部件上方;以及介电帽层,设置在栅极结构、栅极间隔件层和cesl的至少部分上方,其中,源极/漏极接触件的侧壁与cesl的侧壁直接接触。

2、根据本申请的实施例的另一个方面,提供了一种半导体结构,包括:金属栅极结构,沿着第一方向延伸细长段的宽度;一对栅极间隔件层,沿着垂直于第一方向的第二方向夹持金属栅极结构;一对接触蚀刻停止层,沿着第二方向夹持一对栅极间隔件层;和介电帽,设置在金属栅极结构、一对栅极间隔件层和一对接触蚀刻停止层的至少部分上方,其中,介电帽包括沿着第二方向的顶部宽度和沿着第二方向的底部宽度,其中,顶部宽度大于底部宽度。

3、根据本申请的实施例的又一个方面,提供了一种形成半导体结构的方法,包括:在衬底上方形成半导体元件,半导体元件包括沟道区和源极/漏极区;在半导体元件的沟道区上方形成伪栅极堆叠件;在伪栅极堆叠件的侧壁上方沉积间隔件层;在沉积间隔件层之后,蚀刻半导体元件的源极/漏极区以形成源极/漏极凹陷;在源极/漏极凹陷中形成源极/漏极部件;在间隔件层和源极/漏极部件的侧壁上方沉积接触蚀刻停止层(cesl);在cesl上方沉积层间介电(ild)层;执行第一平坦化以暴露伪栅极堆叠件;用金属栅极结构替换伪栅极堆叠件;使金属栅极结构凹陷以形成凹陷;在凹陷上方沉积介电层;执行第二平坦化以暴露ild层;各向异性地蚀刻源极/漏极部件、cesl、间隔件层和介电层以形成接触开口;在接触开口上方沉积金属层以形成源极/漏极接触件;以及执行第三平坦化,使得源极/漏极接触件、cesl和介电层是共面的。

技术特征:

1.一种半导体结构,包括:

2.根据权利要求1所述的半导体结构,其中,所述有源区包括鳍结构,并且所述栅极结构包裹在所述鳍结构上方。

3.根据权利要求1所述的半导体结构,其中,所述有源区包括纳米结构的垂直堆叠件,并且所述栅极结构包裹围绕每个纳米结构。

4.根据权利要求1所述的半导体结构,其中,所述介电帽层、所述源极/漏极接触件和所述接触蚀刻停止层的顶面是共面的。

5.根据权利要求1所述的半导体结构,其中,所述介电帽层包括在约3.9至约10之间的介电常数。

6.根据权利要求1所述的半导体结构,其中,所述介电帽层包括氮化硅、碳氮化硅、氮氧化硅、碳氧化硅、氧化铝、硅酸锆或硅酸铪。

7.根据权利要求1所述的半导体结构,其中,所述介电帽层的介电常数大于所述栅极间隔件层的介电常数。

8.根据权利要求1所述的半导体结构,其中,所述介电帽层的介电常数大于所述接触蚀刻停止层的介电常数。

9.一种半导体结构,包括:

10.一种形成半导体结构的方法,包括:

技术总结

本公开提供了半导体结构及其形成方法。根据本公开的半导体结构包括具有沟道区和源极/漏极区的有源区、沟道区上方的栅极结构、设置在沟道区上并沿着栅极结构的侧壁延伸的栅极间隔件层、位于源极/漏极区上方的外延源极/漏极部件、其设置在外延源极/漏极部件上并沿着栅极间隔件层的侧壁延伸的接触蚀刻停止层(CESL)、设置在外延漏极/源极部件上的源极/漏极接触件、以及设置在栅极结构、栅极间隔件层和CESL的至少部分上的介电帽层。源极/漏极接触件的侧壁与CESL的侧壁直接接触。

技术研发人员:林大钧,陈仪宪,罗文呈,李春霆,莫亦先,张志豪

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!