一种半导体器件及其制造方法

本发明涉及半导体,尤其涉及一种半导体器件及其制造方法。

背景技术:

1、环栅晶体管包括的栅堆叠不仅形成在沟道的顶部和侧壁上,还形成在沟道的底部,因此相对于平面晶体管和鳍式场效应晶体管,环栅晶体管具有较高的栅控能力等优势。并且,在cmos器件中,nmos环栅晶体管通常采用应变硅、较低锗含量的锗硅或ⅲ-ⅴ族材料制造沟道,以及采用锗硅等高迁移率沟道材料制造pmos环栅晶体管包括的沟道,以降低nmos环栅晶体管和pmos环栅晶体管对应的载流子迁移率之间的差值,使得上述两类晶体管同时具有良好的导电性能。

2、但是,难以采用现有的制造方法实现对上述具有不同沟道材料的nmos环栅晶体管和pmos环栅晶体管的制造,不利于提升cmos器件的工作性能。

技术实现思路

1、本发明的目的在于提供一种半导体器件及其制造方法,用于实现具有不同沟道材料的nmos环栅晶体管和pmos环栅晶体管的制造,利于提升cmos器件的工作性能。

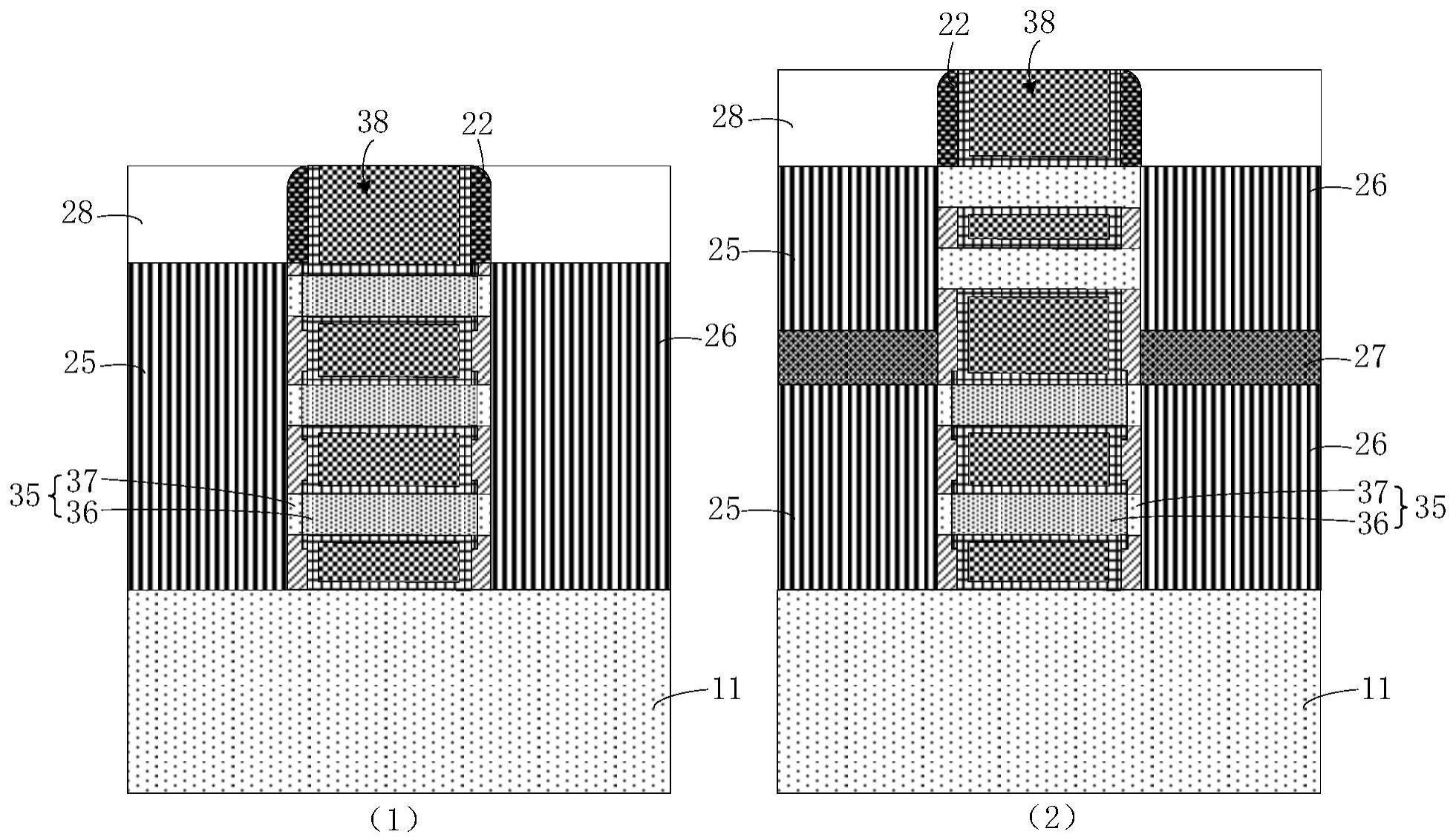

2、为了实现上述目的,第一方面,本发明提供了一种半导体器件,该半导体器件包括:间隔分布的n型环栅晶体管和p型环栅晶体管。上述n型环栅晶体管包括的有源结构和p型环栅晶体管包括的有源结构均具有源区、漏区、以及位于源区和漏区之间的至少一层纳米结构。并且,p型环栅晶体管包括的至少一层纳米结构被p型环栅晶体管包括的栅堆叠结构覆盖的部分为沟道部,p型环栅晶体管包括的至少一层纳米结构被p型环栅晶体管包括的栅极侧墙覆盖的部分为连接部。沟道部内的锗含量分别大于连接部内的锗含量、以及n型环栅晶体管包括的至少一层纳米结构内的锗含量。

3、采用上述技术方案的情况下,p型环栅晶体管包括的至少一层纳米结构位于p型环栅晶体管包括的源区和漏区之间。并且,p型环栅晶体管包括的至少一层纳米结构被p型环栅晶体管包括的栅堆叠结构覆盖的部分为沟道部,以及p型环栅晶体管包括的至少一层纳米结构被p型环栅晶体管包括的栅极侧墙覆盖的部分为连接部。同时,上述沟道部内的锗含量大于n型环栅晶体管包括的至少一层纳米结构内的锗含量。基于此,因与硅材料等n型环栅晶体管包括的纳米结构常采用的半导体材料相比,锗硅或锗等含锗半导体材料具有更高的载流子迁移率,故在p型环栅晶体管包括的沟道部内的锗含量大于n型环栅晶体管包括的至少一层纳米结构内的锗含量的情况下,利于使得器件类型同为环栅晶体管的n型环栅晶体管的沟道载流子迁移率优于p型环栅晶体管的沟道载流子迁移率,也可以通过上述锗含量较高的高迁移率沟道材料制造pmos晶体管的沟道的方式,降低二者对应的载流子迁移率之间的差值,同时也可以防止n型环栅晶体管包括的纳米结构含有锗或含较高含量的锗而出现界面态较差、源漏接触电阻高等问题,使得n型环栅晶体管和p型环栅晶体管同时具有良好的导电性能。

4、另外,与锗含量较高的半导体材料相比,硅等锗含量较低的半导体材料的禁带宽度较大,即硅等锗含量较低的半导体材料对载流子的束缚能力更强。基于此,p型环栅晶体管包括的沟道部内的锗含量大于连接部内的锗含量,此时在p型环栅晶体管包括的锗含量较高的沟道部分别与源区和漏区之间设置锗含量较低的连接部,该连接部的存在可以提高沟道部分别与源区和漏区之间的载流子束缚能力,从而降低漏电,进一步改善p型环栅晶体管的电学性能。

5、第二方面,本发明还提供了一种半导体器件的制造方法,该半导体器件的制造方法包括:首先,在半导体基底上形成间隔分布的第一预形成结构和第二预形成结构。第一预形成结构和第二预形成结构均包括至少一层悬空沟道层、以及横跨在至少一层悬空沟道层沿长度方向的两侧边缘区域上的栅极侧墙。第二预形成结构还包括仅位于每层悬空沟道层沿厚度方向两侧的含锗半导体层。含锗半导体层内的锗含量大于悬空沟道层内的锗含量。接下来,在第一掩膜层和第二预形成结构包括的栅极侧墙的掩膜作用下,对第二预形成结构包括的含锗半导体层和至少一层悬空沟道层暴露在外的部分进行浓缩氧化处理。第一掩膜层覆盖在第一预形成结构上。接下来,基于第一预形成结构形成n型环栅晶体管、以及基于经浓缩氧化处理后的第二预形成结构形成p型环栅晶体管。其中,n型环栅晶体管和p型环栅晶体管间隔分布。n型环栅晶体管包括的有源结构和p型环栅晶体管包括的有源结构均具有源区、漏区、以及位于源区和漏区之间的至少一层纳米结构。p型环栅晶体管包括的至少一层纳米结构被p型环栅晶体管包括的栅堆叠结构覆盖的部分为沟道部,p型环栅晶体管包括的至少一层纳米结构被p型环栅晶体管包括的栅极侧墙覆盖的部分为连接部。沟道部内的锗含量分别大于连接部内的锗含量、以及n型环栅晶体管包括的至少一层纳米结构内的锗含量。

6、本发明中第二方面及其各种实现方式的有益效果,可以参考第一方面及其各种实现方式中的有益效果分析,此处不再赘述。

技术特征:

1.一种半导体器件,其特征在于,包括:间隔分布的n型环栅晶体管和p型环栅晶体管;

2.根据权利要求1所述的半导体器件,其特征在于,所述沟道部内的锗含量大于等于10%、且小于等于60%;和/或,

3.根据权利要求1所述的半导体器件,其特征在于,所述连接部和所述n型环栅晶体管包括的所述至少一层纳米结构内的锗含量均为0。

4.根据权利要求1所述的半导体器件,其特征在于,所述连接部的材料为硅或锗硅;在所述连接部的材料为锗硅的情况下,所述连接部内的锗含量小于10%;和/或,

5.根据权利要求1所述的半导体器件,其特征在于,所述p型环栅晶体管包括位于所述源区与所述栅堆叠结构之间、以及位于所述漏区与所述栅堆叠结构之间的内侧墙;

6.根据权利要求1所述的半导体器件,其特征在于,所述半导体器件还包括半导体基底;

7.一种半导体器件的制造方法,其特征在于,包括:

8.根据权利要求7所述的半导体器件的制造方法,其特征在于,所述第一预形成结构和所述第二预形成结构包括的所述至少一层悬空沟道层的材料相同;和/或,

9.根据权利要求8所述的半导体器件的制造方法,其特征在于,所述在半导体基底上形成间隔分布的第一预形成结构和第二预形成结构,包括:

10.根据权利要求9所述的半导体器件的制造方法,其特征在于,所述n型环栅晶体管和所述p型环栅晶体管沿平行于所述半导体基底的表面方向间隔分布在所述半导体基底上;

11.根据权利要求9所述的半导体器件的制造方法,其特征在于,所述n型环栅晶体管和所述p型环栅晶体管沿所述半导体基底的厚度方向间隔分布在所述半导体基底上;

12.根据权利要求9所述的半导体器件的制造方法,其特征在于,所述在所述牺牲栅和所述栅极侧墙的掩膜作用下,刻蚀所述第二鳍状结构后,所述在所述第二鳍状结构的剩余部分沿长度方向的两侧分别形成p型环栅晶体管包括的源区和漏区前,所述半导体器件的制造方法还包括:

技术总结

本发明公开一种半导体器件及其制造方法,涉及半导体技术领域,以实现具有不同沟道材料的NMOS环栅晶体管和PMOS环栅晶体管的制造,利于提升CMOS器件的工作性能。半导体器件包括间隔分布的N型环栅晶体管和P型环栅晶体管。N型环栅晶体管包括的有源结构和P型环栅晶体管包括的有源结构均具有源区、漏区以及位于源区和漏区之间的至少一层纳米结构。P型环栅晶体管包括的至少一层纳米结构被P型环栅晶体管包括的栅堆叠结构覆盖的部分为沟道部,P型环栅晶体管包括的至少一层纳米结构被P型环栅晶体管包括的栅极侧墙覆盖的部分为连接部。沟道部内的锗含量分别大于连接部内的锗含量、以及N型环栅晶体管包括的至少一层纳米结构内的锗含量。

技术研发人员:李永亮,赵飞

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!