一种抗单粒子辐照效应的MOSFET器件及其制作方法

本发明涉及半导体器件,尤其涉及一种抗单粒子辐照效应的mosfet器件及其制作方法。

背景技术:

1、碳化硅(silicon carbide,sic)作为第三代半导体材料,拥有宽禁带、高击穿场强和高热导率等优点,在高频、高压大功率领域有着广泛的应用前景。新一代航天器对能源转换效率、体积和重量均提出了更高的要求,传统硅(silicon,si)器件已经逐渐无法满足应用需求,因此sic功率器件特别是sic mosfet有望成为新一代航天系统的首选。

2、然而,恶劣的空间环境会对sic mosfet带来严重的威胁。在各种高能粒子和宇宙射线的作用下,元器件会发生辐射效应并导致系统出现逻辑和功能错误,是航天器在轨运行故障的重要原因之一。根据电子元件所受辐射损伤的机制和退化规律,辐射效应可分为单粒子效应(single event effect,see)、总剂量效应(total irradiation dose,tid)以及位移损伤效应,其中单粒子效应是影响器件在辐照环境下正常作业的主要威胁因素。单粒子失效模式主要有两种:一种是单粒子烧毁(single event bornout,seb),另一种是单粒子栅穿(single event gate rupture,segr)。

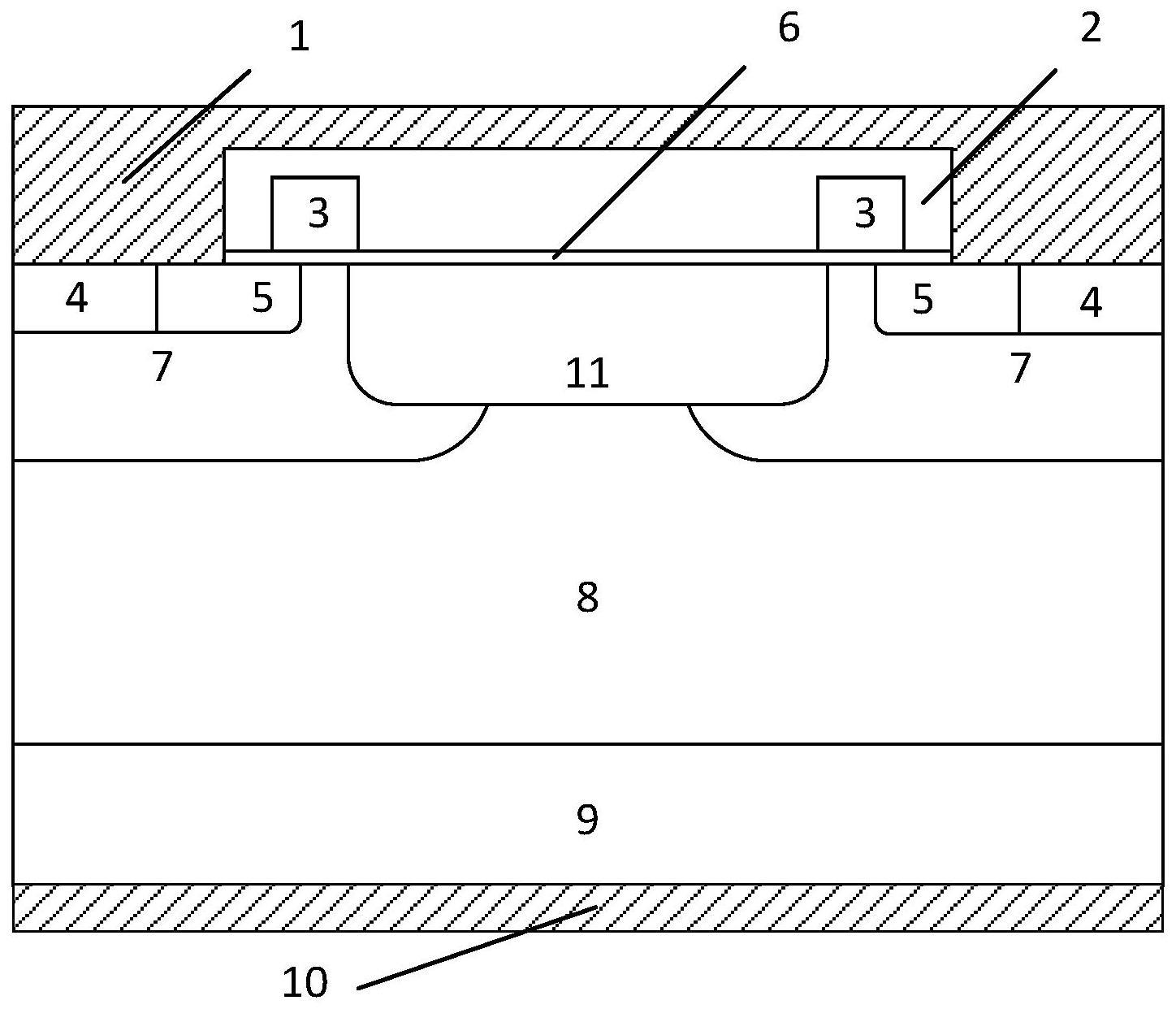

3、目前采用的传统sic mosfet器件结构如图1所示,由于存在固有的栅氧介质和寄生三极管结构,在单粒子辐照下,传统sic mosfet在较低漏极偏压下会发生栅极氧化层损坏从而造成栅极漏电流增加和器件长期可靠性降低,在较高的漏极偏压下会直接发生器件烧毁失效。为了保证器件在空间中的长期稳定工作,需要对sic mosfet的抗单粒子能力进行加固设计。

技术实现思路

1、鉴于上述的分析,本发明旨在提供一种抗单粒子辐照效应的mosfet器件及其制作方法,用以解决现有的mosfet器件受到单粒子辐照下发生单粒子烧毁和单粒子栅穿,造成器件可靠性降低和失效的问题,着重对器件在单粒子辐照下栅极漏电流增加的问题进行了器件的加固设计。

2、本发明的目的主要是通过以下技术方案实现的:

3、一方面,本发明提供了一种抗单粒子辐照的mosfet器件,包括:

4、衬底;

5、位于所述衬底底部的漏极;

6、位于所述衬底上的外延层;

7、位于所述外延层中、靠近上表面且呈轴对称的两个p基区;

8、位于所述外延层中,且与两个p基区均有重叠的注入区;

9、位于所述p基区中的源区和短路区;

10、位于所述外延层上表面的栅极绝缘介质层;

11、位于所述栅极绝缘介质层上的栅极;

12、位于所述栅极绝缘介质层和所述栅极上的层间介质;

13、位于所述层间介质、所述短路区和部分所述源区上的电极。

14、可选地,所述栅极为分隔栅极。

15、可选地,所述分隔栅极与所述注入区重叠区域的宽度为0.05~0.2μm。

16、可选地,所述分隔栅极与所述源区重叠区域的宽度为0.05~0.5μm。

17、另一方面,本发明还提供了一种抗单粒子辐照的mosfet器件的制作方法,包括以下步骤:

18、在衬底上形成外延层;

19、在外延层中形成呈轴对称的两个p基区;

20、在外延层中形成与两个p基区均有重叠的注入区;

21、在p基区中形成源区和短路区;

22、在外延层的上表面形成栅极绝缘介质层;

23、在栅极绝缘介质层上形成分隔栅极;

24、在栅极绝缘介质层和分隔栅极上形成层间介质;

25、形成源极和漏极,得到抗单粒子辐照的mosfet器件。

26、可选地,所述注入区位于外延层中、靠近外延层的上表面处。

27、可选地,所述注入区的注入宽度为0.5~4.0μm,所述注入区的注入深度比所述p基区的注入深度小0.1~1.5μm。

28、可选地,所述注入区与所述p基区的重叠区域宽度为0.1~1.0μm。

29、可选地,所述在栅极绝缘介质层上形成分隔栅极,包括:

30、在栅极绝缘介质层上淀积多晶硅,形成栅极;

31、去除部分多晶硅,未被去除的多晶硅形成分隔栅极。

32、可选地,所注入区的峰值掺杂浓度为1×1016~5×1019cm-3。

33、与现有技术相比,本发明至少可实现如下有益效果之一:

34、1、本发明在外延层中设置与两个p基区均有重叠的注入区(jfet区),上述设置与p型基区和外延层形成的pn结一起,可以阻止载流子在jfet区的移动,减少在单粒子过程中栅极绝缘介质层受到的冲击,从而提高器件的抗单粒子性能。进一步地,通过控制注入区的注入深度比p基区的注入深度小0.1~1.5μm,并且通过控制注入区与p基区重叠区域的宽度为0.1~1.0μm,进一步提高了器件的抗单粒子性能。

35、2、常规栅极结构为连续型(参见图1),上述连续型的栅极结构存在jfet区上方易受单粒子效应影响的缺陷,导致栅极漏电流增加,使得器件受损,可靠性低。本发明创新性地提出采用分隔栅极结构,减轻了常规栅极结构中jfet区上方受单粒子效应的影响,使得器件在单粒子辐照过程中的栅极漏电流小,器件可靠性大幅提高。具体而言,可以将栅极漏电流降为原来的10%以下。

36、3、本发明的分隔栅极结构的栅极电容更小,减小因此带来的器件的米勒效应,可以增强器件的动态特性。

37、4、本发明通过在外延层中设置与两个p基区均有重叠的注入区,使得形成的jfet区可以减小传统sic mosfet器件中的jfet区电阻,减小器件的整体电阻,从而提高器件的电流密度并减小导通损耗。

38、5、本发明通过将分隔栅极与注入区重叠区域的宽度控制为0.05~0.2μm,使得栅极的长度略长于mosfet器件的沟道长度,从而能够实现器件的电学特性。

39、6、本发明与传统mosfet器件制备工艺兼容性好,无需特别调整sic工艺即可实现量产。

40、本发明中,上述各技术方案之间还可以相互组合,以实现更多的优选组合方案。本发明的其他特征和优点将在随后的说明书中阐述,并且,部分优点可从说明书中变得显而易见,或者通过实施本发明而了解。

技术特征:

1.一种抗单粒子辐照的mosfet器件,其特征在于,包括:

2.根据权利要求1所述的mosfet器件,其特征在于,所述栅极为分隔栅极。

3.根据权利要求2所述的mosfet器件,其特征在于,所述分隔栅极与所述注入区重叠区域的宽度为0.05~0.2μm。

4.根据权利要求2所述的mosfet器件,其特征在于,所述分隔栅极与所述源区重叠区域的宽度为0.05~0.5μm。

5.一种抗单粒子辐照的mosfet器件的制作方法,其特征在于,包括以下步骤:

6.根据权利要求5所述的制作方法,其特征在于,所述注入区位于外延层中、靠近外延层的上表面处。

7.根据权利要求6所述的制作方法,其特征在于,所述注入区的注入宽度为0.5~4.0μm,所述注入区的注入深度比所述p基区的注入深度小0.1~1.5μm。

8.根据权利要求6所述的制作方法,其特征在于,所述注入区与所述p基区的重叠区域宽度为0.1~1.0μm。

9.根据权利要求5-8任一项所述的制作方法,其特征在于,所述在栅极绝缘介质层上形成分隔栅极,包括:

10.根据权利要求9所述的制作方法,其特征在于,所注入区的峰值掺杂浓度为1×1016~5×1019cm-3。

技术总结

本发明涉及一种抗单粒子辐照效应的MOSFET器件及其制作方法,属于半导体器件技术领域,解决了现有的MOSFET器件受到单粒子辐照下发生单粒子烧毁和单粒子栅穿,造成器件可靠性降低和失效的问题,着重对器件在单粒子辐照下栅极漏电流增加的问题进行了器件的加固设计。该制作方法包括:在衬底上形成外延层;在外延层中形成呈轴对称的两个P基区;在外延层中形成与两个P基区均有重叠的注入区;在P基区中形成源区和短路区;在外延层的上表面形成栅极绝缘介质层;在栅极绝缘介质层上形成分隔栅极;在栅极绝缘介质层和分隔栅极上形成层间介质;形成源极和漏极,得到抗单粒子辐照的MOSFET器件。本发明大幅提高了MOSFET器件在恶劣的空间环境中的长期可靠性。

技术研发人员:邱乐山,白云,刘新宇,汤益丹,郝继龙,杨成樾,田晓丽

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!