芯片、测试机台、芯片内部比较器的校准方法及相关设备与流程

本发明适用于芯片工艺,尤其涉及一种芯片、测试机台、芯片内部比较器的校准方法及相关设备。

背景技术:

1、由于晶圆制造时,尺寸、掺杂浓度等的偏差,芯片等集成电路(integratedcircuit chip,ic)被制造出来后,内部的差分对管可能存在一定的失配,导致比较器出现一定的偏差(offset)。在部分高精度要求的芯片中,为使产品的参数性能达到预期且具备良好的一致性,在出货前需要进行比较器的校准。校准的原理是加入一个可以人为调节的阈值偏差,通过这个阈值偏差抵消制造中产生的实际偏差。

2、相关技术一般是在芯片内部将比较器的两个输入脚短起来,然后在外部测试机台以一定逻辑来操作芯片的寄存器来调整阈值偏差,再依据比较器输出的翻转情况来确定是否校准完成,如图1所示。

3、基于图1的校准环境,相关技术通常使用以下两种方式进行比较器校准:

4、一、从外部测试机台操作芯片寄存器的逻辑是遍历,通过操作寄存器的值,使其从全0遍历到全1(或从全1遍历到全0),并每次确定比较器输出,当比较器输出翻转后中止遍历。

5、二、述机台操作ic寄存器的逻辑是“二分法”,机台根据比较器输出的翻转情况,决定寄存器每个bit是0还是1。这个做法大大缩短了测试时间,寄存器有几个bit就调整几次寄存器。

6、然而,上述方法具有以下问题:

7、对于方式一,由于芯片夹具和机台之间有很长的软排线连接,容易被干扰,所以通信速率不会很高,并且遍历操作有大量的修改寄存器的通信过程,5bit寄存器最差情况需要32次修改寄存器的通信,平均情况也需要16次通信,寄存器每增加1bit,通信时间都会成倍增长,此外,io端口也是通过很长路径连接到机台的,为了保证结果准确,相关技术需要加入一段防抖(debounce)时间,单次防抖时间固定,总防抖时间和寄存器调整次数成正比,因此寄存器每增加1bit,总防抖时间也会成倍增长;

8、对于方式二,由于芯片的比较器往往有一定滞回的特性,在二分法中是依靠比较器来回翻转来确定每个寄存器bit的值的,这就导致最后得出的值未必是期望的比较器刚刚翻转的阈值,因此造成了偏差,在一些滞回做得比较大的比较器上,这个偏差甚至可以高达有十多个step。

9、因此,有必要提出一种新的芯片比较器的校准系统和方法来解决上述问题。

技术实现思路

1、本发明提供一种芯片、测试机台、芯片内部比较器的校准方法及相关设备,旨在解决现有技术对于芯片内部比较器校准的方法受限于排线连接及二分遍历逻辑导致的等待时间长、通信时间长的技术问题。

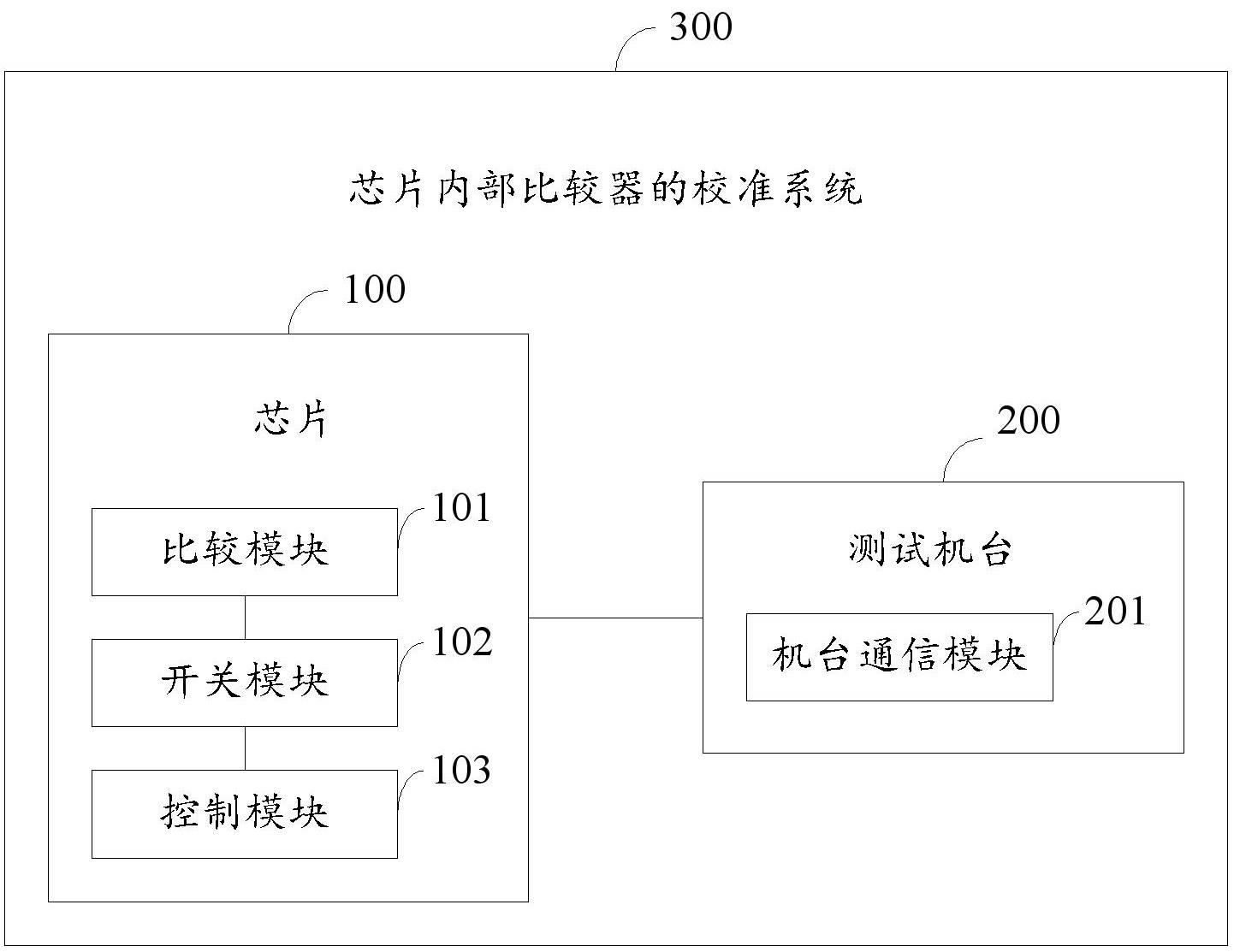

2、第一方面,本发明实施例提供一种芯片,可由一个测试机台进行比较器校准,所述芯片包括比较模块、开关模块、控制模块,所述比较模块包括待校准的比较器,所述比较模块的输入端连接所述开关模块,所述比较模块的输出端连接所述控制模块,其中:

3、所述开关模块用于获取校准开始信号,并根据所述校准开始信号将所述比较器的输入端进行短路连接,以及根据校准完成信号将比较器的输入端进行开路连接;其中,所述校准开始信号为所述测试机台发出,所述校准完成信号由所述控制模块在所述比较器的输出发生翻转时产生;

4、所述控制模块用于将芯片的寄存器值进行遍历输出至所述比较器,并判断所述寄存器值是否使所述比较器的输出发生翻转:若是,则释放所述校准完成信号至所述开关模块和所述测试机台,并保存使所述比较器的输出发生翻转的所述寄存器值,以完成所述比较器的校准;若否,则持续进行所述寄存器值的遍历输出;

5、所述比较模块用于根据所述寄存器值调整所述比较器的偏差值。

6、更进一步地,所述开关模块为开路连接时,所述比较器的输出保持不变。

7、更进一步地,所述开关模块为mos管,所述mos管的源极、漏极分别连接所述比较器的输入端,所述mos管的栅极连接所述控制模块的输出端。

8、更进一步地,所述控制模块包含第一输出端和第二输出端,所述第一输出端连接所述开关模块以传输所述校准完成信号,所述第二输出端连接所述比较模块以传输所述寄存器值。

9、第二方面,本发明实施例还提供一种测试机台,用于对芯片中的比较器进行校准,所述测试机台包括机台通讯模块,所述机台通信模块用于根据指令发出校准开始信号至所述芯片,并接收所述芯片返回的校准结束信号。

10、第三方面,本发明实施例还提供一种芯片内部比较器的校准系统,所述校准系统包括如上任一项所述的芯片及测试机台。

11、第四方面,本发明实施例还提供一种芯片内部比较器的校准方法,所述校准方法基于如上任一项所述的芯片实现,所述校准方法包括以下步骤:

12、s11、在芯片的开关模块中接收所述校准开始信号,并将比较器的输入端进行短路连接;

13、s12、在芯片的控制模块中将芯片的寄存器值进行遍历输出至所述比较器;

14、s13、在芯片的控制模块中判断所述寄存器值是否使所述比较器的输出发生翻转:若是,则释放校准完成信号,并执行步骤s14,若否,返回步骤s12;

15、s14、在芯片的控制模块中终止所述寄存器值的遍历输出,根据所述校准完成信号将比较器的输入端进行开路连接,并保存使所述比较器的输出发生翻转的所述寄存器值,以完成所述比较器的校准。

16、第五方面,本发明实施例还提供一种芯片内部比较器的校准方法,所述校准方法基于如上所述的测试机台实现,所述校准方法包括以下步骤:

17、s21、在测试机台的机台通信模块中输入指令,以向包含待校准比较器的芯片发出校准开始信号,以开始参数校准;

18、s22、通过所述机台通信模块接收校准结束信号,并结束参数校准,所述校准结束信号为所述比较器校准完成时发出。

19、第六方面,本发明实施例还提供一种计算机设备,包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现如上任一项所述的芯片内部比较器的校准方法中的步骤。

20、第七方面,本发明实施例还提供一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如上任一项所述的芯片内部比较器的校准方法中的步骤。

21、本发明所达到的有益效果,在于提出了一种基于芯片内部电路实现的比较器校准方法以及对应的芯片及测试机台,本发明的校准方法中测试机台与芯片通信的内容少、通信时间短,并且,基于顺序遍历的逻辑实现的校准方案不仅能够减少芯片内部电路的开发负担,还能够提高校准准确度、缩短校准时间。

技术特征:

1.一种芯片,可由一个测试机台进行比较器校准,其特征在于,所述芯片包括比较模块、开关模块、控制模块,所述比较模块包括待校准的比较器,所述比较模块的输入端连接所述开关模块,所述比较模块的输出端连接所述控制模块,其中:

2.如权利要求1所述的芯片,其特征在于,所述开关模块为开路连接时,所述比较器的输出保持不变。

3.如权利要求1所述的芯片,其特征在于,所述开关模块为mos管,所述mos管的源极、漏极分别连接所述比较器的输入端,所述mos管的栅极连接所述控制模块的输出端。

4.如权利要求1所述的芯片,其特征在于,所述控制模块包含第一输出端和第二输出端,所述第一输出端连接所述开关模块以传输所述校准完成信号,所述第二输出端连接所述比较模块以传输所述寄存器值。

5.一种测试机台,用于对芯片中的比较器进行校准,其特征在于,所述测试机台包括机台通讯模块,所述机台通信模块用于根据指令发出校准开始信号至所述芯片,并接收所述芯片返回的校准结束信号。

6.一种芯片内部比较器的校准系统,其特征在于,所述校准系统包括如权利要求1-4任一项所述的芯片及如权利要求5所述的测试机台。

7.一种芯片内部比较器的校准方法,所述校准方法基于权利要求1-4任一项所述的芯片实现,其特征在于,所述校准方法包括以下步骤:

8.一种芯片内部比较器的校准方法,所述校准方法基于权利要求5所述的测试机台实现,其特征在于,所述校准方法包括以下步骤:

9.一种计算机设备,其特征在于,包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现如权利要求7或8所述的芯片内部比较器的校准方法中的步骤。

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如权利要求7或8所述的芯片内部比较器的校准方法中的步骤。

技术总结

本发明适用于芯片工艺技术领域,尤其涉及一种芯片、测试机台、芯片内部比较器的校准方法及相关设备。本发明提出了一种基于芯片内部电路实现的比较器校准方法以及对应的芯片及测试机台,本发明的校准方法中测试机台与芯片通信的内容少、通信时间短,并且,基于顺序遍历的逻辑实现的校准方案不仅能够减少芯片内部电路的开发负担,还能够提高校准准确度、缩短校准时间。

技术研发人员:文浩飞

受保护的技术使用者:深圳市思远半导体有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!