一种三维集成电路的制备方法及三维集成电路与流程

本申请涉及半导体器件,具体地,涉及一种三维集成电路的制备方法及三维集成电路。

背景技术:

1、集成电路(integrated circuit,简称ic)是一种微型电子器件或部件。电子产品目前正在朝小型化、高密度化、高可靠性、低功耗方向发展,因此,集成电路/芯片发展方向也是小型化、高密度化、高可靠性、低功耗。为了缩小芯片尺寸,业界发明了多层芯片堆叠封装技术。

2、开始时,堆叠封装是把多个芯片裸片堆叠放置在一起,把芯片之间的信号通过键合(bonding)技术连结,组成内部的完整系统,再把外部信号通过封装引脚外连,最后封装成为一个完整芯片。

3、后来,业界发明了硅通孔(tsv)技术,堆叠的芯片裸片之间的信号是通过tsv连接,形成了更加紧凑的多芯片堆叠的3d封装芯片。这种3d封装芯片是在封装阶段通过多层芯片裸片堆叠封装形成的,从芯片制造角度看,这种3d封装芯片只能看作是伪3d芯片。

4、3d封装芯片存在如下缺陷:

5、1、减薄技术面临的主要挑战是超薄化工艺所要求的<50um的减薄能力,没有支撑的减薄硅片在组装后会发生严重的翘曲,与基板之间的互连(微凸点)上会产生较大的残余应力,从而导致器件结构的可靠性问题。

6、2、因为cu易于氧化并在高温下容易形成各种氧化物(cuo和cu2o),需要高真空度和高洁净度的cu-cu混合键合工艺。

7、3、不同芯片裸晶在封装过程中的对准精度较低,封装过程之中,裸晶可能会有位移,导致钻孔或脚位没对准,布线和互连间距受覆盖精度的影响被限制在几个微米。intel最先进的qmc工艺的pitch为3um,因此键合的i/o数目受到pitch的限制,无法再提高集成度。

8、4、3d封装由大量不同的材料组成,这些材料具有不同的材料特性,如热膨胀系数(cte)、热导率、电导率及弹性模量等,这会在芯片上产生巨大的热-机械力,并导致芯片与封装相互作用(cpi),从而发生低k值电介质材料开裂、金属结构脱落等现象。另外,封装自身可能也会发生严重翘曲,从而增加了额外的应力,尤其是对于面积较大的封装。

9、因此,传统的3d封装芯片的封装技术不能适应芯片的发展方向,是本领域技术人员急需要解决的技术问题。

10、在背景技术中公开的上述信息仅用于加强对本申请的背景的理解,因此其可能包含没有形成为本领域普通技术人员所知晓的现有技术的信息。

技术实现思路

1、本申请实施例提供了一种三维集成电路的制备方法及三维集成电路,以解决传统的3d封装芯片的封装技术不能适应芯片的发展方向的技术问题。

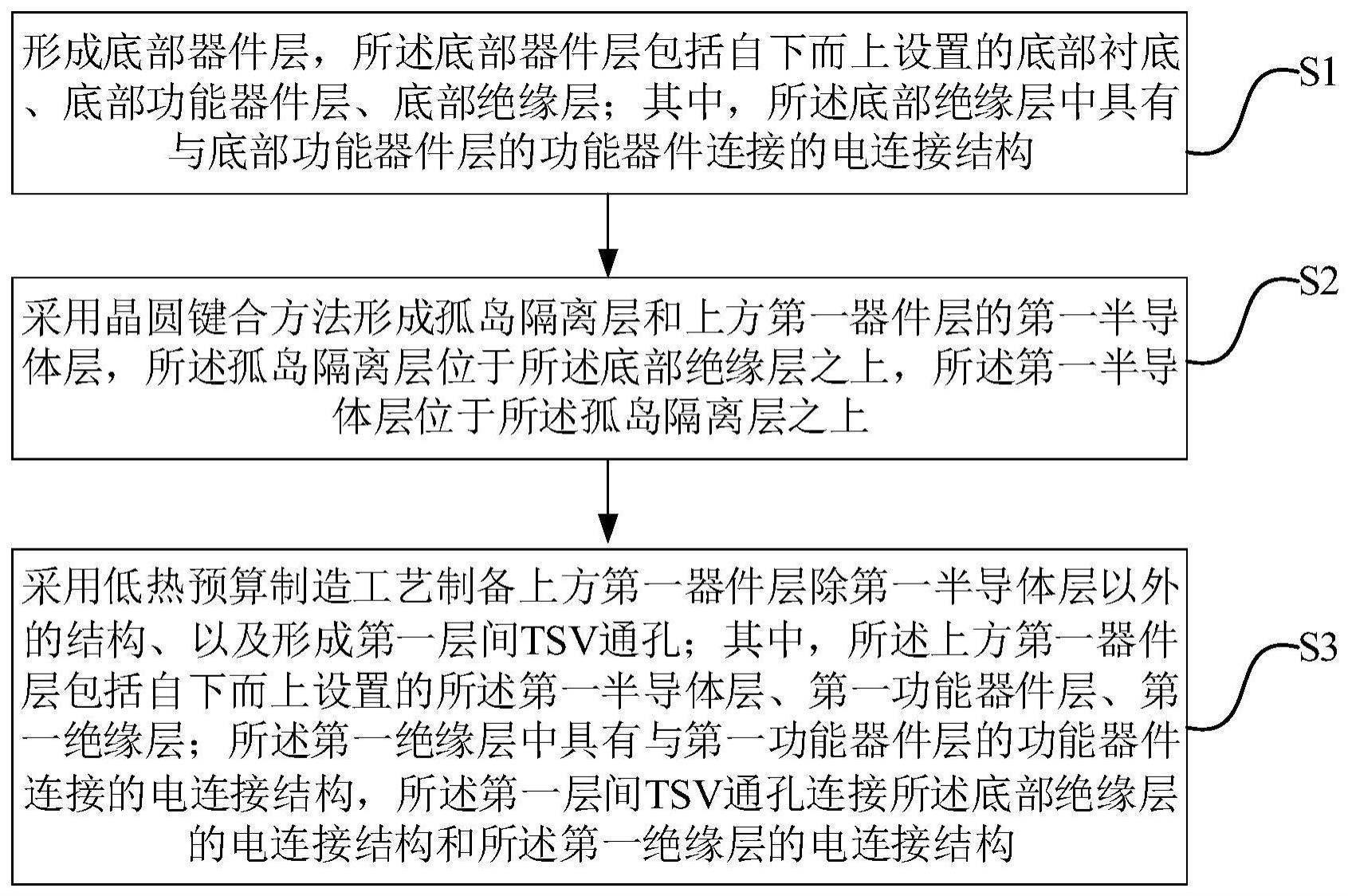

2、本申请实施例提供了一种三维集成电路的制备方法,包括如下步骤:

3、步骤s1:形成底部器件层,所述底部器件层包括自下而上设置的底部衬底、底部功能器件层、底部绝缘层;其中,所述底部绝缘层中具有与底部功能器件层的功能器件连接的电连接结构;

4、步骤s2:采用晶圆键合方法形成孤岛隔离层和上方第一器件层的第一半导体层,所述孤岛隔离层位于所述底部绝缘层之上,所述第一半导体层位于所述孤岛隔离层之上;

5、步骤s3:制备上方第一器件层除第一半导体层以外的结构、以及形成第一层间tsv通孔;其中,所述上方第一器件层包括自下而上设置的所述第一半导体层、第一功能器件层、第一绝缘层;所述第一绝缘层中具有与第一功能器件层的功能器件连接的电连接结构,所述第一层间tsv通孔连接所述底部绝缘层的电连接结构和所述第一绝缘层的电连接结构。

6、本申请实施例还提供一种三维集成电路,采用上述三维集成电路的制备方法制备形成。

7、本申请实施例由于采用以上技术方案,具有以下技术效果:

8、三维集成电路的制备方法,本质上制备一个真正的3d芯片,只有一个衬底就是底部衬底。第一半导体层厚度不仅是小于所述底部衬底的厚度,而且是远远小于底部衬底的厚度。底部器件层仅仅是一个三维集成电路中的层结构,上方第一器件层是底部器件层上方的层结构,即底部器件层和上方第一器件层在制造时垂向排列形成,两者通过孤岛隔离层键合。孤岛隔离层键合的连接方式,一方面方便的实现了底部器件层和上方第一器件层之间的连接,另一方面,也将底部器件层和上方第一器件层进行了有效的隔离,避免了上方第一器件层向底部器件层的漏电。因此,孤岛隔离层是实现在垂向方向集成底部器件层和上方第一器件层的重要环节。第一层间tsv通孔电连接下方绝缘层的电连接结构和第一绝缘层的电连接结构,实现了底部功能器件层的功能器件和第一功能器件层的功能器件的连接。即实现了实现了三维集成电路在垂向方向的电连接。本申请实施例的三维集成电路的制备方法,不是为了形成3d封装芯片,而是制备一个真正的3d芯片,即三维集成电路。整个三维集成电路只有一个底部衬底,使得整个三维集成电路的垂向高度能够较小,进而整个三维集成电路的尺寸较小;同时也使得三维集成电路的衬底成本较低。

技术特征:

1.一种三维集成电路的制备方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的三维集成电路的制备方法,其特征在于,三维集成电路还包括自上方第一器件层的上方依次排列的上方第二器件层、……、上方第n器件层;其中,n的取值范围为大于等于2小于等于50;

3.根据权利要求1或2所述的三维集成电路的制备方法,其特征在于,步骤s1具体包括:

4.根据权利要求3所述的三维集成电路的制备方法,其特征在于,所述氧化物绝缘层中的电连接结构完全被氧化物绝缘层包裹,以及所述低介电常数绝缘层中的电连接结构完全被低介电常数绝缘层包裹的结构,通过控制三维集成电路的曝光区域位于三维集成电路的侧面边缘之内实现。

5.根据权利要求4所述的三维集成电路的制备方法,其特征在于,步骤s2具体包括:

6.根据权利要求5所述的三维集成电路的制备方法,其特征在于,采用低热预算制造工艺制备上方第一器件层除第一半导体层以外的结构、以及形成第一层间tsv通孔;

7.根据权利要求6所述的三维集成电路的制备方法,其特征在于,步骤s3具体还包括如下步骤:

8.根据权利要求7所述的三维集成电路的制备方法,其特征在于,步骤s3具体还包括如下步骤:

9.根据权利要求8所述的三维集成电路的制备方法,其特征在于,步骤s3具体还包括如下步骤:

10.根据权利要求9所述的三维集成电路的制备方法,其特征在于,步骤s3-5中形成第一层间tsv通孔的步骤,具体包括:

11.根据权利要求5所述的三维集成电路的制备方法,其特征在于,所述第一薄硅层为透明的所述第一薄硅层。

12.根据权利要求1所述的三维集成电路的制备方法,其特征在于,所述第一层间tsv通孔内的导电物质的熔点高于低热预算闪光毫秒退火工艺的退火温度;

13.根据权利要求10所述的三维集成电路的制备方法,其特征在于,步骤s1-4,还包括如下步骤:

14.根据权利要求13所述的三维集成电路的制备方法,其特征在于,步骤s3-7,还包括如下步骤:

15.一种三维集成电路,其特征在于,通过权利要求1至14任一所述的三维集成电路的制备方法制备形成。

技术总结

本申请实施例提供了一种三维集成电路的制备方法及三维集成电路。制备方法,包括如下步骤:步骤S1:形成底部器件层;底部绝缘层中具有电连接结构;步骤S2:采用晶圆键合方法形成孤岛隔离层和上方第一器件层的第一半导体层,孤岛隔离层位于底部绝缘层之上,第一半导体层位于孤岛隔离层之上;步骤S3:制备上方第一器件层除第一半导体层以外的结构、以及形成第一层间TSV通孔;第一绝缘层中具有电连接结构,第一层间TSV通孔连接底部绝缘层的电连接结构和第一绝缘层的电连接结构。本申请实施例了解决传统的3D封装芯片的封装技术不能适应芯片的发展方向的技术问题。

技术研发人员:张耀辉

受保护的技术使用者:苏州华太电子技术股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!