一种半导体器件的T型栅及其制备方法与流程

本发明属于半导体器件,具体涉及一种半导体器件的t型栅及其制备方法。

背景技术:

1、目前,以gaas、gan为代表的单片微波集成电路(mmic)已广泛用于电子对抗、雷达制导等武器装备及民用卫星和通讯系统,尤其gan材料由于其宽禁带、高电子饱和漂移速度、高击穿场强等优势,在武器装备、空间应用、无线通信等领域具有重要的应用价值和市场价值。更高频率和更大带宽是mmic的重要发展方向之一,工作频段从c、x波段逐渐向ku、ka等更高频段发展。mmic的核心器件就是以hemt为代表的场效应晶体管(filed effecttransistor),hemt的栅极的制作对器件的截止频率和寄生效应具有至关重要的影响。缩小栅长是提高频率特性的最直接方法,栅长越小,器件的截止频率越高,但是栅长缩小,带来栅电阻增加,为了兼顾栅长缩小和尽力降低栅电阻,底部长度小而截面积大的t型栅结构得到了广泛的应用,典型的栅长从亚微米级到纳米级,典型的工艺节点包括0.5µm,0.25µm和0.15µm。

2、作为现有技术,cn102569054a和cn108807162a均公开了一种t型栅的制备方法。但是,现有的t型栅的光刻制备工艺主要采用i-line(i线)步进式光刻、duv(深紫外线)步进式光刻和电子束曝光工艺,其中,传统i-line步进式光刻机可实现的最小线宽一般是0.35μm或0.28μm,更小线条的t型栅光刻则需要采用duv步进式光刻机和电子束光刻机进行制备。受限于现有i-line光刻的工艺线宽,目前0.25µm及以下栅长的t型栅通常采用电子束曝光机或者深紫外曝光机制作,两者设备成本和工艺大幅提高,而且电子束曝光机制备效率大幅降低。因此,duv步进式光刻机和电子束光刻机的价格较高且制备效率较低一直是其制约因素。

技术实现思路

1、本发明的目的是提供一种半导体器件的t型栅及其制备方法,能够降低制备成本,提高制备效率。

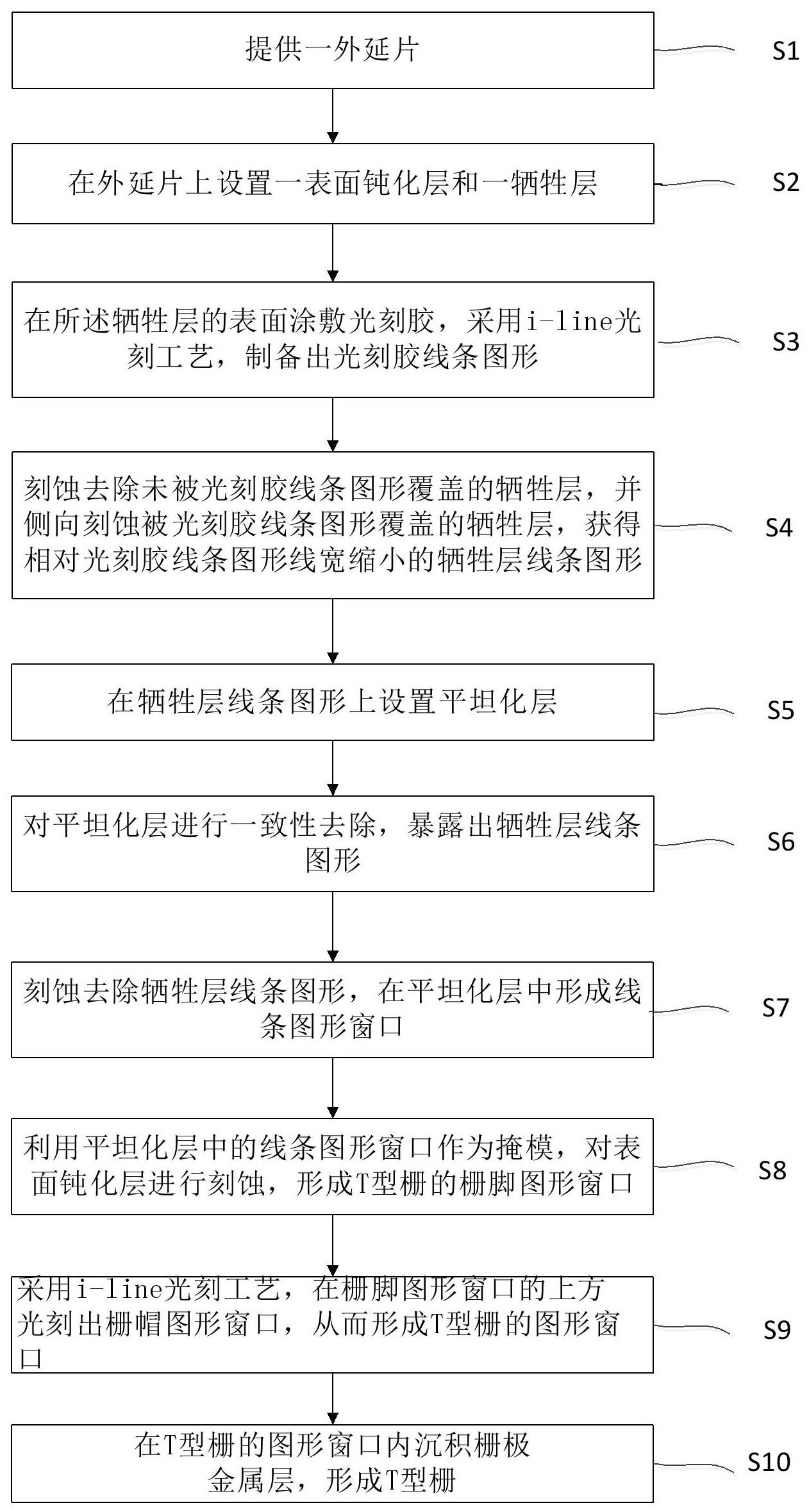

2、本发明的一个方面提供一种半导体器件的t型栅制备方法,其特征在于,包括:

3、步骤s1:提供一外延片;

4、步骤s2:在外延片上设置一表面钝化层和一牺牲层;

5、步骤s3:在所述牺牲层的表面涂敷光刻胶,采用i-line光刻工艺,制备出光刻胶线条图形;

6、步骤s4:刻蚀去除未被光刻胶线条图形覆盖的牺牲层,并侧向刻蚀被光刻胶线条图形覆盖的牺牲层,获得相对光刻胶线条图形线宽缩小的牺牲层线条图形;

7、步骤s5:在牺牲层线条图形上设置平坦化层;

8、步骤s6:对平坦化层进行一致性去除,暴露出牺牲层线条图形;

9、步骤s7:刻蚀去除牺牲层线条图形,在平坦化层中形成线条图形窗口;

10、步骤s8:利用平坦化层中的线条图形窗口作为掩模,对表面钝化层进行刻蚀,形成t型栅的栅脚图形窗口;

11、步骤s9:采用i-line光刻工艺,在栅脚图形窗口的上方光刻出栅帽图形窗口,从而形成t型栅的图形窗口;

12、步骤s10:在t型栅的图形窗口内沉积栅极金属层,形成t型栅。

13、优选地,在步骤s3中,所制备的光刻胶线条图形的线宽为0.28µm~2µm。

14、优选地,在步骤s4中,所获得的牺牲层线条图形的线宽为0.05µm~1µm。

15、优选地,在步骤s5中,对牺牲层线条图形的间隙进行填充,使得牺牲层线条图形间隙处的平坦化层的厚度大于牺牲层线条图形上方的平坦化层厚度。

16、优选地,在步骤s6中,通过化学机械抛光或干法刻蚀对平坦化层进行一致性去除。

17、优选地,在步骤s7和s8中所形成的线条图形窗口和栅脚图形窗口的截面是矩形、正梯形、倒梯形中的任一种或组合图形,图形线宽为0.05µm~1µm。

18、优选地,在步骤s9中,光刻出的栅帽图形窗口的线宽大于栅脚图形窗口的线宽,栅帽图形窗口的线宽为0.28µm~2µm。

19、优选地,在步骤s2中,在外延片的表面采用lpcvd、pecvd、ald、mocvd中的任一方式沉积一层或多层的氧化物、氮化物或氮氧化物作为所述表面钝化层,厚度为20nm~200nm,所述牺牲层为金属材料或介质材料,厚度为20nm~200nm。

20、优选地,在步骤s10中,所形成的t型栅是由栅脚和栅帽组成的t型电极结构,栅脚线宽为0.05µm~1µm,栅帽线宽为0.28µm~2µm。

21、本发明的另一个方面提供半导体器件的t型栅,通过上述的方法制备得到。

22、根据本发明上述方面的半导体器件的t型栅及其制备方法,能够降低制备成本,提高制备效率。

技术特征:

1.一种半导体器件的t型栅制备方法,其特征在于,包括:

2.如权利要求1所述的方法,其特征在于,在步骤s3中,所制备的光刻胶线条图形的线宽为0.28µm~2µm。

3.如权利要求1或2所述的方法,其特征在于,在步骤s4中,所获得的牺牲层线条图形的线宽为0.05µm~1µm。

4.如权利要求1或2所述的方法,其特征在于,在步骤s5中,对牺牲层线条图形的间隙进行填充,使得牺牲层线条图形间隙处的平坦化层的厚度大于牺牲层线条图形上方的平坦化层厚度。

5.如权利要求1或2所述的方法,其特征在于,在步骤s6中,通过化学机械抛光或干法刻蚀对平坦化层进行一致性去除。

6.如权利要求1或2所述的方法,其特征在于,在步骤s7和s8中所形成的线条图形窗口和栅脚图形窗口的截面是矩形、正梯形、倒梯形中的任一种或组合图形,图形线宽为0.05µm~1µm。

7.如权利要求1或2所述的方法,其特征在于,在步骤s9中,光刻出的栅帽图形窗口的线宽大于栅脚图形窗口的线宽,栅帽图形窗口的线宽为0.28µm~2µm。

8.如权利要求1或2所述的方法,其特征在于,在步骤s2中,在外延片的表面采用lpcvd、pecvd、ald、mocvd中的任一方式沉积一层或多层的氧化物、氮化物或氮氧化物作为所述表面钝化层,厚度为20nm~200nm,所述牺牲层为金属材料或介质材料,厚度为20nm~200nm。

9.如权利要求1或2所述的方法,其特征在于,在步骤s10中,所形成的t型栅是由栅脚和栅帽组成的t型电极结构,栅脚线宽为0.05µm~1µm,栅帽线宽为0.28µm~2µm。

10.一种半导体器件的t型栅,其特征在于,通过权利要求1-9中任一项所述的方法制备得到。

技术总结

本发明公开了一种半导体器件的T型栅及其制备方法,所述方法包括:在外延片上设置表面钝化层和牺牲层;在牺牲层的表面涂敷光刻胶,采用i‑line光刻工艺制备出光刻胶线条图形;刻蚀去除未被光刻胶线条图形覆盖的牺牲层,并侧向刻蚀被光刻胶线条图形覆盖的牺牲层,获得线宽缩小的牺牲层线条图形;在牺牲层线条图形上设置平坦化层;对平坦化层进行一致性去除,暴露出牺牲层线条图形;刻蚀去除牺牲层线条图形,形成线条图形窗口;利用线条图形窗口作为掩模,对表面钝化层进行刻蚀形成栅脚图形窗口;采用i‑line光刻工艺光刻出栅帽图形窗口,形成T型栅的图形窗口;在T型栅的图形窗口内沉积栅极金属层,形成T型栅。本发明能够降低制备成本,提高制备效率。

技术研发人员:董鹏,边旭明,廖梦雅,徐浩,杨云畅,曹佳,王琦

受保护的技术使用者:北京无线电测量研究所

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!