一种提升SiCMOSFET器件崩溃电压的方法与流程

本发明涉及半导体,尤其涉及一种提升sic mosfet器件崩溃电压的方法。

背景技术:

1、目前市场上已知的sic mosfet相对比较成熟的技术,芯片崩溃电压可达650v至1200v的范围,现在用在新能源汽车内的车载充电器(on board char ging,obc)、高压牵引逆变器(hv traction invertor)以及高压直流转换器(hv dc/dc)都会用到sic mosfet器件,串联电池模块的高压直流转换器,会随着电动车的续航能力增加需求,增加更多串连电池模块而需要更高压的直流转换器模块,转换器模块内的sic mosfet芯片的崩溃电压需求提升950v至1500v。整个高压直流转换器模块的崩溃电压须大幅提升,必须从sic mosfe t芯片内的最基本的单元晶体管器件设计上去改良提升才能让整个模块的崩溃电压提升。

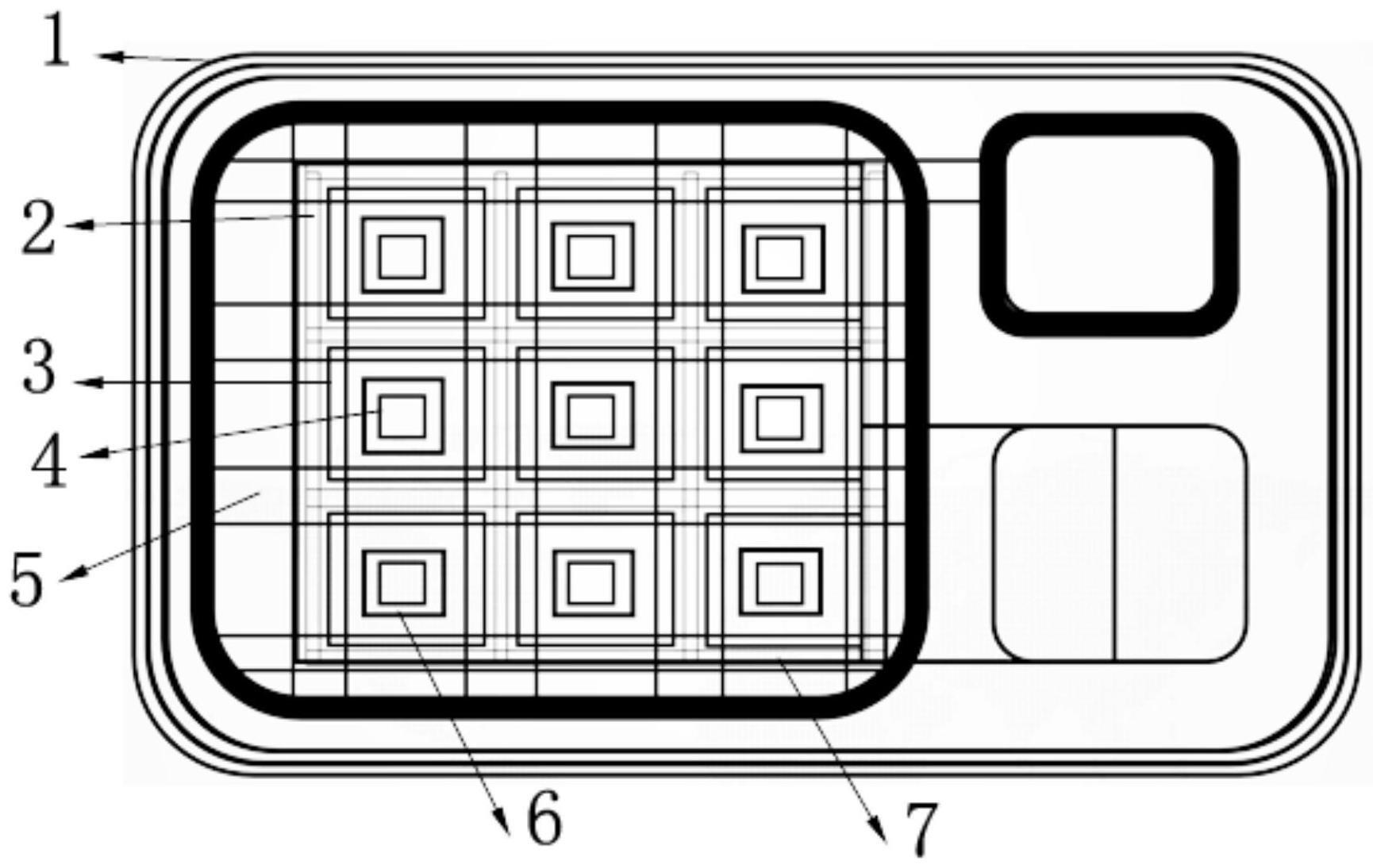

2、现有的sic mosfet器件的结构设计如图1所示,其栅极为长方形,多个mosfet器件的栅极用源极接触sc并联在一起,mosfet器件的源极的区域透过源极接触跨接在器件的栅极两侧,再同时并连接出来,mosfet器件的漏极在器件的底部,未在图1的俯视结构示意图表示出来。增大其沟道区域的面积对于提升模块的崩溃电压来说至关重要。

技术实现思路

1、本发明的目的在于提高现有sic mosfet器件崩溃电压,提供了一种提升sicmosfet器件崩溃电压的方法。

2、本发明的目的是通过以下技术方案来实现的:

3、主要提供一种提升sic mosfet器件崩溃电压的方法,所述方法包括:

4、将多个mosfet管并联,将sic mosfet器件的沟道区域由现有垂直的排列结构,重新设计成垂直和水平结构共存。

5、作为一优选项,一种提升sic mosfet器件崩溃电压的方法,所述将sic mosfet器件的沟道区域由现有垂直的排列结构,重新设计成垂直和水平结构共存,包括:

6、将所述mosfet管的栅极设计为方形矩阵列式。

7、作为一优选项,一种提升sic mosfet器件崩溃电压的方法,所述mosfet管包括:

8、sic基板;

9、设于sic基板上方的漂移区;

10、设于漂移区上方的多个p型区域,所述p型区域对称分布;

11、在p型区域中设有n型离子注入层,所述n型离子注入层中设有p型离子注入层;

12、在p型区域的上方设有栅极区,所述栅极区搭设在相邻两个p型区域的n型离子注入层上,通过源极接触分别与所述n型离子注入层、p型离子注入层连接。

13、作为一优选项,一种提升sic mosfet器件崩溃电压的方法,所述p型区域两侧设有保护环。

14、作为一优选项,一种提升sic mosfet器件崩溃电压的方法,所述保护环对称分布。

15、作为一优选项,一种提升sic mosfet器件崩溃电压的方法,所述栅极区通过栅极侧壁与所述源极接触连接。

16、作为一优选项,一种提升sic mosfet器件崩溃电压的方法,所述栅极侧壁为氮化硅薄膜。

17、作为一优选项,一种提升sic mosfet器件崩溃电压的方法,所述sic基板为n+型基板。

18、作为一优选项,一种提升sic mosfet器件崩溃电压的方法,所述漂移区为n-漂移区。

19、作为一优选项,一种提升sic mosfet器件崩溃电压的方法,所述n型离子注入层为n+型。

20、作为一优选项,一种提升sic mosfet器件崩溃电压的方法,所述p型离子注入层为p+型。

21、需要进一步说明的是,上述各选项对应的技术特征在不冲突的情况下可以相互组合或替换构成新的技术方案。

22、与现有技术相比,本发明有益效果是:

23、本发明设计的器件包括多个并联的mosfet管,将sic mosfet器件的沟道区域由现有垂直的排列结构,重新设计成垂直和水平结构共存,将所述mosfet管的栅极为方形矩阵列式,该结构提升mosfet器件沟道的面积,增加器件栅极开关可控的沟道面积再并联多数个mosfet,进而提升整体并联后的等校晶体管的崩溃电压,有别于一般传统硅基mosfet,碳化硅基mosfet器件单位面积的功率密度更高,适用于1200v~1500v高压器件开关。

技术特征:

1.一种提升sic mosfet器件崩溃电压的方法,其特征在于,所述方法包括:

2.根据权利要求1所述的一种提升sic mosfet器件崩溃电压的方法,其特征在于,所述将sic mosfet器件的沟道区域由现有垂直的排列结构,重新设计成垂直和水平结构共存,包括:

3.根据权利要求1所述的一种提升sic mosfet器件崩溃电压的方法,其特征在于,所述mosfet管包括:

4.根据权利要求3所述的一种提升sic mosfet器件崩溃电压的方法,其特征在于,所述p型区域两侧设有保护环。

5.根据权利要求1所述的一种提升sic mosfet器件崩溃电压的方法,其特征在于,所述栅极区通过栅极侧壁与所述源极接触连接。

6.根据权利要求5所述的一种提升sic mosfet器件崩溃电压的方法,其特征在于,所述栅极侧壁为氮化硅薄膜。

7.根据权利要求3所述的一种提升sic mosfet器件崩溃电压的方法,其特征在于,所述sic基板为n+型基板。

8.根据权利要求3所述的一种提升sic mosfet器件崩溃电压的方法,其特征在于,所述漂移区为n-漂移区。

9.根据权利要求3所述的一种提升sic mosfet器件崩溃电压的方法,其特征在于,所述n型离子注入层为n+型。

10.根据权利要求3所述的一种提升sic mosfet器件崩溃电压的方法,其特征在于,所述p型离子注入层为p+型。

技术总结

本发明公开了一种提升SiC MOSFET器件崩溃电压的方法,属于半导体技术领域,包括:将多个MOSFET管并联,将SiC MOSFET器件的沟道区域由现有垂直的排列结构,重新设计成垂直和水平结构共存;将所述MOSFET管的栅极设计为方形矩阵列式。该方法提升MOSFET器件沟道的面积,增加器件栅极开关可控的沟道面积再并联多个MOSFET,进而提升整体并联后的等校晶体管的崩溃电压,该方法形成的SiC MOSFET器件有别于一般传统硅基MOSFET,碳化硅基MOSFET器件单位面积的功率密度更高,适用于1200V~1500V高压器件开关。

技术研发人员:林张鸿,冯小涛,赵炎,张淞,何泽涛,林书勋,黎明

受保护的技术使用者:成都海威华芯科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!