一种低栅极内阻屏蔽栅沟槽MOSFET的制作方法

本发明涉及到一种屏蔽栅沟槽mosfet,尤其涉及到一种低栅极内阻屏蔽栅沟槽mosfet。

背景技术:

1、屏蔽栅结构(sgt)mosfet 利用电荷平衡原理打破了硅的理论极限,实现了击穿电压和导通电阻的优化,在中低压硅基功率器件领域得到了广泛的应用。如图1所示,传统的屏蔽栅(sgt)结构中,沟槽内存在两层多晶硅、分别与源极和栅极相连,两层多晶硅通过inter poly oxide层实现电隔离,使得该传统屏蔽栅结构(sgt)mosfet的栅极内阻rg较大,通常为1~5ω。目前,sgt对于击穿电压和导通电阻的优化主要基于工艺能力的提升,例如,深宽比更高的沟槽刻蚀工艺和多晶填充工艺,使得器件的单胞截距更小,从而优化沟道电阻,而没有对其沟槽中的内部结构作出改进。事实上,单胞密度的提升带来了器件电容迅速飙升以及开关损耗增加的不利影响,而对大多数应用来说,器件电容和开关损耗也是评价器件优劣的重要指标。此外,如图2和图3所示,传统的sgt结构,在栅极打线区下方无有效图形,栅极打线区下方没有有源区即不形成电流通道,造成一定的有效图形损失。

技术实现思路

1、本发明所要解决的技术问题是:提供一种通过对其沟槽中内部结构的改进来降低栅极内阻的低栅极内阻屏蔽栅沟槽mosfet。

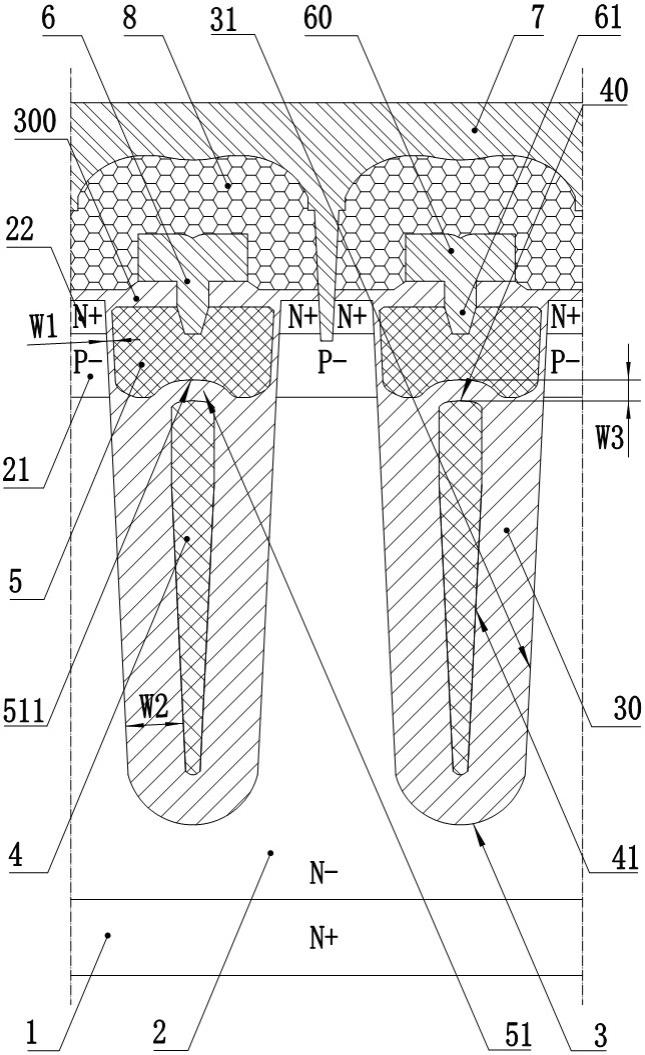

2、为解决上述技术问题,本发明采用的技术方案为:一种低栅极内阻屏蔽栅沟槽mosfet,包括:半导体基板,半导体基板包括有第一导电类型衬底以及设置在第一导电类型衬底上的第一导电类型外延层,其中,第一导电类型外延层的表面为第一主面,第一导电类型衬底的表面为第二主面,第一主面上开设有元胞沟槽,元胞沟槽内设置有第一多晶硅层和位于第一多晶硅层下方的第二多晶硅层,元胞沟槽内还设置有将第一多晶硅层和第二多晶硅层隔开、以及将第一多晶硅层和第二多晶硅层与元胞沟槽的内壁隔开的沟槽内氧化层;所述第一多晶硅层的底面上开设有与第二多晶硅层的顶面相配合的等距凹槽,使得第二多晶硅层的顶面上的各处到第一多晶硅层的等距凹槽的底壁上的最短距离均相等;第一导电类型外延层在位于元胞沟槽的外侧上部依次注入第二导电类型注入层和第一导电类型注入层;所述的第一主面在元胞沟槽的上方还设置有与所述的沟槽内氧化层相连的隔离氧化层、以及位于隔离氧化层上方的隔离介质层,隔离介质层和隔离氧化层中设置有栅极金属层,该栅极金属层呈t型,该栅极金属层包括:位于隔离介质层中的头冠部、居中设置在所述头冠部底面上的连接部,连接部的上部穿设在隔离氧化层中,连接部的下部伸入第一多晶硅层中;栅极金属层与栅极打线区相连作为所述mosfet的栅极;所述的隔离介质层垂直向下开设有贯穿隔离介质层和隔离氧化层、深入至第二导电类型注入层的源极引出孔,隔离介质层上和源极引出孔中淀积有源极金属层,源极金属层与源极打线区相连作为所述mosfet的源极;所述的第二主面上淀积有漏极金属层,漏极金属层作为所述mosfet的漏极。

3、作为一种优选方案,在所述的一种低栅极内阻屏蔽栅沟槽mosfet中,所述第二多晶硅层下部的两侧侧壁分别与元胞沟槽相应侧的侧壁平行。

4、作为一种优选方案,在所述的一种低栅极内阻屏蔽栅沟槽mosfet中,所述第二多晶硅层下部的高度占整个第二多晶硅层高度的四分之三至五分之四之间。

5、作为一种优选方案,在所述的一种低栅极内阻屏蔽栅沟槽mosfet中,所述第二多晶硅层下部的两侧侧壁与元胞沟槽的相应侧侧壁之间的距离相等,所述第一多晶硅层的两侧侧壁与元胞沟槽的相应侧侧壁之间的距离相等。

6、作为一种优选方案,在所述的一种低栅极内阻屏蔽栅沟槽mosfet中,所述第二多晶硅层下部的侧壁与元胞沟槽的相应侧侧壁之间的距离是第一多晶硅层的侧壁与元胞沟槽的相应侧侧壁之间的距离的2.5至4倍。

7、作为一种优选方案,在所述的一种低栅极内阻屏蔽栅沟槽mosfet中,所述栅极金属层的头冠部的宽度是连接部上部宽度的2.5至3.5倍。

8、作为一种优选方案,在所述的一种低栅极内阻屏蔽栅沟槽mosfet中,所述栅极金属层的头冠部的宽度在1μm~5μm之间。

9、作为一种优选方案,在所述的一种低栅极内阻屏蔽栅沟槽mosfet中,所述栅极金属层的头冠部的厚度在0.3μm~2μm之间。

10、作为一种优选方案,在所述的一种低栅极内阻屏蔽栅沟槽mosfet中,所述第二多晶硅层的顶面到第一多晶硅层的等距凹槽的底壁的距离控制在0.15μm~0.6μm之间。

11、作为一种优选方案,在所述的一种低栅极内阻屏蔽栅沟槽mosfet中,所述等距凹槽的底壁和第二多晶硅层的顶面均为弧形柱面。

12、本发明的有益效果是:

13、首先,本发明通过在隔离介质层和隔离氧化层中设置栅极金属层,形成双层金属布局的屏蔽栅沟槽mosfet结构,由于栅极金属与第一多晶硅层中的栅极多晶硅相连,栅极电阻转变为栅极金属的电阻,从而可以将栅极电阻(也称栅极内阻)rg控制在极小的范围之内。

14、其次,t型结构的栅极金属层中的头冠部增大了截面积,进一步减小了栅极电阻;以铝作为栅极金属层为例,铝的电阻率为0.0294ωmm2/m,远远小于重掺杂的多晶硅,采用铝电极作为栅极材料可使栅极电阻rg大幅度降低,通常可以控制在0.2ω以内,降低了整个器件的开关时间(tdon和tdoff),提升了整个器件的单脉冲雪崩能量(esa),从而提高了整个器件的可靠性。

15、此外,本发明中双层金属布局的mosfet结构,可通过接触孔和双层金属的平面选择性布局,实现了双层金属的互连,达到了有源区优化的目的,填补了栅极打线区下方有源区的空白(参见图5所示),实现了导通电阻的降低,这样,中等面积产品的有源区占比率由86.9%提升至90.3%,折合导通电阻降低3.76%;小面积产品的有源区占比率由78.4%提升至83.2%,折合导通电阻降低5.9%。

技术特征:

1.一种低栅极内阻屏蔽栅沟槽mosfet,包括:半导体基板,半导体基板包括:第一导电类型衬底以及设置在第一导电类型衬底上的第一导电类型外延层,其中,第一导电类型外延层的表面为第一主面,第一导电类型衬底的表面为第二主面,第一主面上开设有元胞沟槽,其特征在于:所述的元胞沟槽内设置有第一多晶硅层和位于第一多晶硅层下方的第二多晶硅层,元胞沟槽内还设置有将第一多晶硅层和第二多晶硅层隔开、以及将第一多晶硅层和第二多晶硅层与元胞沟槽的内壁隔开的沟槽内氧化层;所述第一多晶硅层的底面上开设有与第二多晶硅层的顶面相配合的等距凹槽,使得第二多晶硅层的顶面上的各处到第一多晶硅层的等距凹槽的底壁上的最短距离均相等;第一导电类型外延层在位于元胞沟槽的外侧上部依次注入第二导电类型注入层和第一导电类型注入层;所述的第一主面在元胞沟槽的上方还设置有与所述的沟槽内氧化层相连的隔离氧化层、以及位于隔离氧化层上方的隔离介质层,隔离介质层和隔离氧化层中设置有栅极金属层,该栅极金属层呈t型,该栅极金属层包括:位于隔离介质层中的头冠部、居中设置在所述头冠部底面上的连接部,连接部的上部穿设在隔离氧化层中,连接部的下部伸入第一多晶硅层中;栅极金属层与栅极打线区相连作为所述mosfet的栅极;所述的隔离介质层上还开设有贯穿隔离介质层和隔离氧化层、深入至第二导电类型注入层的源极引出孔,隔离介质层上和源极引出孔中淀积有源极金属层,源极金属层与源极打线区相连作为所述mosfet的源极;所述的第二主面上淀积有漏极金属层,漏极金属层作为所述mosfet的漏极。

2.根据权利要求1所述的一种低栅极内阻屏蔽栅沟槽mosfet,其特征在于,所述第二多晶硅层下部的两侧侧壁分别与元胞沟槽相应侧的侧壁平行。

3.根据权利要求2所述的一种低栅极内阻屏蔽栅沟槽mosfet,其特征在于,所述第二多晶硅层下部的高度占整个第二多晶硅层高度的四分之三至五分之四之间。

4.根据权利要求3所述的一种低栅极内阻屏蔽栅沟槽mosfet,其特征在于,所述第二多晶硅层下部的两侧侧壁与元胞沟槽的相应侧侧壁之间的距离相等,所述第一多晶硅层的两侧侧壁与元胞沟槽的相应侧侧壁之间的距离相等。

5.根据权利要求4所述的一种低栅极内阻屏蔽栅沟槽mosfet,其特征在于,所述第二多晶硅层下部的侧壁与元胞沟槽的相应侧侧壁之间的距离是第一多晶硅层的侧壁与元胞沟槽的相应侧侧壁之间的距离的2.5至4倍。

6.根据权利要求1所述的一种低栅极内阻屏蔽栅沟槽mosfet,其特征在于,所述栅极金属层的头冠部的宽度是连接部上部宽度的2.5至3.5倍。

7.根据权利要求1所述的一种低栅极内阻屏蔽栅沟槽mosfet,其特征在于,所述栅极金属层的头冠部的宽度在1μm~5μm之间。

8.根据权利要求7所述的一种低栅极内阻屏蔽栅沟槽mosfet,其特征在于,所述栅极金属层的头冠部的厚度在0.3μm~2μm之间。

9.根据权利要求1所述的一种低栅极内阻屏蔽栅沟槽mosfet,其特征在于,所述第二多晶硅层的顶面到第一多晶硅层的等距凹槽的底壁的距离控制在0.15μm~0.6μm之间。

10.根据权利要求1至9中任一项所述的一种低栅极内阻屏蔽栅沟槽mosfet,其特征在于,所述等距凹槽的底壁和第二多晶硅层的顶面均为弧形柱面。

技术总结

本发明公开了一种低栅极内阻屏蔽栅沟槽MOSFET,包括:由其表面为第一主面的第一导电类型衬底和其表面为第二主面的第一导电类型外延层构成的半导体基板,第一主面上开设有元胞沟槽,元胞沟槽内设置有第一多晶硅层和第二多晶硅层和沟槽内氧化层;第一导电类型外延层在位于元胞沟槽的外侧上部依次注入有第二导电类型注入层和第一导电类型注入层,第一主面在元胞沟槽的上方依次设置有隔离氧化层和隔离介质层,隔离介质层和隔离氧化层中设置有栅极金属层,隔离介质层上垂直向下开设有深入至第二导电类型注入层的源极引出孔,隔离介质层上和源极引出孔中淀积有源极金属层。中低压功率器件尤其适合于采用本发明所述屏蔽栅沟槽MOSFET的结构。

技术研发人员:顾挺,侯宏伟,包奚成,杨建军

受保护的技术使用者:张家港凯思半导体有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!