一种多功能功率器件及其制作方法与流程

本发明属于半导体集成电路制造,涉及一种多功能功率器件及其制作方法。

背景技术:

1、mosfet是功率半导体的一种,在日常生活中,凡涉及发电、输电、变电、配电、用电、储电等环节的,均离不开功率半导体,功率半导体器件作为不可替代的基础性产品,广泛应用于国民经济建设的各个领域。目前,现在市场主流的mosfet主要分为四大类:超结mosfet、平面型mosfet、屏蔽栅沟槽mosfet和沟槽型mosfet,其中,屏蔽栅mosfet是对深沟槽mosfet的一种改进,通过在栅电极下方增加多晶硅电极(称为屏蔽电极),并将屏蔽电极与源电极相连,将传统沟槽型mosfet底部中的大部分栅漏极电容cgd或crss转换为栅源极电容cgs,同时屏蔽栅技术实现了电荷耦合,减小了漂移区临界电场强度,器件的rds(on)也得以降低,因此,屏蔽栅沟槽mosfet广泛应用于电源开关领域。

2、目前,普通的屏蔽栅沟槽mosfet器件的导通电阻较低,但是开关速度及开关损耗相对而言并不具有明显优势,因此适用于对内阻要求严格而对开关速度要求宽松的应用领域,却不适用于要求开关损耗小及开关速度快的领域(如高频同步整流领域),即普通的功率器件无法实现多场景的应用,应用前景受限。

3、因此,如何提供一种多功能功率器件及其制作方法,以实现功率器件能够满足多种应用场合的使用需求,成为本领域技术人员亟待解决的一个重要技术问题。

4、应该注意,上面对技术背景的介绍只是为了方便对本申请的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本申请的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种多功能功率器件及其制作方法,用于解决现有技术中普通功率器件不能满足多种应用场合的使用需求,应用前景受限的问题。

2、为实现上述目的及其他相关目的,本发明提供一种多功能功率器件,包括:

3、半导体层;

4、至少一第一元胞,位于所述半导体层中,所述第一元胞包括第一屏蔽栅多晶硅及第一栅极多晶硅,所述第一屏蔽栅多晶硅与所述第一栅极多晶硅间隔设置;

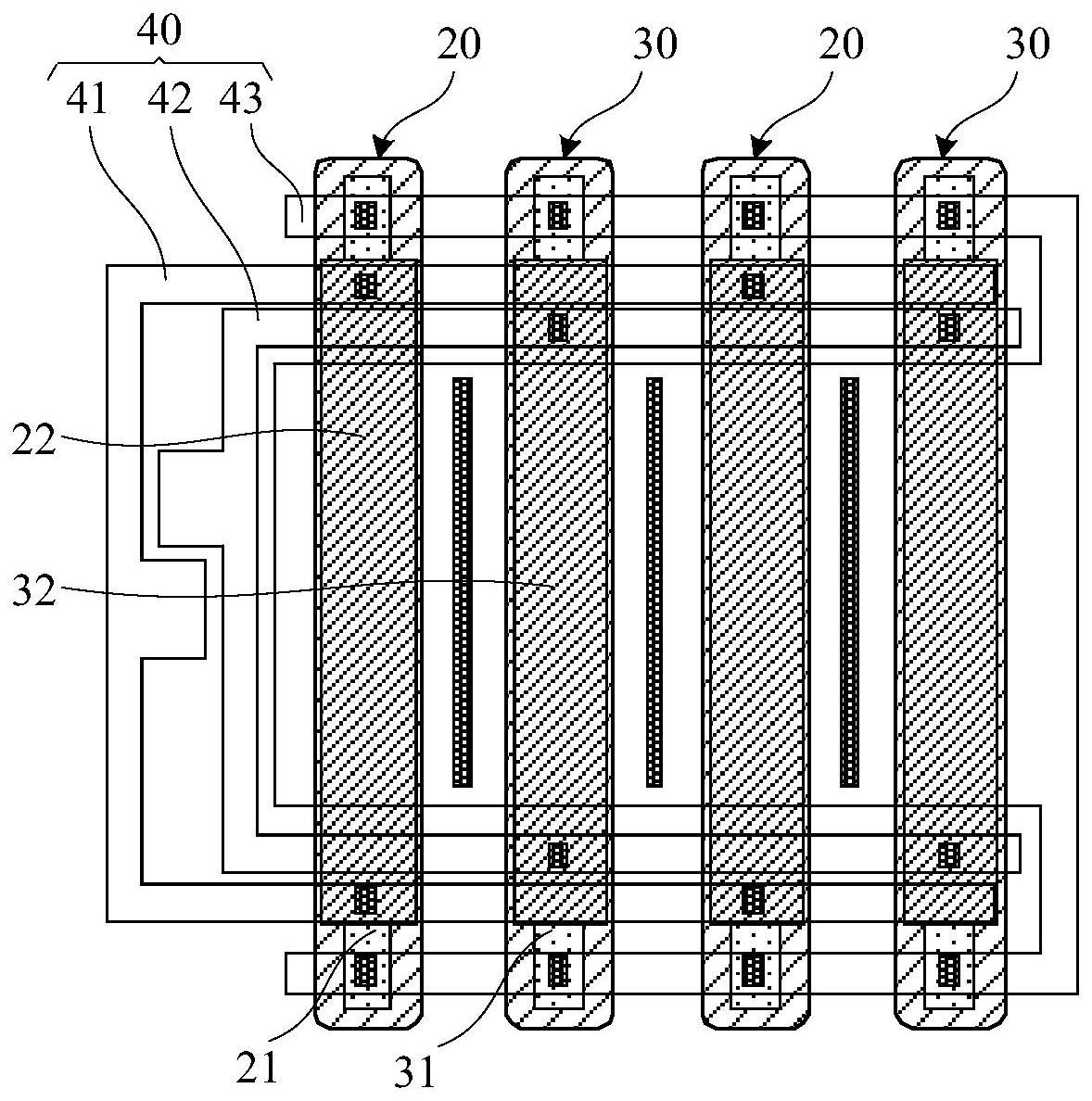

5、至少一第二元胞,位于所述半导体层中且与所述第一元胞间隔设置,所述第二元胞包括第二屏蔽栅多晶硅及第二栅极多晶硅,所述第二屏蔽栅多晶硅与所述第二栅极多晶硅间隔设置;

6、金属层,位于所述半导体层上,所述金属层包括在间隔设置的第一栅极金属、第二栅极金属及源极金属,所述第一栅极金属与所述第一栅极多晶硅电连接,所述第二栅极金属与所述第二栅极多晶硅电连接,所述源极金属与所述第一屏蔽栅多晶硅及所述第二屏蔽栅多晶硅电连接。

7、可选地,所述第一栅极金属与所述第二栅极金属电连接。

8、可选地,所述第一栅极金属与所述源极金属电连接,或者,所述第二栅极金属与所述源极金属电连接。

9、可选地,所述第一屏蔽栅多晶硅的至少一部分顶面低于所述第一栅极多晶硅的顶面,所述第一栅极多晶硅位于所述第一屏蔽栅多晶硅的上方,并且,所述第二屏蔽栅多晶硅的至少一部分顶面低于所述第二栅极多晶硅的顶面,所述第二栅极多晶硅位于所述第二屏蔽栅多晶硅的上方。

10、可选地,所述第一屏蔽栅多晶硅的顶面与所述第一栅极多晶硅的顶面平齐,所述第一栅极多晶硅环绕所述第一屏蔽栅多晶硅设置,并且,所述第二屏蔽栅多晶硅的顶面与所述第二栅极多晶硅的顶面平齐,所述第二栅极多晶硅环绕所述第二屏蔽栅多晶硅设置。

11、可选地,所述第一屏蔽栅多晶硅的至少一部分顶面低于所述第一栅极多晶硅的顶面,所述第一栅极多晶硅位于所述第一屏蔽栅多晶硅的上方,并且,所述第二屏蔽栅多晶硅的顶面与所述第二栅极多晶硅的顶面平齐,所述第二栅极多晶硅环绕所述第二屏蔽栅多晶硅设置。

12、可选地,所述第一元胞与所述第二元胞均为多个,多个所述第一元胞与多个所述第二元胞间隔且交替排列。

13、本发明还提供一种多功能功率器件的制作方法,包括以下步骤:

14、提供一半导体层;

15、形成至少一第一元胞及至少一第二元胞于所述半导体层中,所述第一元胞包括第一屏蔽栅多晶硅及第一栅极多晶硅,所述第一屏蔽栅多晶硅与所述第一栅极多晶硅间隔设置,所述第二元胞与所述第一元胞间隔设置,所述第二元胞包括第二屏蔽栅多晶硅及第二栅极多晶硅,所述第二屏蔽栅多晶硅与所述第二栅极多晶硅间隔设置;

16、形成金属层于所述半导体层上,所述金属层包括间隔设置的第一栅极金属、第二栅极金属及源极金属,所述第一栅极金属与所述第一栅极多晶硅电连接,所述第二栅极金属与所述第二栅极多晶硅电连接,所述源极金属与所述第一屏蔽栅多晶硅及所述第二屏蔽栅多晶硅电连接。

17、可选地,所述第一栅极金属与所述第二栅极金属电连接。

18、可选地,所述第一栅极金属与所述源极金属电连接,或者,所述第二栅极金属与所述源极金属电连接。

19、如上所述,本发明的多功能功率器件能够根据实际应用场合选择相应的功能从而实现多场景应用,有效提高芯片的利用率并拓展其应用场景,具备较强的市场竞争力;本发明的多功能功率器件的制作方法,能够制作得到多功能功率器件,且制作步骤简单、工艺成熟,能够实现大规模生产。

技术特征:

1.一种多功能功率器件,其特征在于,包括:

2.根据权利要求1所述的多功能功率器件,其特征在于:所述第一栅极金属与所述第二栅极金属电连接。

3.根据权利要求1所述的多功能功率器件,其特征在于:所述第一栅极金属与所述源极金属电连接,或者,所述第二栅极金属与所述源极金属电连接。

4.根据权利要求1所述的多功能功率器件,其特征在于:所述第一屏蔽栅多晶硅的至少一部分顶面低于所述第一栅极多晶硅的顶面,所述第一栅极多晶硅位于所述第一屏蔽栅多晶硅的上方,并且,所述第二屏蔽栅多晶硅的至少一部分顶面低于所述第二栅极多晶硅的顶面,所述第二栅极多晶硅位于所述第二屏蔽栅多晶硅的上方。

5.根据权利要求1所述的多功能功率器件,其特征在于:所述第一屏蔽栅多晶硅的顶面与所述第一栅极多晶硅的顶面平齐,所述第一栅极多晶硅环绕所述第一屏蔽栅多晶硅设置,并且,所述第二屏蔽栅多晶硅的顶面与所述第二栅极多晶硅的顶面平齐,所述第二栅极多晶硅环绕所述第二屏蔽栅多晶硅设置。

6.根据权利要求1所述的多功能功率器件,其特征在于:所述第一屏蔽栅多晶硅的至少一部分顶面低于所述第一栅极多晶硅的顶面,所述第一栅极多晶硅位于所述第一屏蔽栅多晶硅的上方,并且,所述第二屏蔽栅多晶硅的顶面与所述第二栅极多晶硅的顶面平齐,所述第二栅极多晶硅环绕所述第二屏蔽栅多晶硅设置。

7.根据权利要求1所述的多功能功率器件,其特征在于:所述第一元胞与所述第二元胞均为多个,多个所述第一元胞与多个所述第二元胞间隔且交替排列。

8.一种多功能功率器件的制作方法,其特征在于,包括以下步骤:

9.根据权利要求8所述的多功能功率器件,其特征在于:所述第一栅极金属与所述第二栅极金属电连接。

10.根据权利要求8所述的多功能功率器件,其特征在于:所述第一栅极金属与所述源极金属电连接,或者,所述第二栅极金属与所述源极金属电连接。

技术总结

本发明提供一种多功能功率器件及其制作方法,该器件包括半导体层、至少一第一元胞、至少一第二元胞及金属层,第一元胞及第二元胞在半导体层间隔设置,第一元胞包括间隔设置的第一屏蔽栅多晶硅及第一栅极多晶硅,第二元胞包括间隔设置的第二屏蔽栅多晶硅及第二栅极多晶硅,金属层位于半导体层上且包括间隔设置的第一栅极金属、第二栅极金属及源极金属,第一栅极金属与第一栅极多晶硅电连接,第二栅极金属与第二栅极多晶硅电连接,源极金属与第一屏蔽栅多晶硅及第二屏蔽栅多晶硅电连接。该器件可根据实际应用场合选择相应的功能从而实现多场景应用,有效提高芯片的利用率并拓展其应用场景,该制作方法制作步骤简单、工艺成熟,能够实现大规模生产。

技术研发人员:高学,柴展,罗杰馨

受保护的技术使用者:上海功成半导体科技有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!