选择性外延生长方法与流程

本申请涉及半导体集成电路制造,具体涉及一种选择性外延生长方法。

背景技术:

1、bi-cmos工艺是指在同一衬底上集成双极晶体管(bipolar junctiontransistor,bjt)器件(例如,其可以是异质结双极晶体管(heterojunction bipolartransistor,hbt)器件)和互补金属氧化物半导体(complementary metal-oxidesemiconductor,cmos)器件的制备工艺。

2、在55纳米(nm)以上的半导体制程中,bi-cmos工艺中通常采用选择性外延(selective epi,seg)生长工艺(即在需要生长的区域生长外延层的工艺)生长hbt器件的外基区。然而,通过选择性外延生长工艺得到的外延层在衬底上的厚度分布一致性较差。

技术实现思路

1、本申请提供了一种选择性外延生长方法,可以解决相关技术中提供的bi-cmos工艺形成的hbt器件的外基区的厚度的一致性较差的问题,该方法包括:

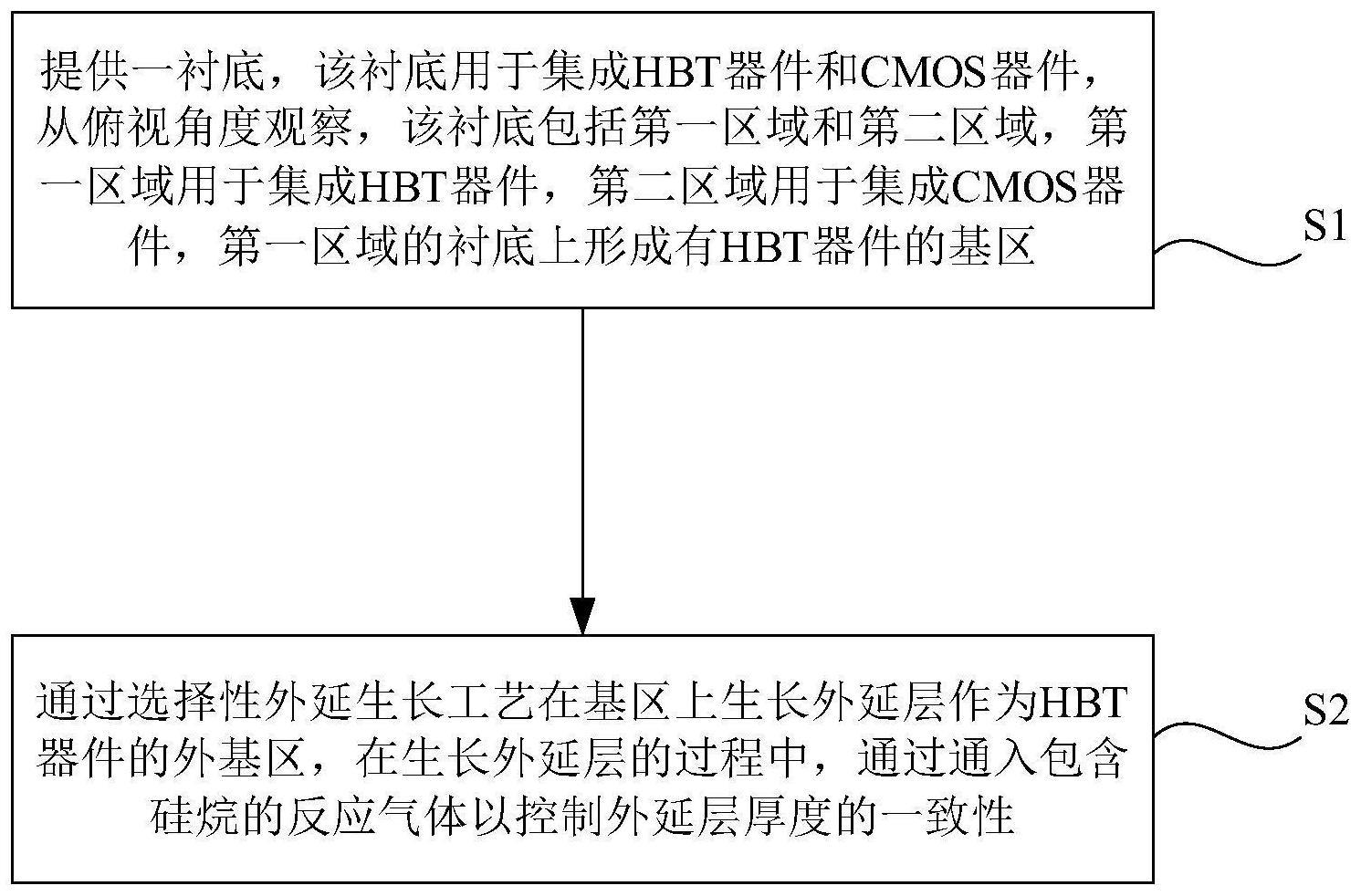

2、提供一衬底,所述衬底用于集成hbt器件和cmos器件,从俯视角度观察,所述衬底包括第一区域和第二区域,所述第一区域用于集成所述hbt器件,所述第二区域用于集成所述cmos器件,所述第一区域的衬底上形成有所述hbt器件的基区;

3、通过选择性外延生长工艺在所述基区上生长外延层作为所述hbt器件的外基区,在生长所述外延层的过程中,通过通入包含硅烷的反应气体以控制所述外延层厚度的一致性。

4、在一些实施例中,在生长所述外延层的过程中,通入的主反应气体包括dcs。

5、在一些实施例中,所述外延层的厚度为200埃至1000埃。

6、在一些实施例中,所述第一区域的衬底中形成有多个第一sti结构,从俯视角度观察,所述第一sti结构为环形,所述第一sti结构环绕的衬底区域内形成有第二sti结构,所述第二sti结构为环形;

7、所述第一sti结构的外边缘环绕的区域为所述hbt器件的有源区,所述第一sti结构和所述第二sti结构之间的衬底区域为所述hbt器件的引出区,所述第二sti结构环绕的衬底区域为所述hbt器件的集电区。

8、在一些实施例中,从俯视角度观察,所述基区覆盖在所述有源区上,所述外基区为环形。

9、在一些实施例中,所述hbt器件的有源区的衬底中形成有埋层,所述埋层形成于引出区以及所述第一sti结构和所述第二sti结构下方的衬底中。

10、在一些实施例中,所述通过选择性外延生长工艺在所述基区上生长外延层作为所述第一区域生长所述hbt器件的外基区之后,还包括:

11、在所述外基区环绕的衬底区域上形成介质层;

12、在所述介质层上形成多晶硅层;

13、在所述多晶硅层的周侧形成侧墙。

14、本申请技术方案,至少包括如下优点:

15、通过在bi-cmos工艺中,在通过选择性外延生长工艺在基区上生长外延层作为hbt器件的外基区时,通过通入包含硅烷的反应气体以控制外延层厚度的一致性,从而提高了hbt器件外基区厚度的一致性,在一定程度上提高了器件产品的良率。

技术特征:

1.一种选择性外延生长方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,在生长所述外延层的过程中,通入的主反应气体包括dcs。

3.根据权利要求2所述的方法,其特征在于,所述外延层的厚度为200埃至1000埃。

4.根据权利要求1至3任一所述的方法,其特征在于,所述第一区域的衬底中形成有多个第一sti结构,从俯视角度观察,所述第一sti结构为环形,所述第一sti结构环绕的衬底区域内形成有第二sti结构,所述第二sti结构为环形;

5.根据权利要求4所述的方法,其特征在于,从俯视角度观察,所述基区覆盖在所述有源区上,所述外基区为环形。

6.根据权利要求5所述的方法,其特征在于,所述hbt器件的有源区的衬底中形成有埋层,所述埋层形成于所述引出区以及所述第一sti结构和所述第二sti结构下方的衬底中。

7.根据权利要求6所述的方法,其特征在于,所述通过选择性外延生长工艺在所述基区上生长外延层作为所述第一区域生长所述hbt器件的外基区之后,还包括:

技术总结

本申请公开了一种选择性外延生长方法,包括:提供一衬底,该衬底用于集成HBT器件和CMOS器件,从俯视角度观察,衬底包括第一区域和第二区域,第一区域用于集成HBT器件,第二区域用于集成CMOS器件,第一区域的衬底上形成有HBT器件的基区;通过选择性外延生长工艺在基区上生长外延层作为HBT器件的外基区,在生长外延层的过程中,通过通入包含硅烷的反应气体以控制外延层厚度的一致性。本申请通过在Bi‑CMOS工艺中,在通过选择性外延生长工艺在基区上生长外延层作为HBT器件的外基区时,通过通入包含硅烷的反应气体以控制外延层厚度的一致性,从而提高了HBT器件外基区厚度的一致性,在一定程度上提高了器件产品的良率。

技术研发人员:周康,孙伟虎,杨德明,赵正元,张守龙

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!