包含LDMOS晶体管的半导体器件的制作方法

本发明涉及集成电路制造领域,尤其涉及一种包含ldmos晶体管的半导体器件。

背景技术:

1、ldmos(laterally diffused metal oxide semiconductor,横向扩散金属氧化物半导体)晶体管是一种双扩散结构的功率器件,相较于普通的mos晶体管,ldmos晶体管增加了低掺杂的漂移区,漂移区在沟道和漏区之间起缓冲作用,削弱了短沟道效应,漏源电压(vds)的大部分会降落在漂移区上,在沟道夹断后,基本上没有沟道的长度调制效应,并且当漏源电压进一步增大时,输出电阻不会降低,沟道区不易穿通,从而ldmos晶体管的击穿电压(bv)基本不受沟道长度和掺杂水平限制,可以进行独立设计。ldmos晶体管在工艺上容易实现0.4μm~2μm的沟道长度,故跨导gm、漏极电流(id)、最高工作频率和速度都较普通的mos晶体管有较大幅度的提高。ldmos晶体管在中高压以及高压领域应用广泛。

2、对于ldmos晶体管而言,增加漂移区的长度可以提高击穿电压,但会增加芯片面积和导通电阻(rdson),需进行适合的结构设计,以获得较大的击穿电压和较小的导通电阻。目前,对于包含ldmos晶体管的半导体器件,在提高ldmos晶体管的击穿电压和降低导通电阻方面,仍需改进。

技术实现思路

1、为了提高ldmos晶体管的击穿电压和降低导通电阻,本发明提供一种包含ldmos晶体管的半导体器件。

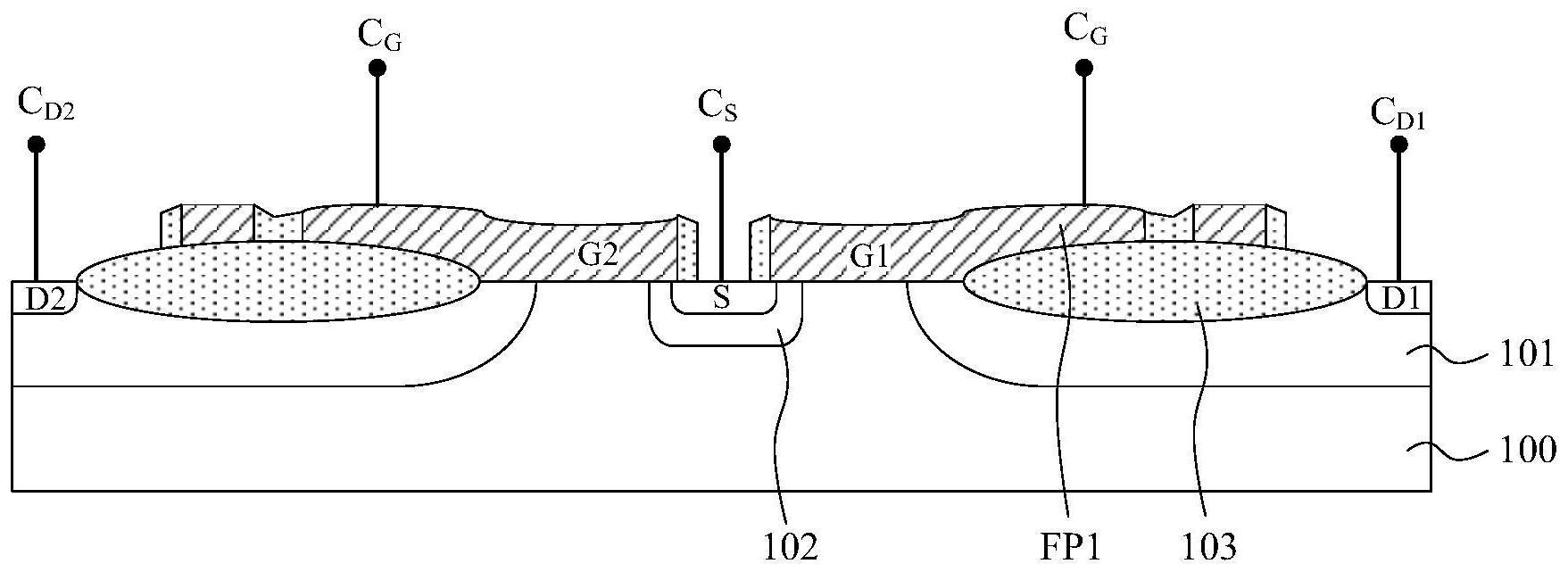

2、本发明提供的包含ldmos晶体管的半导体器件包括具有第一导电类型的半导体衬底以及基于所述半导体衬底形成的ldmos晶体管,所述ldmos晶体管包括:

3、形成于所述半导体衬底内且具有第二导电类型的漂移区、源区以及漏区;

4、形成于所述半导体衬底上的多晶硅栅极,所述多晶硅栅极从所述源区横跨至所述漂移区;

5、漂移区场氧化层,形成于所述漂移区的表面且邻接所述漏区;

6、场极板,由构成所述多晶硅栅极的多晶硅条沿宽度方向扩展至所述漂移区场氧化层表面形成;以及

7、第一栅极金属接触,对应于所述场极板形成于所述多晶硅条顶表面。

8、可选地,所述半导体器件包括多个所述ldmos晶体管,至少两个所述ldmos晶体管的多晶硅栅极共用所述多晶硅条,至少两个所述ldmos晶体管的源区和漏区分别位于所述多晶硅条的两侧。

9、可选地,所述ldmos晶体管还包括源区金属接触和漏区金属接触,所述源区金属接触和所述漏区金属接触分别形成于所述源区顶表面和所述漏区顶表面。

10、可选的,所述多晶硅条顶表面对应于所述场极板的区域分散形成有多个所述第一栅极金属接触。

11、可选地,所述多晶硅条顶表面形成的所述第一栅极金属接触的横截面面积大于所述源区金属接触和/或所述漏区金属接触的横截面面积。

12、可选地,所述多晶硅条顶表面形成的所述第一栅极金属接触的数量大于或等于位于所述多晶硅条侧面的所述源区金属接触或所述漏区金属接触的数量。

13、可选地,所述半导体器件包括至少一对镜像设置的所述ldmos晶体管,每对镜像设置的所述ldmos晶体管共用所述源区。

14、可选地,所述ldmos晶体管还包括第二栅极金属接触,所述第二栅极金属接触形成于所述多晶硅条的长度方向上的端部。

15、可选地,所述半导体器件还包括形成于所述场极板顶表面的金属硅化物层以及层间介质层,所述层间介质层覆盖所述半导体衬底以及各所述ldmos晶体管,所述第一栅极金属接触填充于贯穿所述层间介质层的通孔中,所述通孔暴露出所述金属硅化物层。

16、可选地,所述半导体器件为bcd器件,所述bcd器件包括基于所述半导体衬底形成的所述ldmos晶体管、双极晶体管以及cmos晶体管。

17、本发明提供的包含ldmos晶体管的半导体器件中,所述ldmos晶体管具有由构成多晶硅栅极的多晶硅条沿宽度方向扩展至漂移区场氧化层表面形成的场极板,并且,第一栅极金属接触对应于所述场极板形成于所述多晶硅条顶表面,栅电压通过所述第一栅极金属接触施加在所述场极板和所述多晶硅栅极上,对于多晶硅栅极和场极板的控制能力较强,可以有效控制场极板下方的漂移区表面电场,使漂移区的表面电场得到有效弱化,能够优化表面电场分布,有利于提高ldmos晶体管的击穿电压以及降低导通电阻,有助于提高ldmos晶体管的综合性能。

技术特征:

1.一种包含ldmos晶体管的半导体器件,其特征在于,所述半导体器件包括具有第一导电类型的半导体衬底以及基于所述半导体衬底形成的ldmos晶体管,所述ldmos晶体管包括:

2.如权利要求1所述的半导体器件,其特征在于,所述半导体器件包括多个所述ldmos晶体管,至少两个所述ldmos晶体管的多晶硅栅极共用所述多晶硅条,至少两个所述ldmos晶体管的源区和漏区分别位于所述多晶硅条的两侧。

3.如权利要求2所述的半导体器件,其特征在于,所述ldmos晶体管还包括:

4.如权利要求3所述的半导体器件,其特征在于,所述多晶硅条顶表面对应于所述场极板的区域分散形成有多个所述第一栅极金属接触。

5.如权利要求4所述的半导体器件,其特征在于,所述多晶硅条顶表面形成的所述第一栅极金属接触的横截面面积大于所述源区金属接触和/或所述漏区金属接触的横截面面积。

6.如权利要求4所述的半导体器件,其特征在于,所述多晶硅条顶表面形成的所述第一栅极金属接触的数量大于或等于位于所述多晶硅条侧面的所述源区金属接触或所述漏区金属接触的数量。

7.如权利要求2所述的半导体器件,其特征在于,所述半导体器件包括至少一对镜像设置的所述ldmos晶体管,每对镜像设置的所述ldmos晶体管共用所述源区。

8.如权利要求1所述的半导体器件,其特征在于,所述ldmos晶体管还包括:

9.如权利要求1所述的半导体器件,其特征在于,所述半导体器件还包括:

10.如权利要求1所述的半导体器件,其特征在于,所述半导体器件为bcd器件,所述bcd器件包括基于所述半导体衬底形成的所述ldmos晶体管、双极晶体管以及cmos晶体管。

技术总结

本发明涉及一种包含LDMOS晶体管的半导体器件。所述半导体器件中,所述LDMOS晶体管包括由构成多晶硅栅极的多晶硅条沿宽度方向扩展至漂移区场氧化层表面形成的场极板,并且,第一栅极金属接触对应于所述场极板形成于所述多晶硅条顶表面,栅电压通过所述第一栅极金属接触施加在所述场极板和所述多晶硅栅极上,对于多晶硅栅极和场极板的控制能力较强,可以有效控制场极板下方的漂移区表面电场,使漂移区的表面电场得到有效弱化,能够优化表面电场分布,有利于提高LDMOS晶体管的击穿电压以及降低导通电阻,有助于提高LDMOS晶体管的综合性能。

技术研发人员:肖莉红,司伟

受保护的技术使用者:荣芯半导体(淮安)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!