集成LDMOS与SGT的半导体器件及形成方法与流程

本发明涉及半导体,特别涉及一种集成ldmos与sgt的半导体器件及形成方法。

背景技术:

1、在垂直双扩散金属氧化物半导体场效应晶体管(vertical double-diffusedmetal oxide semiconductor field effect transistor,vdmos)与横向双扩散型场效应晶体管(lateral double-diffused mos,ldmos)集成工艺平台中,需要在重掺杂衬底和外延层上同时制备vdmos和ldmos两种器件。但是在此集成工艺平台中,受限于vdmos性能要求,衬底与外延层杂质掺杂浓度都很高、外延层厚度不能太厚以及衬底在某些工作状态下会加高压,因此,ldmos的纵向隔离难以保证。为了保证纵向足够耐压,漂移区的掺杂浓度要比较低,但会导致ldmos器件的开态击穿电压(on breakdown voltage,on bv)较差。

技术实现思路

1、本发明的目的在于提供一种集成ldmos与sgt的半导体器件及形成方法,以解决ldmos器件的开态击穿电压较差的问题。

2、为解决上述技术问题,本发明提供一种集成ldmos与sgt的半导体器件,包括:

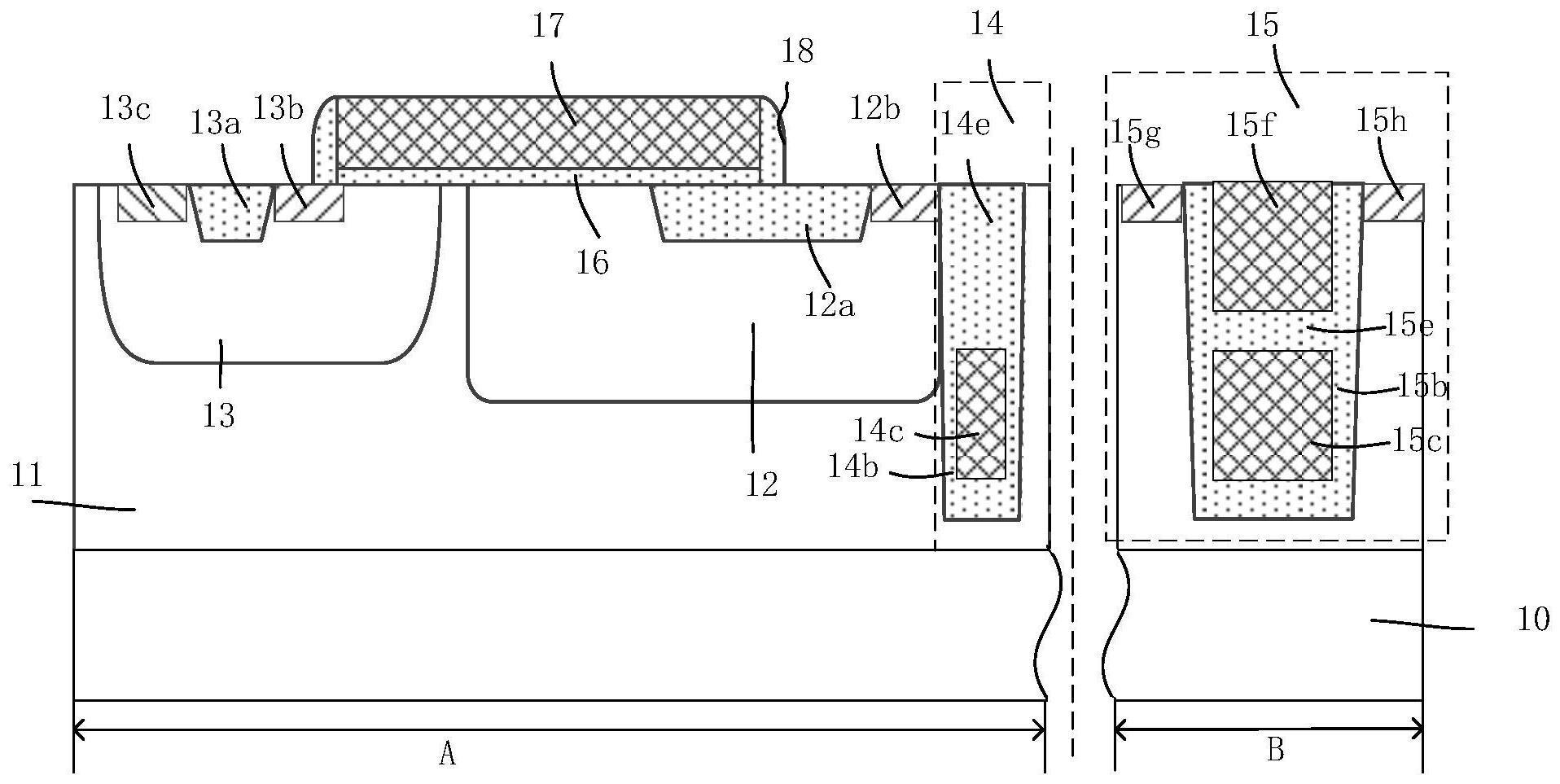

3、衬底,所述衬底包括sgt器件区和ldmos器件区,所述sgt器件区包括sgt器件,所述ldmos器件区包括漂移区以及与所述漂移区相邻的体区;

4、第一漏区,所述第一漏区位于所述漂移区中远离所述体区极一侧;

5、纵向场板,所述纵向场板与所述第一漏区邻接,所述纵向场板的深度大于所述漂移区的深度,以及所述纵向场板和所述sgt器件区中的sgt器件同时形成。

6、可选的,所述纵向场板包括第一深沟槽和位于所述第一深沟槽内下部的第一屏蔽栅,所述第一屏蔽栅悬空且不接电位。

7、可选的,所述ldmos器件区包括阱区,所述漂移区与所述阱区的导电类型相反,所述漂移区在所述阱区内形成耗尽区,所述纵向场板将所述耗尽区的边界向上推至所述第一漏区的区域内。

8、基于同一发明构思,本发明还提供一种集成ldmos与sgt的半导体器件的形成方法,包括:

9、提供一衬底,所述衬底包括sgt器件区和ldmos器件区,所述ldmos器件区上形成漂移区以及与所述漂移区相邻的体区;

10、在所述ldmos器件区上形成纵向场板,同时在所述sgt器件区形成sgt器件;

11、形成第一漏区,所述第一漏区位于所述漂移区中远离所述体区极一侧,且所述第一漏区与所述纵向场板邻接。

12、可选的,在所述ldmos器件区上形成纵向场板,同时在所述sgt器件区形成sgt器件的步骤包括:

13、在ldmos器件区形成第一深沟槽,同时在所述sgt器件区形成第二深沟槽;

14、在所述第一深沟槽内形成第一屏蔽栅,同时在所述第二深沟槽内形成第二屏蔽栅;

15、在所述第一深沟槽内形成第一隔离层,同时在所述第二深沟槽内形成第二隔离层,所述第一沟槽内的第一屏蔽栅和第一隔离层构成纵向场板;

16、去除所述第二深沟槽内的部分所述第二隔离层,并在所述第二深沟槽内形成第二栅极以构成sgt器件。

17、可选的,采用离子注入工艺在所述ldmos器件区形成第一漏区,同时在所述sgt器件区形成第二漏区。

18、可选的,所述第一漏区与所述漂移区的导电类型相同。

19、可选的,在形成所述ldmos器件区的第一栅极之前,在所述漂移区内形成第一浅沟槽隔离结构,以及在所述体区内形成第二浅沟槽隔离结构。

20、可选的,在所述ldmos器件区的体区执行离子注入工艺以形成第一源区和源极接触区,同时在所述sgt器件区形成第二源区。

21、可选的,所述第一源区和所述源极接触区的导电类型相反,且所述第一源区和所述源极接触区之间通过所述第二浅沟槽隔离结构。

22、在本发明提供的集成ldmos与sgt的半导体器件及形成方法中,衬底包括sgt器件区和ldmos器件区,所述ldmos器件区包括漂移区以及与所述漂移区相邻的体区;通过在形成sgt器件区的sgt器件时,同时在ldmos区形成纵向场板,所述纵向场板与所述第一漏区邻接,所述纵向场板的深度大于所述漂移区的深度,所述纵向场板使耗尽区边界向上推至所述第一漏区内。在不增加光刻层以及光刻成本的情况下,本发明通过纵向场板优化纵向电场分布,提高ldmos器件的纵向关态击穿电压,以及在相同的纵向关态击穿电压下,能够让ldmos器件的漂移区掺杂浓度得到进一步的提升,进而提升ldmos器件的性能。

技术特征:

1.一种集成ldmos与sgt的半导体器件,其特征在于,包括:

2.根据权利要求1所述的集成ldmos与sgt的半导体器件,其特征在于,所述纵向场板包括第一深沟槽和位于所述第一深沟槽内下部的第一屏蔽栅,所述第一屏蔽栅悬空且不接电位。

3.根据权利要求1所述的集成ldmos与sgt的半导体器件,其特征在于,所述ldmos器件区包括阱区,所述漂移区与所述阱区的导电类型相反,所述漂移区在所述阱区内形成耗尽区,所述纵向场板将所述耗尽区的边界向上推至所述第一漏区的区域内。

4.一种集成ldmos与sgt的半导体器件的形成方法,其特征在于,包括:

5.根据权利要求4所述的集成ldmos与sgt的半导体器件的形成方法,其特征在于,在所述ldmos器件区上形成纵向场板,同时在所述sgt器件区形成sgt器件的步骤包括:

6.根据权利要求4所述的集成ldmos与sgt的半导体器件的形成方法,其特征在于,采用离子注入工艺在所述ldmos器件区形成第一漏区,同时在所述sgt器件区形成第二漏区。

7.根据权利要求4所述的集成ldmos与sgt的半导体器件的形成方法,其特征在于,所述第一漏区与所述漂移区的导电类型相同。

8.根据权利要求4所述的集成ldmos与sgt的半导体器件的形成方法,其特征在于,在形成所述ldmos器件区的第一栅极之前,在所述漂移区内形成第一浅沟槽隔离结构,以及在所述体区内形成第二浅沟槽隔离结构。

9.根据权利要求8所述的集成ldmos与sgt的半导体器件的形成方法,其特征在于,在所述ldmos器件区的体区执行离子注入工艺以形成第一源区和源极接触区,同时在所述sgt器件区形成第二源区。

10.根据权利要求9所述的集成ldmos与sgt的半导体器件的形成方法,其特征在于,所述第一源区和所述源极接触区的导电类型相反,且所述第一源区和所述源极接触区之间通过所述第二浅沟槽隔离结构。

技术总结

本发明提供的一种集成LDMOS与SGT的半导体器件及形成方法,包括衬底,衬底包括SGT器件区和LDMOS器件区,所述LDMOS器件区包括漂移区以及与所述漂移区相邻的体区;通过在形成SGT器件区的SGT器件时,同时在LDMOS区形成纵向场板,所述纵向场板与所述第一漏区邻接,所述纵向场板的深度大于所述漂移区的深度,以使耗尽区边界向上推至所述第一漏区内。在不增加光刻层以及光刻成本的情况下,本发明通过纵向场板优化纵向电场分布,提高LDMOS器件的纵向关态击穿电压,以及在相同的纵向关态击穿电压下,能够让LDMOS器件的漂移区掺杂浓度得到进一步的提升,进而提升LDMOS器件的性能。

技术研发人员:陈云骢,钱文生,刘冬华,蔡晓晴

受保护的技术使用者:上海华虹宏力半导体制造有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!