半导体结构及其制造方法与流程

本公开实施例涉及半导体领域,特别涉及一种半导体结构及其制造方法。

背景技术:

1、引线键合是半导体封装工艺中一个重要步骤,用引线将芯片上的引线孔和框架衬垫上的引脚连接,使得芯片能与外部电路连接。在微电子封装中,半导体器件的失效约有25%到33.3%是由芯片互连引起的,因而,芯片互连对器件的可靠性影响很大。

2、芯片互连的基础是焊盘和引线的键合。焊盘作为芯片内部电路与外部引线连接的接口,对芯片的良品率及可靠性有着重要的影响。一方面,焊盘表面的状态会影响到引线键合的效果,焊盘表面的低质量会引起引线键合失效或引线键合可靠性差等问题,从而降低后段封测时芯片的良率,甚至影响最终产品的可靠性。另一方面,由于引线键合工序位于整个芯片制造工序的末尾,由于焊盘表面质量不良而造成报废的器件都已接近成品,使得报废的成本变得很高。因此,改善焊盘的表面质量,对于提高半导体结构的良率具有积极意义。

技术实现思路

1、本公开实施例提供一种半导体结构及其制造方法,至少有利于改善焊盘的表面质量。

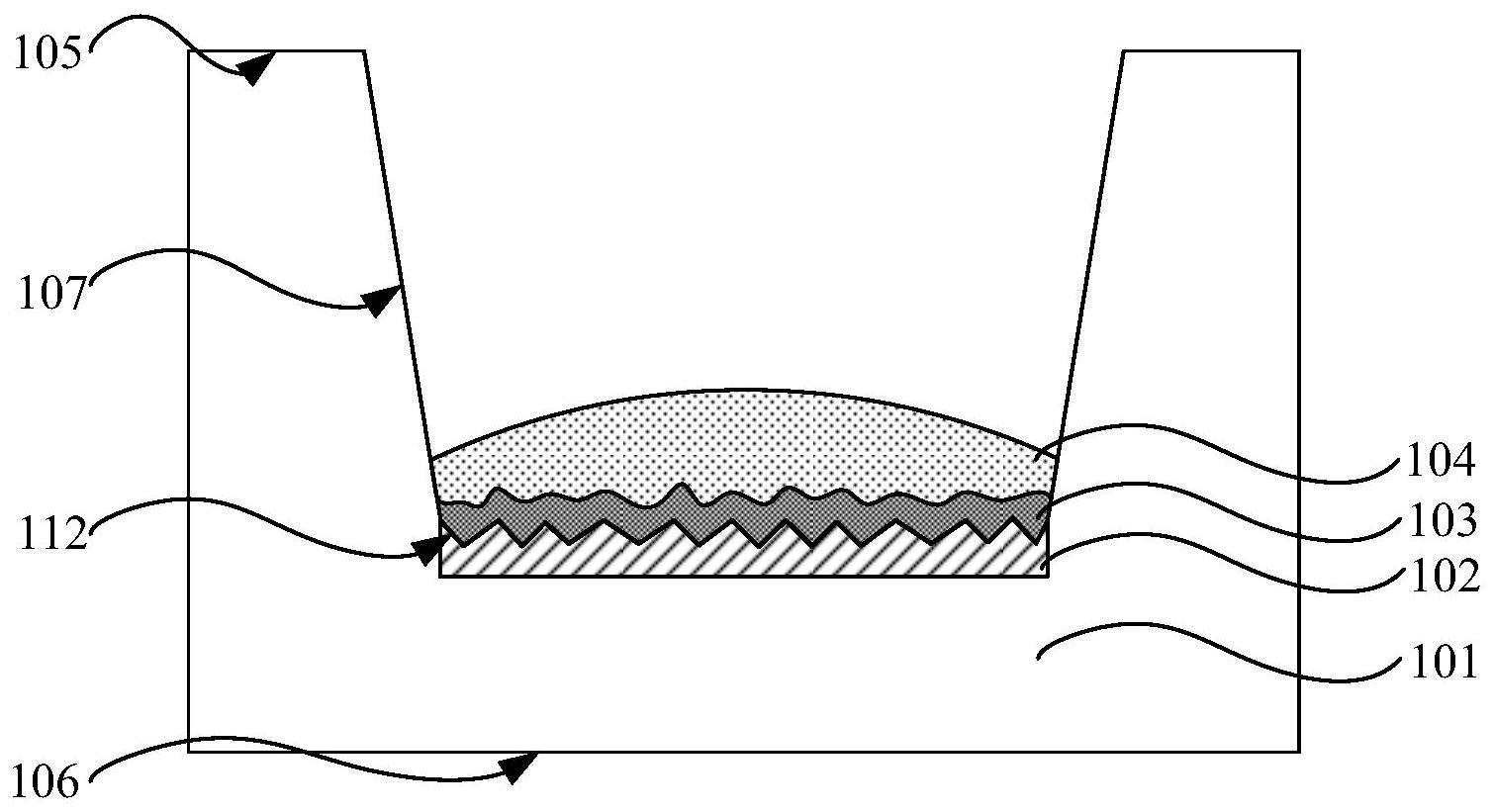

2、根据本公开一些实施例,本公开实施例一方面提供一种半导体结构,包括:基底,基底表面具有焊盘,焊盘远离基底的一侧具有凹凸表面;镀层,镀层位于焊盘的表面,镀层覆盖凹凸表面;焊球,焊球位于镀层的表面。

3、在一些实施例中,镀层远离的焊盘的表面具有第一粗糙度,焊盘上的凹凸表面具有第二粗糙度,第一粗糙度大于或等于第二粗糙度。

4、在一些实施例中,镀层的材料与焊球的材料相同。

5、根据本公开一些实施例,本公开实施例另一方面还提供一种半导体结构的制造方法,包括:提供基底,基底表面具有焊盘;对焊盘进行预处理,预处理用于使焊盘的表面为凹凸表面;形成镀层,镀层位于焊盘表面,镀层覆盖凹凸表面。

6、在一些实施例中,焊盘的表面具有杂质层,对焊盘进行预处理之前,还包括:去除杂质层。

7、在一些实施例中,焊盘的表面具有杂质层,预处理包括:去除杂质层;对焊盘进行粗糙化处理,以使焊盘的表面为凹凸表面;其中,去除杂质层与粗糙化处理为同一设备。

8、在一些实施例中,去除杂质层的同时,对焊盘进行粗糙化处理。

9、在一些实施例中,去除所述杂质层时,保留部分所述杂质层作为残留杂质层。

10、在一些实施例中,未经过预处理的焊盘的表面具有第三粗糙度,经过预处理后的焊盘的表面具有第二粗糙度,第二粗糙度大于第三粗糙度。

11、在一些实施例中,采用气相沉积工艺形成镀层。

12、本公开实施例提供的技术方案至少具有以下优点:

13、本公开实施例提供的半导体结构中,基底表面具有焊盘,焊盘远离基底的一侧具有凹凸表面,镀层位于焊盘的表面,且覆盖凹凸表面。凹凸表面的表面形貌能够提供较大的接触面积,有利于提高焊盘与镀层的接合效果。此外,凹凸表面在一定程度上能够吸收镀层的材料冷却时产生的拉伸应力,使得镀层不易产生裂纹,降低焊盘被杂质污染或被杂质腐蚀的风险,且焊盘在一段时间的保存后还能具有良好的表面质量,维持焊盘的良好的焊接性,使得半导体结构具有良好的可靠性。焊球位于镀层的表面,可以作为引线与镀层连接的媒介,且镀层与焊球可以具有较大的接合面积,镀层与焊球的接合效果得到提升,进而引线的可靠性也得到提高。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,所述镀层远离的所述焊盘的表面具有第一粗糙度,所述焊盘上的所述凹凸表面具有第二粗糙度,所述第一粗糙度大于或等于所述第二粗糙度。

3.根据权利要求1所述的半导体结构,其特征在于,所述镀层的材料与所述焊球的材料相同。

4.一种半导体结构的制造方法,其特征在于,包括:

5.根据权利要求4所述的半导体结构的制造方法,其特征在于,所述焊盘的表面具有杂质层,对所述焊盘进行预处理之前,还包括:去除所述杂质层。

6.根据权利要求5所述的半导体结构的制造方法,其特征在于,所述焊盘的表面具有杂质层,所述预处理包括:去除所述杂质层;对所述焊盘进行粗糙化处理,以使所述焊盘的表面为凹凸表面;其中,去除所述杂质层与所述粗糙化处理为同一设备。

7.根据权利要求5所述的半导体结构的制造方法,其特征在于,去除所述杂质层的同时,对所述焊盘进行粗糙化处理。

8.根据权利要求5至7任一项所述的半导体结构的制造方法,其特征在于,去除所述杂质层时,保留部分所述杂质层作为残留杂质层。

9.根据权利要求4至8任一项所述的半导体结构的制造方法,其特征在于,未经过所述预处理的所述焊盘的表面具有第三粗糙度,经过所述预处理后的所述焊盘的表面具有第二粗糙度,所述第二粗糙度大于所述第三粗糙度。

10.根据权利要求9所述的半导体结构的制造方法,其特征在于,采用气相沉积工艺形成所述镀层。

技术总结

本公开实施例涉及半导体领域,提供一种半导体结构及其制造方法,半导体结构包括:基底,所述基底表面具有焊盘,所述焊盘远离所述基底的一侧具有凹凸表面;镀层,所述镀层位于所述焊盘的表面,所述镀层覆盖所述凹凸表面;焊球,所述焊球位于所述镀层的表面。本公开实施例提供的半导体结构及其制造方法有利于提高半导体结构的良率。

技术研发人员:王隽,吴玉雷

受保护的技术使用者:长鑫科技集团股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!