一种三维堆叠板级扇出型封装结构与工艺的制作方法

:本发明属于半导体芯片的封装,特别涉及一种三维堆叠板级扇出型封装结构与工艺。

背景技术

0、

背景技术:

1、随着集成电路工艺节点逼近物理极限,芯片制造工艺成本呈指数级上升,同时良率也难以保证,除了继续下探集成电路制造工艺的物理极限外,更多行业者开始聚焦于先进封装,通过多芯片集成实现性能相当的封装结构,从芯片封装的角度开辟了新赛道,实现成本的大幅度降低和良率的极大提升。

2、在诸多先进封装技术中,扇出型封装技术的开发和拓展,是实现上述目标的关键一环。由于封装技术的先进性,晶圆级扇出型封装一直以来都面临封装成本较高的问题,使得该项技术无法大范围普及,特别是针对中低端芯片封装领域。为了解决封装成本高居不下的问题,越来越多的人开始聚焦于板级扇出封装,得益于面积远超于晶圆的封装平台,板级扇出封装技术在一定程度上解决了晶圆级扇出性封装的成本问题。

3、目前,板级扇出型封装尚处于早期的开发阶段,大多适配于2d平面的产品封装,受限于超大面积的尺寸效应,板级扇出型封装在三维堆叠方面一直进展缓慢。基于大板级平台,如何设计出稳定高效的三维堆叠封装结构,是先进封装领域面临的一大难题。目前,包括晶圆级扇出封装在内的诸多封装技术,针对三维纵向的解决方案,大多采用“依此封装、逐层封装”的思路,即先完成芯片重分布、正面线路增层后,再翻转封装结构,搭配使用临时键合技术,完成背面的线路增层,实现三维纵向互联。而这样的工艺与结构存在封装效率不高,封装周期时间长、成本高等问题。

4、公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现思路

0、

技术实现要素:

1、本发明的目的在于提供一种三维堆叠板级扇出型封装结构与工艺,从而克服上述现有技术中的缺陷。

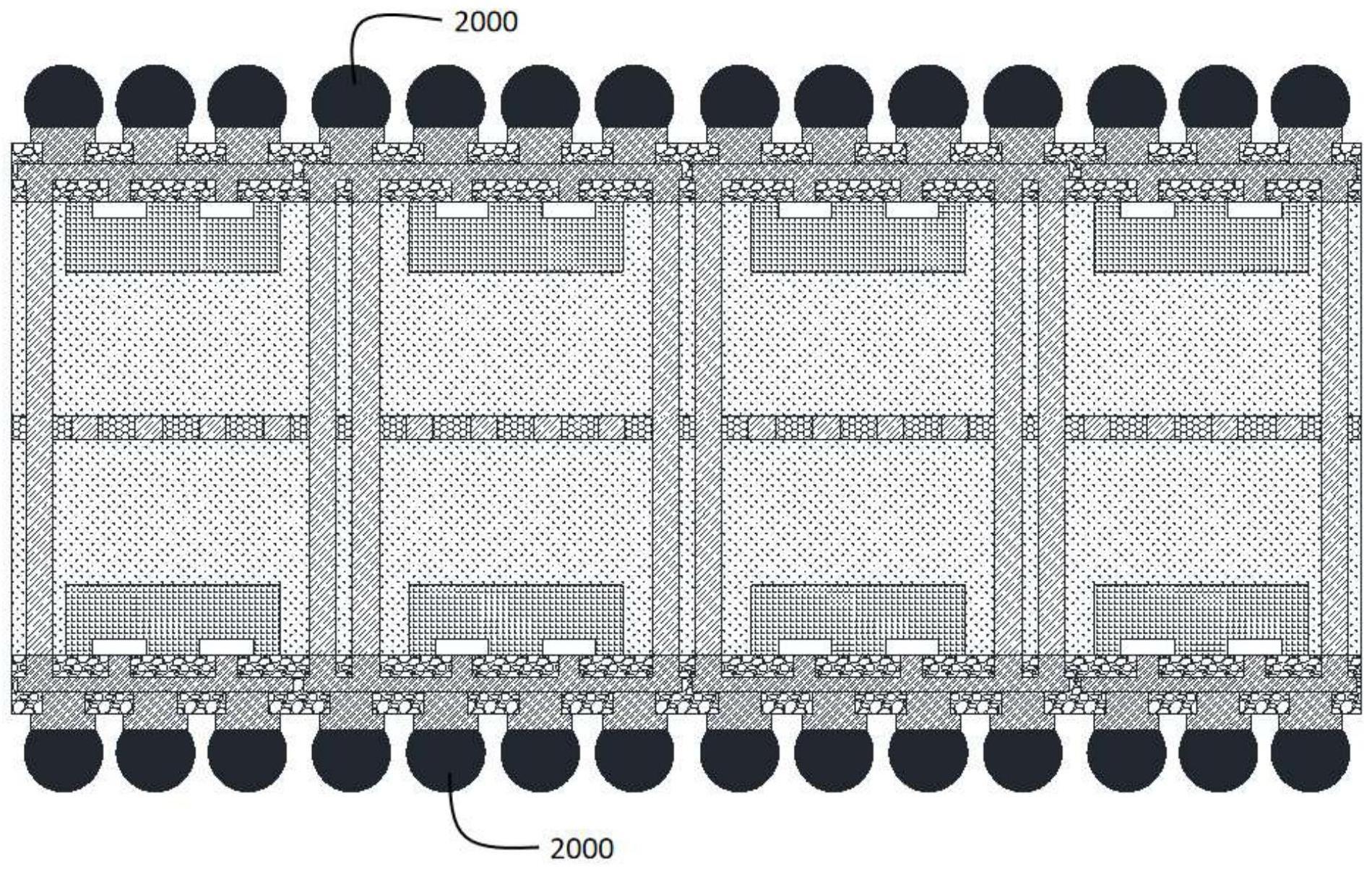

2、为了实现上述目的,本发明提供了一种三维堆叠板级扇出型封装结构,其特征在于,包括:

3、第一芯片封装体;

4、第二芯片封装体,所述第一芯片封装体和第二芯片封装体背靠背键合;

5、导电铜柱,所述导电铜柱贯穿第一芯片封装体和第二芯片封装体;

6、第一重布线层,布置在第一芯片封装体的正面;

7、第二重布线层,布置在第二芯片封装体的正面。

8、进一步的,作为优选,所述第一芯片封装体包括第一芯片和塑封第一芯片的第一塑封体;所述第二芯片封装体包括第二芯片和塑封第二芯片的第二塑封体。

9、进一步的,作为优选,所述第一芯片和第二芯片为相同的芯片或者不同的芯片。

10、进一步的,作为优选,所述第一芯片封装体和第二芯片封装体背靠背键合时通过金属凸点焊接键合或者通过键合胶永久键合。

11、本发明还提供一种三维堆叠板级扇出型封装工艺,包括以下步骤:

12、s1:准备临时载板,在临时载板上附着临时键合层;

13、s2:在临时键合层上贴芯片,芯片的正面朝下;

14、s3:对芯片进行塑封,形成第一芯片封装体;

15、s4:在第一芯片封装体上形成贯穿的通孔,并在通孔内填充导电铜柱;

16、s5:按照上述步骤再准备一个结构相同的组合体作为第二芯片封装体;

17、s6:对第一芯片封装体、第二芯片封装体进行背靠背键合,键合时通过导电铜柱对位;

18、s7:解除第一芯片封装体、第二芯片封装体的临时键合层;

19、s8:分别在第一芯片封装体、第二芯片封装体的另外一面制备重布线层;

20、s9:在重布线层上制备信号导出结构。

21、进一步的,作为优选,所述s1中临时载板采用不锈钢钢板、玻璃板、树脂板或者复合板,厚度为0.5-2mm。

22、进一步的,作为优选,所述第一芯片封装体的芯片和第二芯片封装体的芯片相同或者不同。

23、进一步的,作为优选,所述s4中通孔采用激光钻孔、机械钻孔、干湿法刻蚀的方式形成。

24、进一步的,作为优选,所述s4中通孔在第一芯片封装体、第二芯片封装体背靠背键合完成后制作。

25、进一步的,作为优选,所述s6中第一芯片封装体和第二芯片封装体背靠背键合时通过金属凸点焊接键合或者通过键合胶永久键合。

26、与现有技术相比,本发明的一个方面具有如下有益效果:

27、(1)本发明采用背靠背的方式将第一芯片封装体和第二芯片封装体进行键合,再分别在两面制作重布线和信号引出结构,可以实现芯片布局的多样化设计,并且可以取消传统的二次塑封程序,可以提高封装质量和封装效率;

28、(2)本发明预先完成第一芯片封装体和第二芯片封装体的制备,再将两者进行键合,键合后的整体拥有较高的结构强度,在制作重布线层时无需再使用临时载板,既可以降低物料成本,又可以双面同时作业。

29、(3)本发明相较于传统的“正反面逐层增层”的方案,可以显著提高封装效率。

技术特征:

1.一种三维堆叠板级扇出型封装结构,其特征在于,包括:

2.根据权利要求1所述的一种三维堆叠板级扇出型封装结构,其特征在于,所述第一芯片封装体包括第一芯片和塑封第一芯片的第一塑封体;所述第二芯片封装体包括第二芯片和塑封第二芯片的第二塑封体。

3.根据权利要求2所述的一种三维堆叠板级扇出型封装结构,其特征在于,所述第一芯片和第二芯片为相同的芯片或者不同的芯片。

4.根据权利要求1所述的一种三维堆叠板级扇出型封装结构,其特征在于,所述第一芯片封装体和第二芯片封装体背靠背键合时通过金属凸点焊接键合或者通过键合胶永久键合。

5.一种三维堆叠板级扇出型封装工艺,其特征在于,包括以下步骤:

6.根据权利要求5所述的一种三维堆叠板级扇出型封装工艺,其特征在于,所述s1中临时载板采用不锈钢钢板、玻璃板、树脂板或者复合板,厚度为0.5-2mm。

7.根据权利要求5所述的一种三维堆叠板级扇出型封装工艺,其特征在于,所述第一芯片封装体的芯片和第二芯片封装体的芯片相同或者不同。

8.根据权利要求5所述的一种三维堆叠板级扇出型封装工艺,其特征在于,所述s4中通孔采用激光钻孔、机械钻孔、干湿法刻蚀的方式形成。

9.根据权利要求5所述的一种三维堆叠板级扇出型封装工艺,其特征在于,所述s4中通孔在第一芯片封装体、第二芯片封装体背靠背键合完成后制作。

10.根据权利要求5所述的一种三维堆叠板级扇出型封装工艺,其特征在于,所述s6中第一芯片封装体和第二芯片封装体背靠背键合时通过金属凸点焊接键合或者通过键合胶永久键合。

技术总结

本发明公开了一种三维堆叠板级扇出型封装结构与工艺,该结构包括:第一芯片封装体;第二芯片封装体,第一芯片封装体和第二芯片封装体背靠背键合;导电铜柱,所述导电铜柱贯穿第一芯片封装体和第二芯片封装体;第一重布线层,布置在第一芯片封装体的正面;第二重布线层,布置在第二芯片封装体的正面。本发明采用背靠背的方式将两个芯片封装体进行键合,再分别在两面制作重布线和信号引出结构,可以实现芯片布局的多样化设计,并且可以取消传统的二次塑封程序;同时背靠背键合后的整体拥有较高的结构强度,在制作重布线层时无需再使用临时载板,既可以降低物料成本,又可以双面同时作业;相较于传统的逐层增层方案,可以显著提高封装效率。

技术研发人员:刘苏,马书英,王姣

受保护的技术使用者:华天科技(江苏)有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!