一种高密度IC封装载板的制作方法

本发明涉及芯片封装,具体为一种高密度ic封装载板。

背景技术:

1、传统8脚ic封装通常采用sop8引线框架进行封装,sop封装工艺是一种表面贴装型(smd)封装制造工艺。 sop封装工艺流程为:首先晶圆减薄、晶圆划片,然后将ic芯片粘贴在sop引线框架的载体上,经过烘烤后,键合(打线)使芯片与芯片、 芯片与内引脚相连接,再经过塑封将芯片、键合线、内引脚等包封,最后通过后固化、打标、电镀、切筋引脚折弯成型、测试,完成整个sop生产工艺过程。传统引线框架在目前的芯片封装过程中,从芯片粘片、引线键合、塑封、引脚电镀、切割引脚折弯成型,要经过多道工序,需要使用多种不同类型的半导体设备,造成巨额的运行成本,由于环节过多,导致芯片封装周期长,且传统引线框架因后期需折弯引脚设计较长,占用引线框架空间大,由此可见材料单颗密度不高,使得框架基板利用率不高。

技术实现思路

1、本发明的目的在于提供一种高密度ic封装载板,提升载板单颗成品密度,精简封装流程、缩短加工周期,降低企业运营成本。

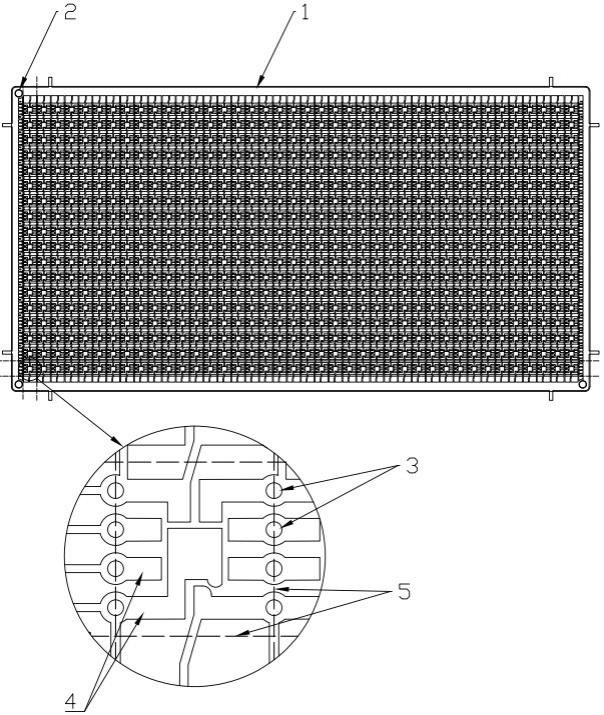

2、本发明采用的技术方案如下:一种高密度ic封装载板,包括基板和导电铜层,在所述基板上阵列分布有若干个封装单元,每个封装单元的正面由多个独立、隔断的导电铜层形成对应数量的导电板功能区,在基板上每个封装单元的两侧设有多个通孔,所述通孔内设有侧铜壁,通孔的数量与导电板功能区数量一致,并且每个导电板功能区的导电铜层对应连接其中一个通孔侧铜壁,每个封装单元的背面设有与通孔一一对应的由导电铜层形成的引脚焊盘,且引脚焊盘的导电铜层与对应通孔侧铜壁连通,每个封装单元两侧的切割线与多个通孔的中心线重合。

3、进一步地,所述导电板功能区、通孔侧铜壁、背面引脚焊盘的导电铜层包括底层的铜层,在铜层上镀有镍层,在镍层上镀有银层。

4、进一步地,所述基板为bt树脂基板。

5、进一步地,所述基板的3个角上设有用于后期塑封模具定位用的定位孔。

6、进一步地,所述导电板功能区、通孔、引脚焊盘的数量均为8个,8个导电板功能区分别为1个大导电板功能区与7个小导电板功能区,芯片固定安装于大导电板功能区上。

7、本发明带来的有益效果为:本发明的ic封装载板正面设有若干个产品封装单元,每个封装单元设有隔断独立的导电板功能区,导电板功能区通过两侧通孔内设有的侧铜壁与载板背面引脚焊盘相连接,通过在每个封装单元大导电板固上ic芯片,再通过引线键合、塑封、切割后即形成若干个半导体器件,可直接通过后续电性测试包装完成了整个封装流程,无需再进行引脚电镀及引脚折弯成型,省去了引脚电镀、引脚折弯等工序,精简了封装流程,缩短了加工周期,提升了生产效率,节约了成本。

技术特征:

1.一种高密度ic封装载板,包括基板(1)和导电铜层,其特征在于:在所述基板(1)上阵列分布有若干个封装单元,每个封装单元的正面由多个独立、隔断的导电铜层形成对应数量的导电板功能区(4),在基板(1)上每个封装单元的两侧设有多个通孔(3),所述通孔(3)内设有侧铜壁,通孔(3)的数量与导电板功能区(4)数量一致,并且每个导电板功能区(4)的导电铜层对应连接其中一个通孔(3)侧铜壁,每个封装单元的背面设有与通孔(3)一一对应的由导电铜层形成的引脚焊盘(6),且引脚焊盘(6)的导电铜层与对应通孔(3)侧铜壁连通,每个封装单元两侧的切割线(5)与多个通孔(3)的中心线重合。

2.如权利要求1所述的一种高密度ic封装载板,其特征在于:所述导电板功能区(4)、通孔(3)侧铜壁、背面引脚焊盘(6)的导电铜层包括底层的铜层,在铜层上镀有镍层,在镍层上镀有银层。

3.如权利要求1所述的一种高密度ic封装载板,其特征在于:所述基板(1)为bt树脂基板(1)。

4.如权利要求1所述的一种高密度ic封装载板,其特征在于:所述基板(1)的3个角上设有用于后期塑封模具定位用的定位孔(2)。

5.如权利要求1-4任意一项所述的一种高密度ic封装载板,其特征在于:所述导电板功能区(4)、通孔(3)、引脚焊盘(6)的数量均为8个,8个导电板功能区(4)分别为1个大导电板功能区(4)与7个小导电板功能区(4),芯片固定安装于大导电板功能区(4)上。

技术总结

本发明公开了一种高密度IC封装载板,包括基板和导电铜层,在所述基板上阵列分布有若干个封装单元,每个封装单元的正面由多个独立、隔断的导电铜层形成对应数量的导电板功能区,在基板上每个封装单元的两侧设有多个通孔,所述通孔内设有侧铜壁,通孔的数量与导电板功能区数量一致,并且每个导电板功能区的导电铜层对应连接其中一个通孔侧铜壁,每个封装单元的背面设有与通孔一一对应的由导电铜层形成的引脚焊盘,且引脚焊盘的导电铜层与对应通孔侧铜壁连通,每个封装单元两侧的切割线与多个通孔的中心线重合。本发明的IC封装载板省去了引脚电镀、引脚折弯等工序,精简了封装流程,缩短了加工周期,提升了生产效率,节约了成本。

技术研发人员:王桂,胡良峰,周维

受保护的技术使用者:江西天佑半导体有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!