嵌入式线路结构成型方法及嵌入式线路结构与流程

本发明涉及集成电路封装,具体涉及一种嵌入式线路结构成型方法及嵌入式线路结构。

背景技术:

1、在传统的集成电路封装技术中,芯片贴片、塑封后需要制备线路层,将芯片的i/o口电性引出。其中,线路层的制备通常包括以下步骤:

2、步骤1、对芯片塑封层开通孔处理;

3、步骤2、通过真空溅射在芯片塑封层的表面以及通孔内壁形成种子层;

4、步骤3、在通孔内壁电镀沉积导电柱,同时在种子层上电镀沉积与导电柱电连接的铜层;

5、步骤4、在铜层上贴菲林,然后蚀刻掉部分铜层和种子层,形成线路层。

6、采用上述制备方法制备线路层时,需要做减铜处理,工艺流程繁琐。

技术实现思路

1、本发明的目的之一在于提供一种嵌入式线路结构成型方法,可以使线路槽和通孔一体成型,制作线路结构时无需做减铜处理。

2、为达此目的,本发明采用以下技术方案:

3、提供一种嵌入式线路结构成型方法,包括以下步骤:

4、s10、选用玻璃板作为基板,对基板的部分区域进行激光改性;

5、s20、在基板的双面溅射一铜层,采用雕刻液对铜层的部分区域进行雕刻,形成第一图形化窗口,并使基板的激光改性区域外露于所述第一图形化窗口;

6、s30、对基板进行刻蚀处理,在激光改性区域形成通孔以及在第一图形化窗口处的非激光改性区域形成嵌入式线路槽;

7、s40、同步在通孔内以及基板双面的嵌入式线路槽内制备嵌入式线路结构。

8、本方案首先对玻璃材质的基板进行激光改性,然后溅射铜层,具体可以通过真空溅射或者化学溅射的方式制作铜层,铜层的厚度可以为1纳米-10微米,采用雕刻液对铜层的部分区域进行雕刻,形成第一图形化窗口,并使激光改性区域外露于第一图形化窗口,此时第一图形化窗口内的基板同时具有激光改性区域和非激光改性区域;随后进行刻蚀,并通过控制刻蚀速率,可以直接在激光改性区域形成通孔,并且非激光改性区域同步刻蚀下沉形成嵌入式线路槽。通过本方案,可以使通孔和嵌入式线路槽成型,制作工艺简单。通过刻蚀形成的通孔的侧壁和嵌入式线路槽的侧壁具有一定的粗糙度,在后续制备线路结构时可以增加线路结合力,并且不需要做减铜处理。

9、本发明中,步骤s20中对玻璃基板进行刻蚀处理所采用的刻蚀液由氢氟酸和添加剂组成。

10、具体地,按照中国专利cn113045209a中公开的方法对玻璃基板开设通孔和嵌入式线路槽。

11、作为嵌入式线路结构成型方法的一种优选方案,步骤s30中,基板的激光改性区域和非激光改性区域的刻蚀速率比为20:1,从而可以实现嵌入式线路槽和通孔一体成型,且嵌入式线路槽的深度较浅,适合线路的制备。

12、作为嵌入式线路结构成型方法的一种优选方案,步骤s40具体包括以下步骤:

13、s40a、采用雕刻液去除残留的铜层,在嵌入式线路槽表面以及通孔内壁制作种子层;

14、s40b、在基板表面及嵌入式线路槽表面的种子层上压感光膜,并对感光膜进行曝光显影处理,形成第二图形化窗口;

15、s40c、在通孔内制作铜柱以及同时在第二图形化窗口内制作与铜柱电连接的重布线层,并使重布线层的表面与基板的表面平齐;

16、s40d、去除残留的感光膜并对外露的种子层进行闪蚀处理,制得嵌入式线路结构。

17、作为嵌入式线路结构成型方法的一种优选方案,所述雕刻液由5-10wt%硫酸和1-10wt%双氧水组成。

18、作为嵌入式线路结构成型方法的一种优选方案,步骤s40b中,形成第二图形化窗口之后,采用plasma蚀刻掉第二图形化窗口内残留的感光膜。

19、本发明的目的之二在于提供一种采用所述的成型方法制得的嵌入式线路结构。

20、具体地,本发明的嵌入式线路结构包括:

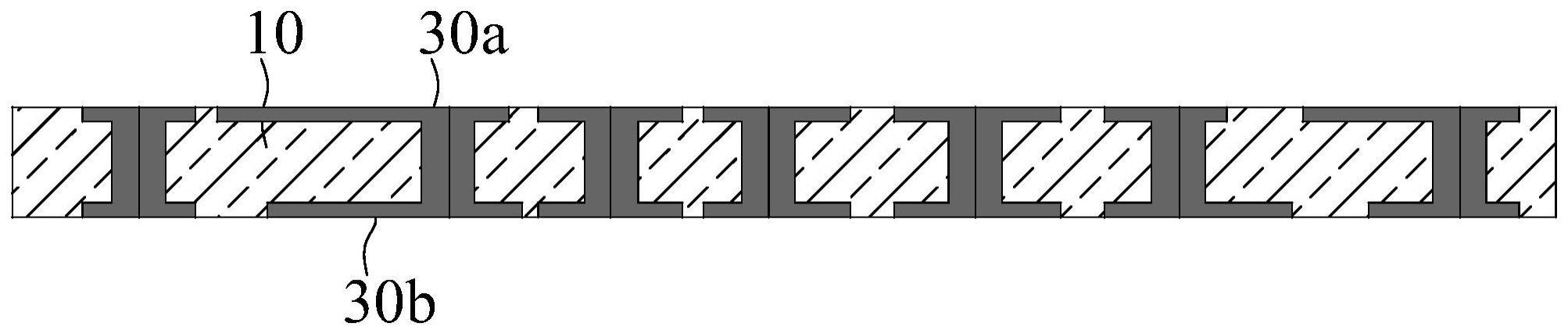

21、玻璃材质的基板,所述基板开设有通孔和位于所述基板双面的嵌入式线路槽,所述嵌入式线路槽与所述通孔连接;

22、嵌入式线路,包括嵌入至所述通孔内的导电柱和嵌入至所述嵌入式线路槽内的线路层,所述导电柱与所述线路层电连接,且所述线路层的表面与所述基板的表面平齐。

23、作为嵌入式线路结构的一种优选方案,所述导电柱包括覆盖所述通孔内壁的第一种子层和填充于所述通孔内并与所述第一种子层连接的铜柱,所述线路层包括位于所述嵌入式线路槽内的第二种子层和位于所述第二种子层表面的重布线层,所述重布线层与所述铜柱电连接。

24、作为嵌入式线路结构的一种优选方案,所述第一种子层和所述第二种子层通过真空溅射一体成型。

25、作为嵌入式线路结构的一种优选方案,所述铜柱和所述重布线层通过电镀沉积一体成型。

26、本发明的有益效果:

27、本发明首先对玻璃材质的基板进行激光改性,然后溅射铜层并采用雕刻液对铜层部分区域进行雕刻形成第一图形化窗口,并使激光改性区域外露于第一图形化窗口,此时第一图形化窗口内的基板同时具有激光改性区域和非激光改性区域;随后进行刻蚀,并通过控制刻蚀速率,可以直接在激光改性区域形成通孔,并且非激光改性区域同步刻蚀下沉形成嵌入式线路槽。通过本方案,可以使通孔和嵌入式线路槽一体成型,制作工艺简单。

28、通过刻蚀形成的通孔的侧壁和嵌入式线路槽的侧壁具有一定的粗糙度,在后续制备线路结构时可以增加线路结合力,并且不需要做减铜处理。

技术特征:

1.一种嵌入式线路结构成型方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的嵌入式线路结构成型方法,其特征在于,步骤s30中,基板的激光改性区域和非激光改性区域的刻蚀速率比为20:1。

3.根据权利要求1所述的嵌入式线路结构成型方法,其特征在于,步骤s40具体包括以下步骤:

4.根据权利要求3所述的嵌入式线路结构成型方法,其特征在于,所述雕刻液由5-10wt%硫酸和1-10wt%双氧水组成。

5.根据权利要求3所述的嵌入式线路结构成型方法,其特征在于,步骤s40b中,形成第二图形化窗口之后,采用plasma蚀刻掉第二图形化窗口内残留的感光膜。

6.一种嵌入式线路结构,采用权利要求1-5任一项所述的成型方法制得,其特征在于,包括:

7.根据权利要求6所述的嵌入式线路结构,其特征在于,所述导电柱包括覆盖所述通孔内壁的第一种子层和填充于所述通孔内并与所述第一种子层连接的铜柱,所述线路层包括位于所述嵌入式线路槽内的第二种子层和位于所述第二种子层表面的重布线层,所述重布线层与所述铜柱电连接。

8.根据权利要求7所述的嵌入式线路结构,其特征在于,所述第一种子层和所述第二种子层通过真空溅射一体成型。

9.根据权利要求7所述的嵌入式线路结构,其特征在于,所述铜柱和所述重布线层通过电镀沉积一体成型。

技术总结

本发明公开一种嵌入式线路结构成型方法及嵌入式线路结构,涉及集成电路封装技术领域。其中,嵌入式线路结构成型方法包括以下步骤:S10、选用玻璃板作为基板,对基板的部分区域进行激光改性;S20、在基板的双面溅射一铜层,采用雕刻液对铜层的部分区域进行雕刻,形成第一图形化窗口,并使基板的激光改性区域外露于所述第一图形化窗口;S30、对基板进行刻蚀处理,在激光改性区域形成通孔以及在第一图形化窗口处的非激光改性区域形成嵌入式线路槽;S40、同步在通孔内以及基板双面的嵌入式线路槽内制备嵌入式线路结构。采用本发明的嵌入式线路结构成型方法可以使线路槽和通孔一体成型,制作线路结构时无需做减铜处理。

技术研发人员:杨斌,何健豪,杜毅嵩,华显刚

受保护的技术使用者:广东佛智芯微电子技术研究有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!