半导体结构及其形成方法与流程

本申请的实施例涉及半导体结构及其形成方法。

背景技术:

1、半导体集成电路(ic)工业经历了指数级增长。ic材料和设计中的技术进步已经产生了多代ic,其中每一代都具有比上一代更小且更复杂的电路。在ic发展的过程中,功能密度(即,每芯片区的互连器件的数量)普遍增大,而几何尺寸(即,可以使用制造工艺创建的最小组件(或线))已经减小。这种缩小工艺通常通过提高生产效率和降低相关成本来提供益处。这样的缩小也增加了ic处理和制造的复杂性,并且为了实现这些进步,需要ic处理和制造中的类似发展。例如,电容器(作为无源器件)是集成电路中的重要器件,并且广泛用于各种目的,诸如在随机存取存储器(ram)、非易失性存储器器件、去耦电容器或rc电路中。当ic转移至具有更小部件尺寸的先进技术节点时,电容器几乎是不可收缩的,并且由于电容器特性而不能缩小至较小尺寸。电容器承受了相当大的电路区损失。此外,现有的制造电容器的方法将缺陷引入电容器中,并且造成不期望的问题,诸如应力和引起的晶圆翘曲。因此,期望提供集成有其它电路器件的电容器结构及其制造方法,而不存在上面讨论的缺点。

技术实现思路

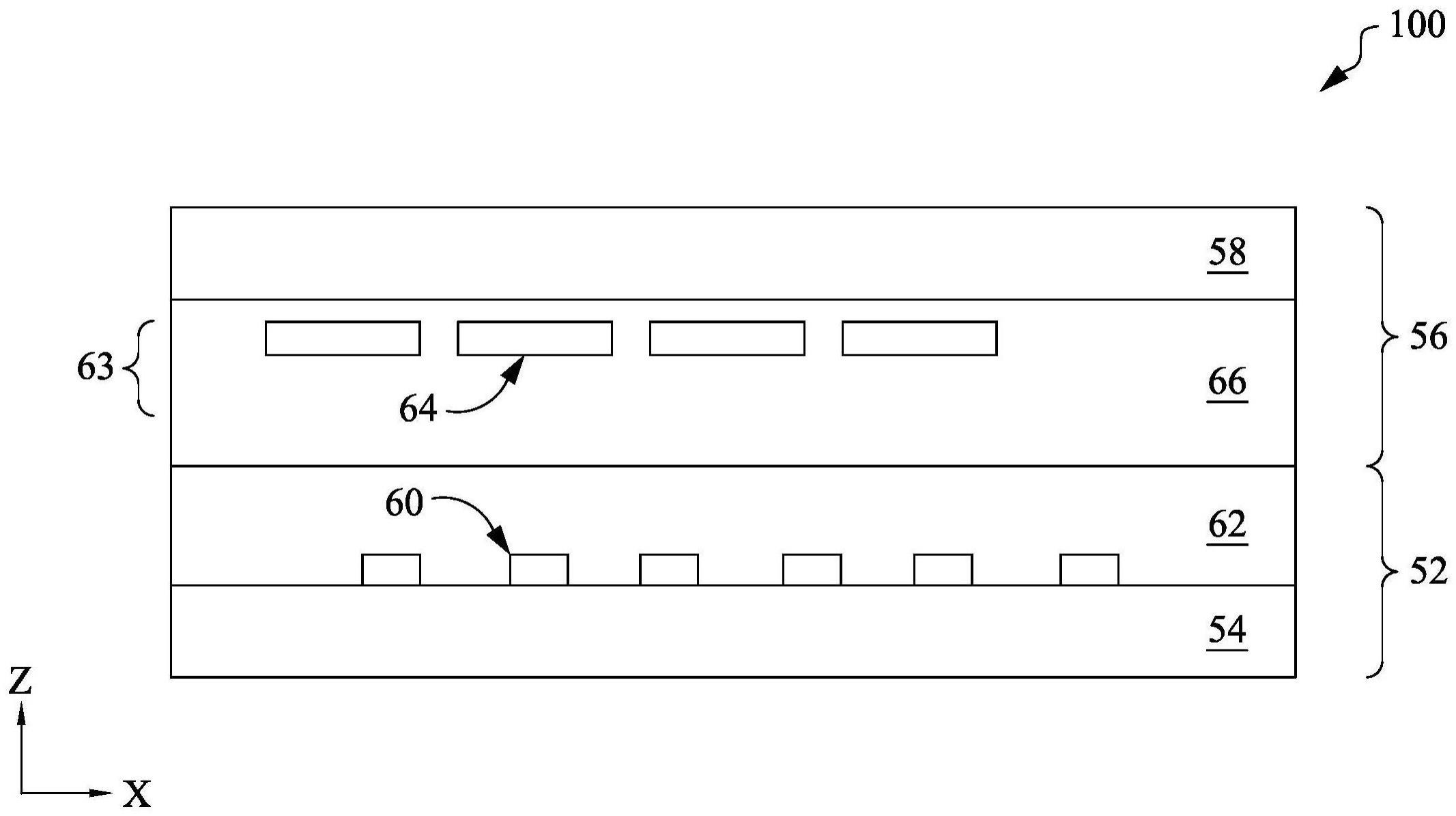

1、本申请的一些实施例提供了一种形成半导体结构的方法,包括:图案化衬底以形成沟槽;蚀刻所述衬底,从而将所述沟槽修改为具有圆形尖端;在所述沟槽中形成包括导电层和介电层的堆叠件,其中,所述导电层和所述介电层在所述堆叠件内彼此交替;在所述第一沟槽中形成绝缘压缩膜,从而密封所述沟槽中的空隙;以及形成分别连接至所述导电层的导电插塞。

2、本申请的另一些实施例提供了一种形成半导体结构的方法,包括:图案化衬底以形成深沟槽;蚀刻所述衬底,从而修改所述深沟槽;形成包括在所述沟槽中交替堆叠和折叠的导电层和介电层的堆叠件;以及在所述第一沟槽中形成绝缘膜,从而密封所述深沟槽中的空隙,其中,所述深沟槽配置为多个深沟槽单位单元,其中,所述深沟槽单位单元的每个中的所述深沟槽在相同方向上取向,并且其中,相邻深沟槽单位单元中的所述深沟槽在不同方向上取向。

3、本申请的又一些实施例一种半导体结构,包括:多个深沟槽,形成在衬底上;导电层和介电层的堆叠件,交替设置在所述多个深沟槽中;以及导电插塞,分别接合在所述导电层上,其中,所述深沟槽配置为多个深沟槽单位单元,并且其中,所述深沟槽单位单元的每个中的所述多个深沟槽在相同方向上取向。

技术特征:

1.一种形成半导体结构的方法,包括:

2.根据权利要求1所述的方法,其中,在所述沟槽中形成绝缘压缩膜包括在800℃和1200℃之间范围内的退火温度下在氧环境中实施退火工艺。

3.根据权利要求1所述的方法,其中,在所述沟槽中形成绝缘压缩膜包括形成氧化硅(sio2)层、氮化硅层、多晶硅层、碳化硅层和它们的组合中的至少一种。

4.根据权利要求1所述的方法,其中,在所述第一沟槽中形成绝缘压缩膜包括实施化学气相沉积工艺以形成所述绝缘压缩膜。

5.根据权利要求4所述的方法,其中,在所述第一沟槽中形成绝缘压缩膜包括形成无氮抗反射层(nfarl)、氧化硅(sio2)层、未掺杂的石英玻璃(usg)层、碳化硅层和它们的组合中的至少一种。

6.根据权利要求1所述的方法,其中,

7.根据权利要求6所述的方法,其中,蚀刻所述衬底包括:

8.根据权利要求1所述的方法,其中,图案化衬底以形成沟槽包括图案化所述衬底以形成配置为多个深沟槽单位单元的所述沟槽,其中,所述深沟槽单位单元的每个包括在相同方向上取向的多个深沟槽。

9.一种形成半导体结构的方法,包括:

10.一种半导体结构,包括:

技术总结

本公开实施例提供了方法的实施例。方法包括:图案化衬底以形成沟槽;蚀刻衬底,从而将沟槽修改为具有圆形尖端;在沟槽中形成包括导电层和介电层的堆叠件,其中,导电层和介电层在堆叠件内彼此交替;在第一沟槽中形成绝缘压缩膜,从而密封沟槽中的空隙;以及形成分别连接至导电层的导电插塞。本申请的实施例还涉及半导体结构及其形成方法。

技术研发人员:郭富强,陈信良,郑新立,许庭祯

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!