填充沟槽的方法与流程

本申请涉及半导体加工,尤其涉及一种填充沟槽的方法。

背景技术:

1、目前,半导体集成电路通常包含隔离结构,相邻两隔离结构之间定义出有源区,这些隔离结构在制造有源器件之前形成。伴随着半导体工艺进入深亚微米时代,半导体器件的隔离结构已大多采用浅沟槽隔离(shallow trench isolation,简称sti)工艺来制作。随着半导体技术的飞速发展,浅沟槽隔离工艺已经成为一种广泛应用于半导体器件制造过程中的器件隔离技术。

2、浅沟槽隔离工艺主要包括:在衬底上形成沟槽;采用等离子体技术在沟槽内填充介质。虽然浅沟槽隔离工艺形成的隔离结构拥有较佳的隔离特性;然而采用等离子体技术对沟槽填充形成隔离结构时,会对隔离结构造成较强的破坏,而产生大量的蚀刻缺陷,且具有尖锐角落的陡峭沟渠也会导致角落寄生漏电流,因而降低隔离结构的隔离效果。

技术实现思路

1、本申请所要解决的技术问题是提供一种填充沟槽的方法,可以降低寄生漏电流的产生,从而有效提供sti的隔离效果。

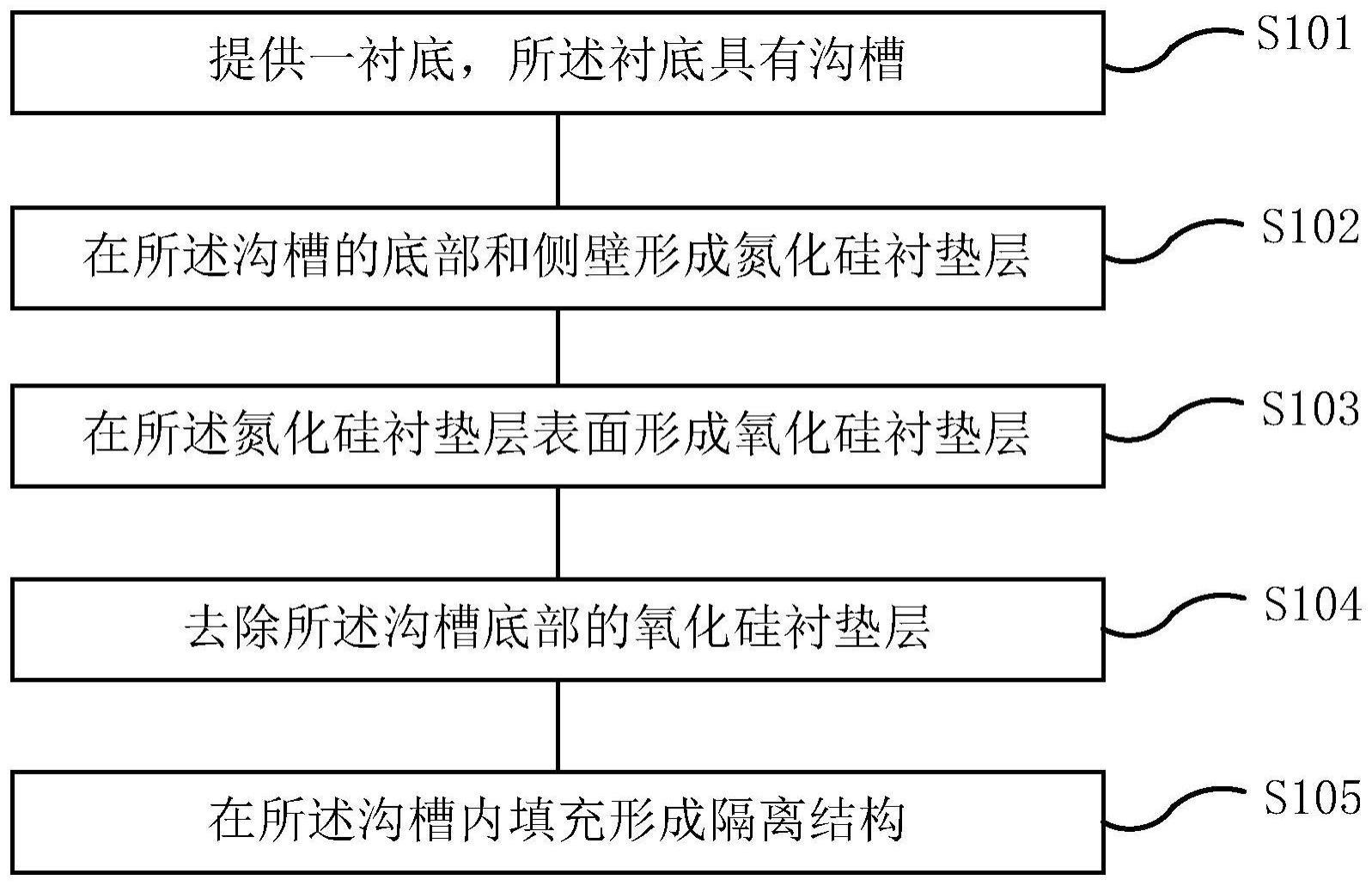

2、为了解决上述问题,本申请提供了一种填充沟槽的方法,包括如下步骤:提供一衬底,所述衬底具有沟槽;在所述沟槽的底部和侧壁形成氮化硅衬垫层;在所述氮化硅衬垫层表面形成氧化硅衬垫层;去除所述沟槽底部的氧化硅衬垫层;在所述沟槽内填充形成隔离结构。

3、在一些实施例中,形成所述沟槽的步骤包括:在一衬底表面形成氧化硅保护层;在所述氧化硅保护层表面形成氮化硅层;对所述氮化硅层、氧化硅保护层进行刻蚀形成硬掩膜层;以所述硬掩膜层为遮挡对所述衬底进行刻蚀以形成所述沟槽。

4、在一些实施例中,采用低压化学气相沉积的方法形成所述氮化硅衬垫层。

5、在一些实施例中,在温度700~800℃和压力0.2~0.3torr的条件下形成所述氮化硅衬垫层。

6、在一些实施例中,在所述沟槽的底部和侧壁形成所述氮化硅衬垫层后,对所述衬底进行快速热退火处理。

7、在一些实施例中,采用低压化学气相沉积的方法形成所述氧化硅衬垫层。

8、在一些实施例中,在温度720~900℃和压力0.1~0.9torr的条件下形成所述氧化硅衬垫层。

9、在一些实施例中,采用干法刻蚀去除所述沟槽底部的氧化硅衬垫层。

10、在一些实施例中,采用等离子体化学气相淀积的方法形成所述隔离结构。

11、在一些实施例中,所述隔离结构的材料为二氧化硅。

12、上述技术方案,通过在形成沟槽后,在所述沟槽内表面分别形成了氮化硅衬垫层和氧化硅衬垫层,又去除了沟槽底部的氧化硅衬垫层,仅保留侧壁的氧化硅衬垫层,从而形成了底部为氮化硅衬垫层和侧壁为氧化硅衬垫层的结构,在此基础上再对所述沟槽进行填充形成隔离结构,可以降低寄生漏电流的产生,提高抗击穿电压的能力,从而有效提高隔离结构的隔离效果。

13、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本申请。对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为授权说明书的一部分。

技术特征:

1.一种填充沟槽的方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的方法,其特征在于,形成所述沟槽的步骤进一步包括:

3.根据权利要求1所述的方法,其特征在于,采用低压化学气相沉积的方法形成所述氮化硅衬垫层。

4.根据权利要求3所述的方法,其特征在于,在温度700~800℃和压力0.2~0.3torr的条件下形成所述氮化硅衬垫层。

5.根据权利要求1所述的方法,其特征在于,在所述沟槽的底部和侧壁形成所述氮化硅衬垫层后,对所述衬底进行快速热退火处理。

6.根据权利要求1所述的方法,其特征在于,采用低压化学气相沉积的方法形成所述氧化硅衬垫层。

7.根据权利要求6所述的方法,其特征在于,在温度720~900℃和压力0.1~0.9torr的条件下形成所述氧化硅衬垫层。

8.根据权利要求1所述的方法,其特征在于,采用干法刻蚀去除所述沟槽底部的氧化硅衬垫层。

9.根据权利要求1所述的方法,其特征在于,采用等离子体化学气相淀积的方法形成所述隔离结构。

10.根据权利要求9所述的方法,其特征在于,所述隔离结构的材料为二氧化硅。

技术总结

本申请提供了一种填充沟槽的方法。所述方法包括如下步骤:提供一衬底,所述衬底具有沟槽;在所述沟槽的底部和侧壁形成氮化硅衬垫层;在所述氮化硅衬垫层表面形成氧化硅衬垫层;去除所述沟槽底部的氧化硅衬垫层;在所述沟槽内填充形成隔离结构。上述技术方案,通过在形成沟槽后,在所述沟槽内表面分别形成了氮化硅衬垫层和氧化硅衬垫层,又去除了沟槽底部的氧化硅衬垫层,仅保留侧壁的氧化硅衬垫层,从而形成了底部为氮化硅衬垫层和侧壁为氧化硅衬垫层的结构,在此基础上再对所述沟槽进行填充形成隔离结构,可以降低寄生漏电流的产生,提高抗击穿电压的能力,从而有效提高隔离结构的隔离效果。

技术研发人员:张强强,严翔,闫晓晖

受保护的技术使用者:上海积塔半导体有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!