半导体封装结构的制作方法

本发明所揭示内容是关于一种半导体封装结构;特别是,该半导体封装结构包括至少一个电子组件,该电子组件与soc结构和内存结构封装在一起。该soc结构包括片上系统(system on a chip)或系统芯片(system-of-chip)。系统芯片的特征在于具有堆叠的小芯片或是3d小芯片。透过利用所选的封装电子组件,整体封装结构可以提供与所选电子组件相对应的高性能能力。

背景技术:

1、半导体封装结构是指将半导体组件封装在保护外壳内,以保护其免于受到外部损害,并且便于将其整合至电子系统当中的过程。用于dram(动态随机存取内存)的封装结构通常包括一个包含内存单元的硅芯片被安装在导线架或是基板上。该芯片接着被密封在塑料或陶瓷封装中,以提供对湿气、灰尘和其他环境因素的保护。该封装还包括引脚或垫片,使dram能与电子系统中的其他组件间形成电性连接。

技术实现思路

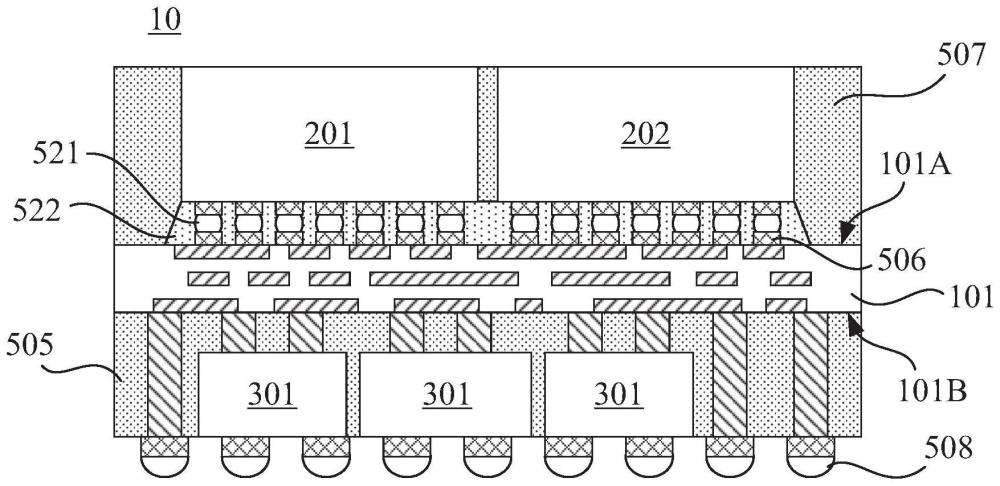

1、本发明在一种例示的态样中,提出一种半导体封装结构。所述半导体封装结构包括第一重分布结构、soc结构、内存结构、第一电子组件及第一封胶层。所述第一重分布结构具有第一侧及相对于第一侧的第二侧。所述soc结构位于第一重分布结构的第一侧上。所述内存结构相邻于soc结构,且其位于第一重分布结构的第一侧上。所述第一电子组件位于第一重分布结构的第二侧上,且其电性连接于soc结构或内存结构中至少的一者。所述第一封胶层封胶第一电子组件。另外,第一电子组件包括半导体电容器结构或电压转换器。

2、本发明在另一种例示的态样中,提出一种半导体封装结构。所述半导体封装结构包含重分布结构、soc结构、内存结构、第一电子组件及第二封胶层。所述重分布结构具有第一侧及相对于第一侧的第二侧。所述soc结构位于重分布结构的第一侧上。所述内存结构相邻于soc结构,且其位于重分布结构的第一侧上。所述第一电子组件位于重分布结构的第一侧上,且其电性连接于soc结构或内存结构中至少的一者。所述第二封胶层封胶第一电子组件、soc结构及内存结构。另外,第一电子组件包括第一半导体电容器结构或电压转换器。

3、本发明在又一种例示的态样中,提出一种半导体封装结构。所述半导体封装结构包括第一重分布结构、soc结构、内存结构、及第一电子组件。所述第一重分布结构具有第一侧及相对于第一侧的第二侧。所述soc结构位于重分布结构的第一侧上。所述内存结构相邻于soc结构,且其位于重分布结构的第一侧上。所述第一电子组件位于第一重分布结构的第二侧上,且其电性连接于内存结构。另外,第一电子组件包括主动装置。

技术特征:

1.一种半导体封装结构,包括:

2.如权利要求1所述的半导体封装结构,进一步包含一第二电子组件,其位于该第一重分布结构的该第二侧上,其中该第二电子组件包括一桥芯片电性连接于该soc结构及该内存结构。

3.如权利要求2所述的半导体封装结构,进一步包含一第二重分布结构电性耦接于该第一电子组件及该第二电子组件,其中该第二重分布结构是设置于该第一电子组件背向于该第一重分布结构的一侧。

4.如权利要求3所述的半导体封装结构,其中该第一电子组件或该第二电子组件其中至少的一者包括复数个硅通孔(tsv)电性连接于该第一重分布结构及该第二重分布结构。

5.如权利要求4所述的半导体封装结构,其中该第一封胶层包含模封底部填充胶(muf)。

6.如权利要求2所述的半导体封装结构,其中该第一封胶层侧向隔开该第一电子组件及该第二电子组件。

7.如权利要求1所述的半导体封装结构,其中该第一电子组件的一厚度是与该第二电子组件的一厚度实质相同。

8.如权利要求1所述的半导体封装结构,进一步包括一第三电子组件,其位于该第一重分布结构的该第一侧上,且其电性连接于该soc结构或该内存结构中至少的一者,其中该第三电子组件包括一半导体电容器结构或一电压转换器。

9.如权利要求1所述的半导体封装结构,其中该soc结构是垂直堆叠于该内存结构。

10.一种半导体封装结构,包括:

11.如权利要求10所述的半导体封装结构,进一步包括一第二电子组件,其位于该重分布结构的该第二侧,且其位于该soc结构及该内存结构的一投影覆盖范围下。

12.如权利要求11所述的半导体封装结构,进一步包括:

13.如权利要求10所述的半导体封装结构,其中该电压转换器包括一主动装置。

14.如权利要求10所述的半导体封装结构,其中该电压转换器包括一电源管理单元及一第二半导体电容器结构。

15.一种半导体封装结构,包括:

16.如权利要求15所述的半导体封装结构,其中该第一电子组件包括一电源管理单元及与该电源管理单元整合的一半导体电容器结构。

17.如权利要求15所述的半导体封装结构,其中该第一电子组件包括一电源管理芯片及透过一混合接合层电性连接至该电源管理芯片的一硅电容器芯片。

18.如权利要求15所述的半导体封装结构,其中该第一电子组件包括一电源管理芯片及与该电源管理芯片为堆叠的一硅电容器芯片,一硅通孔是位于该电源管理芯片及该硅电容器芯片中至少的一者。

19.如权利要求18所述的半导体封装结构,进一步包括一第二重分布结构,其支撑该第一电子组件并透过该硅通孔而电性连接于该第一重分布结构。

20.如权利要求15所述的半导体封装结构,进一步包括:

技术总结

本发明提供一种半导体封装结构。所述半导体封装结构包括第一重分布结构、SoC结构、内存结构、第一电子组件及第一封胶层。所述第一重分布结构具有第一侧及相对于第一侧的第二侧。所述SoC结构位于第一重分布结构之第一侧上。所述内存结构相邻于SoC结构,且其位于第一重分布结构的第一侧上。所述第一电子组件位于第一重分布结构的第二侧上,且其电性连接于SoC结构或内存结构中至少的一者。所述第一封胶层封胶第一电子组件。另外,第一电子组件包括半导体电容器结构或电压转换器。

技术研发人员:钟基伟,蔡茹宜

受保护的技术使用者:爱普科技股份有限公司

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!