SiCMOSFET器件及制备方法、电子设备及制备方法与流程

本发明涉及半导体器件,尤其涉及一种sic mosfet器件及制备方法、电子设备及制备方法。

背景技术:

1、sic作为一种宽禁带半导体材料,具有击穿场强高,耐高温,且开关频率高等特点,因而使用sic材料制造的sic mosfet器件非常适用于高温高压高频等工作领域,目前已广泛应用于光伏和新能源领域。

2、sic mosfet器件目前面临着一个巨大难题,由于sic/sio2界面缺陷造成的沟道迁移率下降问题,导致器件整体导通电阻较大,甚至于无法使用。在没有特殊处理的情况下,sic/sio2界面的迁移率只有10cm2/v*s,远小于sic材料本身1000cm2/v*s的迁移率。

3、对于平面mosfet,业界一般采用n2或者n2o或者no来处理sic/sio2界面,从而改善sic/sio2沟道迁移率提升到20-50cm2/v*s的水平,达到了商业化的水准,但仍有巨大改进空间。

4、对于栅极沟槽型mos,在消除jfet区域电阻的同时,并将沟道从平面晶相改成纵向晶相,改善了sic/sio2沟道迁移率,但这种sic栅极沟槽结构面临着工艺制造难度大,成本较高,且栅极沟槽底部电场集中效应引起的栅氧临界击穿问题,可靠性难以保障,因而截至目前国内外实现量产的难度仍然较高。

5、因而,研发一种新的sic mosfet器件,以改善sic/sio2沟道迁移率,成为本领域技术人员亟待要解决的技术重点。

技术实现思路

1、本发明提供一种sic mosfet器件及制备方法、电子设备及制备方法,以解决如何降低或消除sic mosfet器件的沟道界面缺陷,同时避免了栅极漏电的问题。

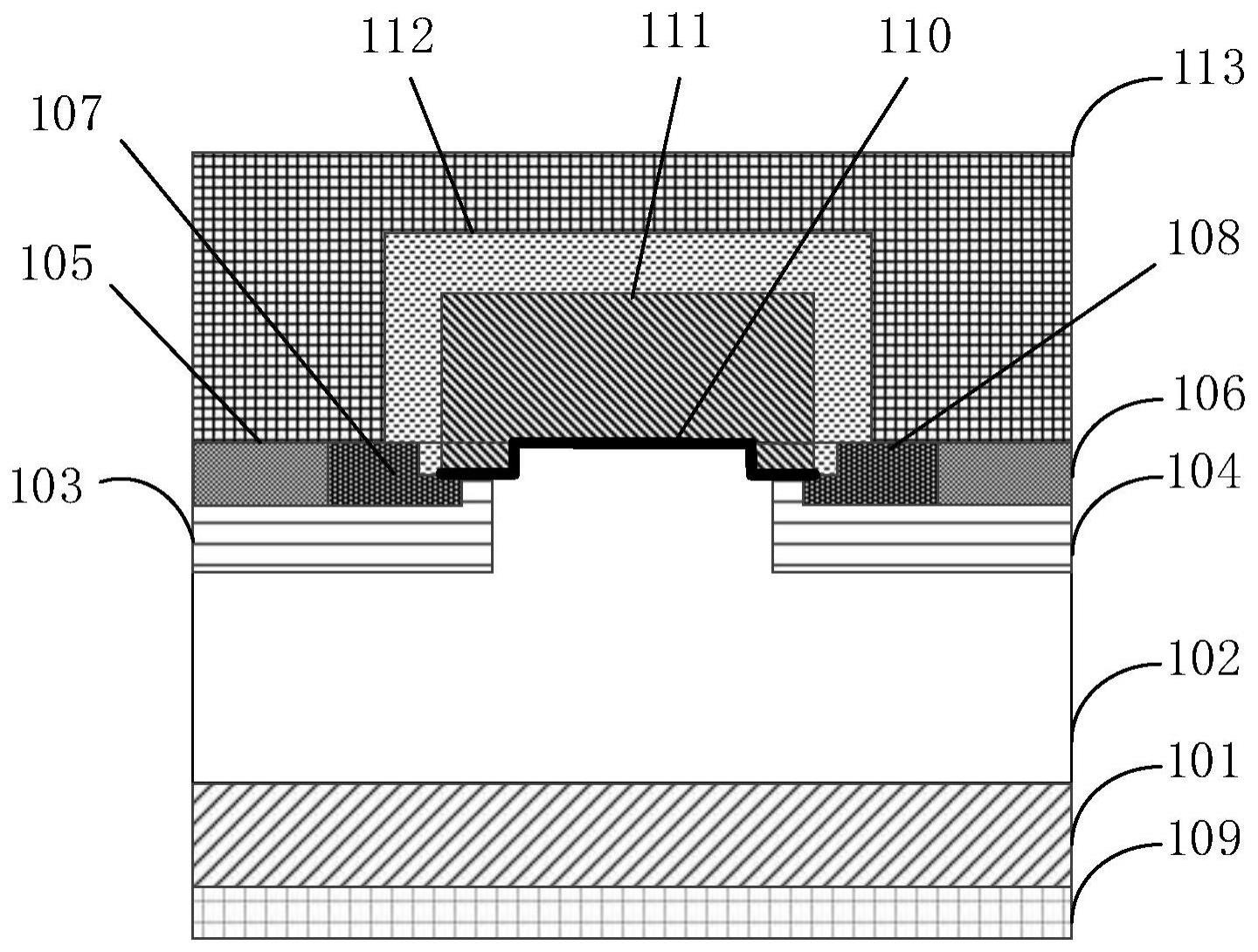

2、根据本发明的第一方面,提供了一种sic mosfet器件,包括:

3、衬底,以及形成于所述衬底上的外延层;所述衬底的材料是sic,所述外延层的材料是sic;

4、第一p阱屏蔽区与第二p阱屏蔽区,形成于所述外延层的表层,且沿第一方向间隔排列;其中,所述第一方向垂直于所述衬底与所述外延层的堆叠方向;

5、第一p+源极注入区与第一n+源极注入区,形成于所述第一p阱屏蔽区的表层;且沿所述第一方向依次排列;

6、第二n+源极注入区与第二p+源极注入区,形成于所述第二p阱屏蔽区的表层;且沿所述第一方向依次排列;其中,所述p阱屏蔽区包裹对应的n+源极注入区与p+源极注入区;

7、栅极多晶硅层,覆盖部分所述外延层,并伸入到所述p阱屏蔽区的表层至所述第一深度;同时还伸入到部分所述外延层的表层与部分所述n+源极注入区的表层至所述第一深度;其中,所述第一深度小于所述n+源极注入区沿第二方向的厚度;其中,所述第二方向垂直于所述第一方向;

8、栅介质层;覆盖所述部分n+源极注入区,还伸入到所述部分所述n+源极注入区的表层至所述第一深度,同时包裹所述栅极多晶硅层;

9、栅极氧化层,形成于所述p阱屏蔽区、所述外延层、部分所述n+源极注入区与所述栅极多晶硅层之间。

10、可选的,所述sic mosfet器件还包括:源极金属层与漏极金属层;

11、其中,所述源极金属层覆盖所述p+源极注入区与暴露出来的所述n+源极注入区,且包裹所述栅介质层;

12、所述漏极金属层形成于所述衬底的第一表面;其中,所述衬底的第一表面表征了所述衬底的背离所述外延层的一面。

13、可选的,所述第一深度为:60nm-120nm。

14、根据本发明的第二方面,提供了一种sic mosfet器件的制备方法,用于制备本发明第一方面的任一项所述的sic mosfet器件,包括:

15、提供一所述衬底,并在所述衬底上形成所述外延层;

16、形成所述第一p阱屏蔽区、所述第二p阱屏蔽区、所述第一p+源极注入区、所述第一n+源极注入区、所述第二n+源极注入区以及所述第二p+源极注入区;其中,所述第一p阱屏蔽区与所述第二p阱屏蔽区形成于所述外延层的表层,且沿所述第一方向间隔排列;所述第一p+源极注入区与所述第一n+源极注入区,形成于所述第一p阱屏蔽区的表层,且沿所述第一方向依次排列;所述第二n+源极注入区与所述第二p+源极注入区形成于所述第二p阱屏蔽区的表层,且沿所述第一方向依次排列;其中,所述p阱屏蔽区包裹对应的所述n+源极注入区与所述p+源极注入区;

17、刻蚀所述p阱屏蔽区、紧贴所述p阱屏蔽区的沿所述第一方向的两侧壁的部分所述n+源极注入区与所述部分外延层至所述第一深度,以形成第一空腔;其中,所述第一深度小于所述n+源极注入区沿所述第二方向的厚度;

18、形成所述栅极多晶硅层与所述栅极氧化层;其中,所述栅极多晶硅层覆盖部分所述外延层,并填充到部分所述第一空腔中,且覆盖所述第一空腔底部的所述外延层、所述p阱屏蔽区以及部分所述n+源极注入区的表面;所述栅极氧化层形成于所述p阱屏蔽区、部分所述n+源极注入区、所述外延层与所述栅极多晶硅层之间;

19、形成所述栅介质层;所述栅介质层覆盖所述部分n+源极注入区的表面,且填充于所述第一空腔的剩余部分,以覆盖所述第一空腔中暴露出来的所述n+源极注入区的表面,同时包裹所述栅极多晶硅层。

20、可选的,所述第一空腔的深度为:60nm-120nm。

21、可选的,所述sic mosfet器件的制备方法还包括:形成所述源极金属层与所述漏极金属层。

22、根据本发明的第三方面,提供了一种电子设备,包括本发明第一方面的任一项所述的sic mosfet器件。

23、根据本发明的第四方面,提供了一种电子设备的制备方法,用于制备本发明第三方面所述的电子设备。

24、本发明提供的sic mosfet器件,通过刻蚀方式在刻蚀所述p阱屏蔽区、部分所述n+源极注入区以及所述部分外延层表层形成空腔,以使得sic mosfet器件制备为:栅极多晶硅层,覆盖部分所述外延层,并伸入到所述p阱屏蔽区的表层至所述第一深度;同时还伸入到部分所述外延层的表层与部分所述n+源极注入区的表层至所述第一深度。栅介质层;覆盖所述部分n+源极注入区,还伸入到所述部分所述n+源极注入区的表层至所述第一深度,同时包裹所述栅极多晶硅层。由于,通过刻蚀方式消除了p阱屏蔽区的表面在制造工艺中引入界面缺陷,从而提升了沟道迁移率以及器件性能。从而能够有效降低mosfet沟道界面缺陷,提升沟道迁移率,以降低器件导通电阻,使设计的sic mosfet器件具有较低比导通电阻,较高栅极可靠性。另外,由于在进行离子注入和高温退火过程中,在n+源极注入区表面也产生了晶格失配或者缺陷,因而,如果栅极氧化层直接覆盖到n+源极注入区上,在施加栅极电压时,会造成缺陷位置电荷急剧增加,从而引起漏电现象。因而,栅极氧化层形成于所述p阱屏蔽区、所述外延层、部分所述n+源极注入区与所述栅极多晶硅层之间,避免了栅极漏电现象。

技术特征:

1.一种sic mosfet器件,其特征在于,包括:

2.根据权利要求1所述的sic mosfet器件,其特征在于,所述sic mosfet器件还包括:源极金属层与漏极金属层;

3.根据权利要求2所述的sic mosfet器件,其特征在于,所述第一深度为:60nm-120nm。

4.一种sic mosfet器件的制备方法,用于制备权利要求1-3任一项所述的sic mosfet器件,其特征在于,包括:

5.根据权利要求4所述的sic mosfet器件的制备方法,其特征在于,所述第一空腔的深度为:60nm-120nm。

6.根据权利要求5所述的sic mosfet器件的制备方法,其特征在于,所述sic mosfet器件的制备方法还包括:

7.一种电子设备,其特征在于,包括权利要求1-3任一项所述的sic mosfet器件。

8.一种电子设备的制备方法,其特征在于,用于制备权利要求7所述的电子设备。

技术总结

本发明提供了一种SiC MOSFET器件,包括:衬底、形成于衬底上的外延层;第一P阱屏蔽区与第二P阱屏蔽区,形成于外延层的表层,第一P+源极注入区、第一N+源极注入区、第二N+源极注入区、第二P+源极注入区,形成于第二P阱屏蔽区的表层;栅极多晶硅层,覆盖部分外延层,并伸入到P阱屏蔽区的表层至第一深度;并伸入到部分外延层的表层与部分N+源极注入区的表层至第一深度;第一深度小于N+源极注入区沿第二方向的厚度;栅介质层;覆盖部分N+源极注入区,还伸入到部分N+源极注入区的表层至第一深度,同时包裹栅极多晶硅层;栅极氧化层,形成于P阱屏蔽区、外延层、部分N+源极注入区与栅极多晶硅层之间。该方案解决了如何降低SiC MOSFET器件的沟道界面缺陷的问题。

技术研发人员:庞亚楠,陈敏,欧新华,袁琼,戴维

受保护的技术使用者:上海芯导电子科技股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!