半导体结构及其形成方法与流程

本发明的实施例涉及半导体结构及其形成方法。

背景技术:

1、半导体图像传感器用于感测光或辐射波。互补金属氧化物半导体(cmos)图像传感器(cis)广泛用于各种应用,诸如数码相机或移动电话相机。cis包括像素的阵列。每个像素包括将入射光转换成电信号的光电二极管。

2、背照式(bsi)图像传感器是cis,其中光从半导体晶圆的背侧而不是从前侧进入。因为在cmos工艺中,bsi cmos图像传感器的背侧相对不受形成在半导体晶圆的前侧上的介电层和/或金属层的阻碍,所以提高了cmos图像传感器的整体灵敏度。

技术实现思路

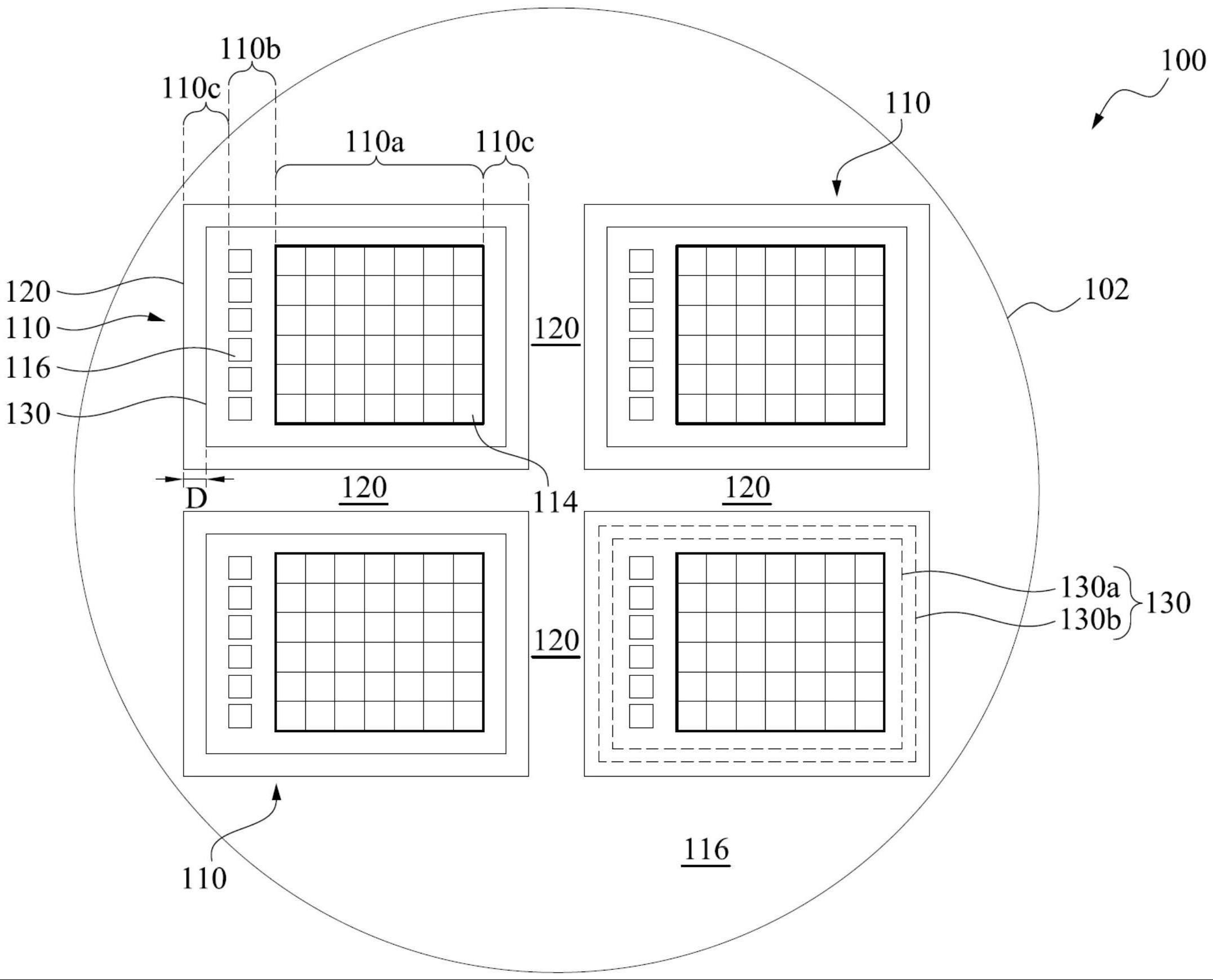

1、本发明的实施例提供了一种半导体结构,包括:传感器晶圆,包括位于衬底上和所述衬底内的多个传感器芯片,其中,所述多个传感器芯片中的每个包括:像素阵列区域,接合焊盘区域,和外围区域,其中,所述外围区域邻近划线,并且所述划线位于所述多个传感器芯片的相邻的传感器芯片之间;以及应力释放沟槽结构,嵌入所述衬底中,其中,所述应力释放沟槽结构位于所述外围区域中,并且所述应力释放沟槽结构完全围绕所述多个传感器芯片的相应传感器芯片的所述像素阵列区域和所述接合焊盘区域的外周。

2、本发明的另一实施例提供了一种半导体结构,包括:传感器晶圆,包括:第一半导体衬底;多个光敏元件,位于所述第一半导体衬底的像素阵列区域中,其中,所述多个光敏元件位于所述第一半导体衬底的前侧内;第一互连结构,位于所述第一半导体衬底的所述前侧上;以及应力释放沟槽结构,位于所述第一半导体衬底的外围区域中,所述应力释放沟槽结构围绕所述像素阵列区域和接合焊盘区域,其中,所述应力释放沟槽结构位于从所述第一半导体衬底的背侧延伸穿过所述第一半导体衬底的沟槽内,并且所述第一半导体衬底的所述背侧与所述第一半导体衬底的所述前侧相对;以及器件晶圆,接合到所述传感器晶圆,其中,所述器件晶圆包括有源器件。

3、本发明的又一实施例提供了一种形成半导体结构的方法,包括:将第一晶圆接合到第二晶圆,所述第一晶圆包括:半导体衬底;多个光敏元件,位于所述半导体衬底的像素阵列区域中,其中,所述多个光敏元件在所述半导体衬底的前侧处嵌入在所述半导体衬底中;多个浅沟槽隔离(sti)结构,在所述半导体衬底的所述前侧处嵌入在所述半导体衬底中;互连结构,位于所述半导体衬底的所述前侧上方;形成从所述半导体衬底的背侧延伸穿过所述半导体衬底的多个焊盘开口,其中,所述多个焊盘开口暴露所述半导体衬底的接合焊盘区域中的所述多个浅沟槽隔离结构的第一浅沟槽隔离结构;形成从所述背侧延伸穿过所述半导体衬底的沟槽,其中,所述沟槽暴露所述半导体衬底的外围区域中的所述多个浅沟槽隔离结构的第二浅沟槽隔离结构,其中,所述沟槽完全围绕所述像素阵列区域和所述接合焊盘区域;以及沿着所述多个焊盘开口和所述沟槽的侧壁和底面以及在所述半导体衬底的背侧表面上方沉积钝化层。

技术特征:

1.一种半导体结构,包括:

2.根据权利要求1所述的半导体结构,其中,所述应力释放沟槽结构包括单个连续结构,所述单个连续结构完全围绕所述像素阵列区域和所述接合焊盘区域。

3.根据权利要求1所述的半导体结构,其中,所述应力释放沟槽结构包括多个非连续段,所述多个非连续段一起完全围绕所述像素阵列区域和所述接合焊盘区域。

4.根据权利要求3所述的半导体结构,其中,所述多个非连续段中的第一组非连续段在所述像素阵列区域和所述接合焊盘区域周围延伸,并且所述多个非连续段中的第二组非连续段在所述第一组非连续段周围延伸。

5.根据权利要求4所述的半导体结构,其中,所述第一组非连续段中的非连续段相对于所述第二组非连续段中的非连续段交错。

6.根据权利要求1所述的半导体结构,其中,所述应力释放沟槽结构与所述多个传感器芯片中的相应传感器芯片的边缘间隔小于100μm的距离,

7.根据权利要求1所述的半导体结构,其中,所述应力释放沟槽结构邻接所述多个传感器芯片中的相应传感器芯片的边缘。

8.根据权利要求1所述的半导体结构,其中,所述应力释放沟槽结构包括与所述衬底的半导体材料不同的材料。

9.一种半导体结构,包括:

10.一种形成半导体结构的方法,包括:

技术总结

半导体结构包括传感器晶圆,该传感器晶圆包括位于衬底上和衬底内的多个传感器芯片。多个传感器芯片中的每个包括像素阵列区域、接合焊盘区域和外围区域。相邻的外围区域之间设置划线,并且划线位于多个传感器芯片的相邻的传感器芯片之间。多个传感器芯片中的每个还包括嵌入衬底中的应力释放沟槽结构,其中应力释放沟槽结构位于外围区域中,并且应力释放沟槽结构完全围绕多个传感器芯片的相应传感器芯片的像素阵列区域和接合焊盘区域的外周。本发明的实施例涉及半导体结构的形成方法。

技术研发人员:郑允玮,周俊豪,李国政,陈英豪,贾钧伟

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!