一种SiC-JFET器件及其制备方法与流程

本申请涉及半导体器件,具体地,涉及一种sic-jfet器件及其制备方法。

背景技术:

1、结型场效应晶体管(junction field-effect transistor,jfet)是一种使用栅极电压来控制器件开启关断的器件。器件的栅极电压施加到pn结的一侧,引起导电沟道中耗尽区的改变,从而控制开启和关断。sic材料具有宽禁带、高电子饱和漂移速度、高耐压、耐高温等优异特性,非常适合于制备大功率器件和高速开关元件。

2、jfet设计的两个重点是提升栅极性能及器件耐压。要获得更好的栅极性能,沟道的长度应当更短,沟道的宽度应当更宽。对于多子为电子的器件来说,沟道n型掺杂浓度应当足够高。但对于需求特定耐压的器件来说,增加沟道n型掺杂浓度会减小其与相邻p型掺杂区域的pn结的耐压,缩短沟道长度受到光刻精度的限制,加宽沟道的厚度会使得需要较大的反向栅极电压来关断器件沟道,限制了器件损耗的降低以及功率的提升。

技术实现思路

1、为了解决上述技术缺陷之一,本申请实施例中提供了一种sic-jfet器件及其制备方法。

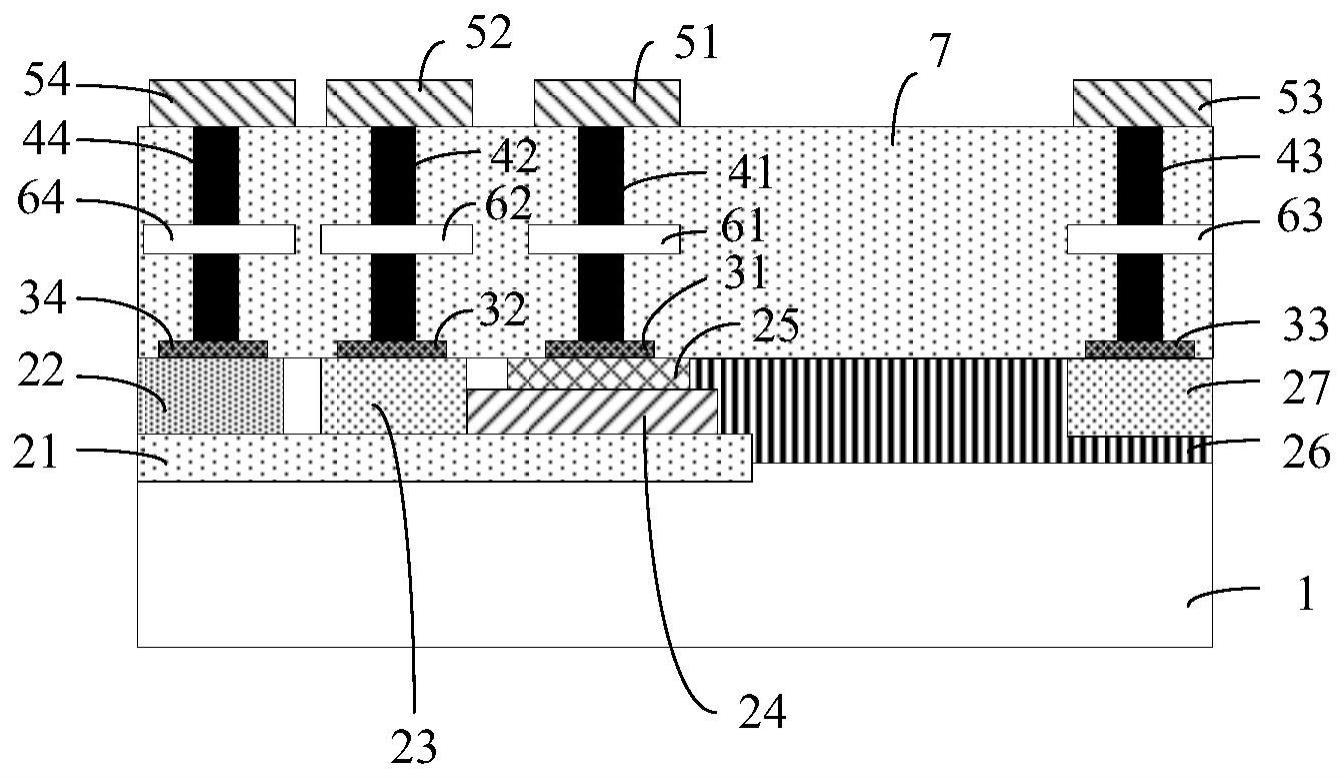

2、根据本申请实施例的第一个方面,提供了一种sic-jfet器件,包括:

3、基底;

4、位于基底上部区域内的第二栅极注入层;

5、位于基底上部区域内且在第二栅极注入层之上并排布设的源极注入层及沟道层;

6、位于基底上部区域内且位于沟道层之上的第一栅极注入层;

7、位于第一栅极注入层之上的第一栅极接触金属层;

8、位于基底之上的绝缘层;

9、位于绝缘层内且位于第一栅极接触金属层之上的第一栅极接触孔;

10、位于第一栅极接触孔之上的第一栅极金属层。

11、根据本申请实施例的第二个方面,提供了一种sic-jfet器件的制备方法,包括:

12、在基底上部区域内形成第一栅极注入层;

13、在基底上部区域内且在第一栅极注入层之上形成并排布设的源极注入层及沟道层;

14、在基底上部区域内且在沟道层之上形成第二栅极注入层;

15、在第二栅极注入层之上形成第一栅极接触金属层;

16、在第一栅极接触金属层之上生长绝缘层;

17、在绝缘层内打孔形成第一栅极接触孔;

18、在第一栅极接触孔之上形成第一栅极金属层。

19、本申请实施例所提供的技术方案,在基底的上部区域形成有第二栅极注入层,并在第二栅极注入层之上并排布设的源极注入层及沟道层;在沟道层之上形成有第一栅极注入层;第一栅极注入层之上依次设置第一栅极接触金属层、形成在绝缘层内的第一栅极接触孔及第一栅极金属层构成栅极,第一栅极注入层和第二栅极注入层分别位于沟道层的上方和下方,分别从上下两个方向对沟道层进行夹断,从而能增大沟道层的厚度,实现在低栅压下有足够低的导通电阻,从而形成足够高的饱和电流,有利于提高栅极性能及器件的耐压性能。

技术特征:

1.一种sic-jfet器件,其特征在于,包括:

2.根据权利要求1所述的sic-jfet器件,其特征在于,还包括:

3.根据权利要求1或2所述的sic-jfet器件,其特征在于,还包括:

4.根据权利要求1所述的sic-jfet器件,其特征在于,还包括:

5.根据权利要求3所述的sic-jfet器件,其特征在于,还包括:

6.根据权利要求1所述的sic-jfet器件,其特征在于,所述基底为高阻sic衬底。

7.根据权利要求1所述的sic-jfet器件,其特征在于,所述基底包括:

8.一种如权利要求1-7任一项所述sic-jfet器件的制备方法,其特征在于,包括:

9.根据权利要求8所述的方法,其特征在于,在形成第一栅极注入层之后,还包括:

10.根据权利要求8或9所述的方法,其特征在于,在形成第一栅极注入层之后,还包括:

11.根据权利要求8所述的方法,其特征在于,在形成绝缘层之后,还包括:

12.根据权利要求8所述的方法,其特征在于,所述基底为高阻sic衬底。

13.根据权利要求8所述的方法,其特征在于,所述基底包括衬底、第一外延层和第二外延层;其中,衬底为n型衬底或高阻sic衬底;

技术总结

本申请实施例提供一种SiC‑JFET器件及其制备方法,其中,SiC‑JFET器件包括:基底;位于基底上部区域内的第二栅极注入层;位于基底上部区域内且在第二栅极注入层之上并排布设的源极注入层及沟道层;位于基底上部区域内且位于沟道层之上的第一栅极注入层;位于第一栅极注入层之上的第一栅极接触金属层;位于基底之上的绝缘层;位于绝缘层内且位于第一栅极接触金属层之上的第一栅极接触孔;位于第一栅极接触孔之上的第一栅极金属层。本申请实施例提供的SiC‑JFET器件及其制备方法,采用第一栅极注入层和第二栅极注入层分别位于沟道层的上方和下方,分别从上下两个方向对沟道层进行夹断,从而能增大沟道层的厚度,从而提升器件的性能。

技术研发人员:蒋天浩,岳丹诚

受保护的技术使用者:苏州华太电子技术股份有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!