半导体可控整流器及其形成方法与流程

本发明涉及半导体可控整流器(scr),更具体地涉及形成在多晶半导体材料阱中的scr及其形成方法。

背景技术:

1、由静电放电(esd)导致的故障可能会对集成电路(ic)的可靠性产生负面影响。ic设计通常包括esd保护器件(例如,在输入/输出衬垫(pad)处、在电源衬垫处、以及在电源域之间)。半导体可控整流器(scr)(例如,硅可控整流器)是一种类型的esd器件。在射频(rf)电路中,半导体可控整流器的存在可能会由于电容负载和随之而来的对谐波的影响而妨碍rf电路性能。过去减轻这些影响的努力包括,例如,用于scr自保护的开关。然而,这种保护开关的存在也减少了通过scr提供的esd保护量。

技术实现思路

1、本文提及的所有方面、示例和特征可以以任何技术上可能的方式组合。

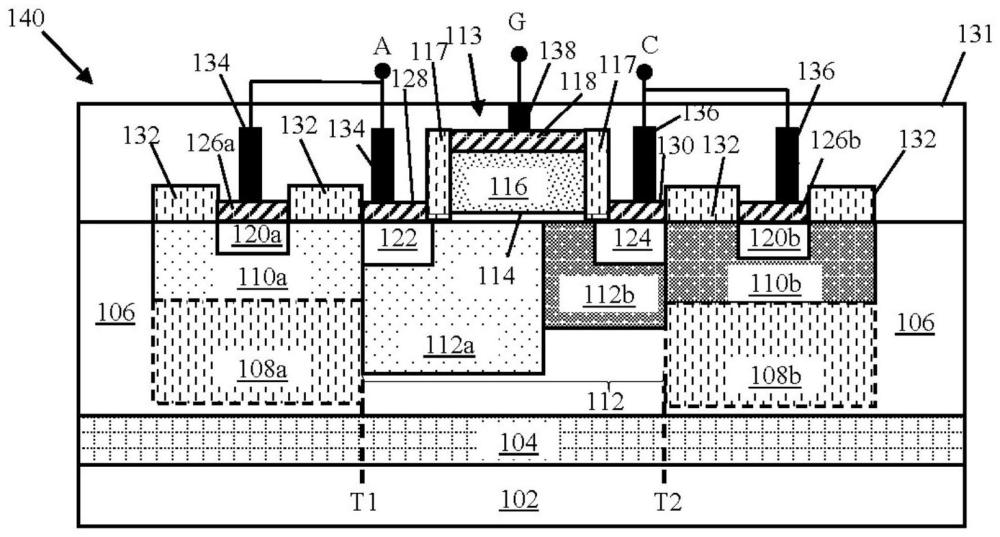

2、本文公开的结构的实施例提供了一种结构,其包括:第一多晶半导体材料,其位于第一绝缘体上,并且在其中包括第一阱;单晶半导体材料,其与所述第一多晶半导体材料相邻,并且在其中包括阳极区域和阴极区域;以及第二多晶半导体材料,其位于第二绝缘体上,并且在其中包括第二阱。

3、本公开的另一方面包括前述方面中的任何方面,并且其中,所述单晶半导体材料包括具有第一掺杂类型的第一区域和具有与所述第一掺杂类型相反的第二掺杂类型的第二区域,其中所述阳极区域位于所述第一区域内,并且所述阴极区域位于所述第二区域内。

4、本公开的另一方面包括前述方面中的任何方面,并且还包括:栅极结构,其位于所述阳极区域和所述阴极区域之间的所述单晶半导体材料上,且位于所述单晶半导体材料的所述第一区域和所述第二区域之间的边界上方。

5、本公开的另一方面包括前述方面中的任何方面,并且还包括:第一上覆(overlying)绝缘体,其位于所述第一阱和所述阳极区域之间的所述第一多晶半导体材料上;以及第二上覆绝缘体,其位于所述第二阱和所述阴极区域之间的所述第二多晶半导体材料上。

6、本公开的另一方面包括前述方面中的任何方面,并且还包括:电阻半导体材料,其位于所述第一绝缘体、所述单晶半导体材料和所述第二绝缘体下方。

7、本公开的另一方面包括前述方面中的任何方面,并且其中,所述单晶半导体材料包括与所述第一多晶半导体材料和所述第一绝缘体相邻的第一侧壁,以及与所述第二多晶半导体材料和所述第二绝缘体相邻的第二侧壁。

8、本公开的另一方面包括前述方面中的任何方面,并且其中,所述单晶半导体材料位于三阱半导体结构内。

9、本文公开的结构的一些实施例提供了一种结构,其包括:n型多晶半导体材料,其位于第一绝缘体上;第一n+区域,其位于所述n型多晶半导体材料内;单晶半导体材料,其位于衬底上并与所述n型多晶半导体材料相邻,所述单晶半导体材料包括与p型区域相邻的n型区域;p型多晶半导体材料,其位于第二绝缘体上;第一p+区域,其位于所述p型多晶半导体材料内;第二p+区域,其位于所述单晶半导体材料的所述n型区域内;以及第二n+区域,其位于所述单晶半导体材料的所述p型区域内。

10、本公开的另一方面包括前述方面中的任何方面,并且还包括:栅极结构,其位于所述第二p+区域和所述第二n+区域之间的所述单晶半导体材料上,且位于所述单晶半导体材料的所述n型区域和所述p型区域之间的边界上方。

11、本公开的另一方面包括前述方面中的任何方面,并且还包括:第一上覆绝缘体,其位于所述第一n+区域和所述第二p+区域之间的所述n型多晶半导体材料上;以及第二上覆绝缘体,其位于所述第一p+区域和所述第二n+区域之间的所述p型多晶半导体材料上。

12、本公开的另一方面包括前述方面中的任何方面,并且还包括:电阻半导体材料,其位于所述第一绝缘体、所述单晶半导体材料和所述第二绝缘体下方。

13、本公开的另一方面包括前述方面中的任何方面,并且其中,所述单晶半导体材料包括与所述n型多晶半导体材料和所述第一绝缘体相邻的第一侧壁,以及与所述p型多晶半导体材料和所述第二绝缘体相邻的第二侧壁。

14、本公开的另一方面包括前述方面中的任何方面,并且其中,所述单晶半导体材料位于三阱半导体结构内。

15、本文公开的结构的另外的实施例提供了一种方法,其包括:在第一绝缘体上形成第一多晶半导体材料;在所述第一多晶半导体材料内形成第一阱;形成与所述第一多晶半导体材料相邻的单晶半导体材料;在所述单晶半导体材料内形成阳极区域和阴极区域;在第二绝缘体上形成第二多晶半导体材料;以及在所述第二多晶半导体材料内形成第二阱。

16、本公开的另一方面包括前述方面中的任何方面,并且其中,形成所述单晶半导体材料包括:形成与所述第一多晶半导体材料相邻的具有第一掺杂类型的第一区域;以及形成与所述第二多晶半导体材料相邻的具有与所述第一掺杂类型相反的第二掺杂类型的第二区域,其中,所述阳极区域位于所述第一区域内,并且所述阴极区域位于所述第二区域内。

17、本公开的另一方面包括前述方面中的任何方面,并且还包括:形成栅极结构,所述栅极结构位于所述阳极区域和所述阴极区域之间的所述单晶半导体材料上且位于所述单晶半导体材料的所述第一区域和所述第二区域之间的边界上方。

18、本公开的另一方面包括前述方面中的任何方面,并且还包括:在所述第一阱和所述阳极区域之间的所述第一多晶半导体材料上形成第一上覆绝缘体;以及在所述第二阱和所述阴极区域之间的所述第二多晶半导体材料上形成第二上覆绝缘体。

19、本公开的另一方面包括前述方面中的任何方面,并且其中,形成所述单晶半导体材料包括在电阻半导体材料上方形成所述单晶半导体材料,其中,所述电阻半导体材料位于所述第一绝缘体和所述第二绝缘体下方。

20、本公开的另一方面包括前述方面中的任何方面,并且其中,所述单晶半导体材料包括与所述第一多晶半导体材料和所述第一绝缘体相邻的第一侧壁,以及与所述第二多晶半导体材料和所述第二绝缘体相邻的第二侧壁。

21、本公开的另一方面包括前述方面中的任何方面,并且其中,形成所述单晶半导体材料包括在三阱半导体结构内形成掺杂半导体。

技术特征:

1.一种结构,包括:

2.根据权利要求1所述的结构,其中,所述单晶半导体材料包括具有第一掺杂类型的第一区域和具有与所述第一掺杂类型相反的第二掺杂类型的第二区域,其中所述阳极区域位于所述第一区域内,并且所述阴极区域位于所述第二区域内。

3.根据权利要求2所述的结构,还包括:栅极结构,其位于所述阳极区域和所述阴极区域之间的所述单晶半导体材料上,且位于所述单晶半导体材料的所述第一区域和所述第二区域之间的边界上方。

4.根据权利要求3所述的结构,还包括:

5.根据权利要求1所述的结构,还包括:电阻半导体材料,其位于所述第一绝缘体、所述单晶半导体材料和所述第二绝缘体下方。

6.根据权利要求1所述的结构,其中,所述单晶半导体材料包括与所述第一多晶半导体材料和所述第一绝缘体相邻的第一侧壁,以及与所述第二多晶半导体材料和所述第二绝缘体相邻的第二侧壁。

7.根据权利要求1所述的结构,其中,所述单晶半导体材料位于三阱半导体结构内。

8.一种结构,包括:

9.根据权利要求8所述的结构,还包括:栅极结构,其位于所述第二p+区域和所述第二n+区域之间的所述单晶半导体材料上,且位于所述单晶半导体材料的所述n型区域和所述p型区域之间的边界上方。

10.根据权利要求8所述的结构,还包括:

11.根据权利要求8所述的结构,还包括:电阻半导体材料,其位于所述第一绝缘体、所述单晶半导体材料和所述第二绝缘体下方。

12.根据权利要求8所述的结构,其中,所述单晶半导体材料包括与所述n型多晶半导体材料和所述第一绝缘体相邻的第一侧壁,以及与所述p型多晶半导体材料和所述第二绝缘体相邻的第二侧壁。

13.根据权利要求8所述的结构,其中,所述单晶半导体材料位于三阱半导体结构内。

14.一种方法,包括:

15.根据权利要求14所述的方法,其中,形成所述单晶半导体材料包括:

16.根据权利要求15所述的方法,还包括:形成栅极结构,所述栅极结构位于所述阳极区域和所述阴极区域之间的所述单晶半导体材料上且位于所述单晶半导体材料的所述第一区域和所述第二区域之间的边界上方。

17.根据权利要求16所述的方法,还包括:

18.根据权利要求14所述的方法,其中,形成所述单晶半导体材料包括在电阻半导体材料上方形成所述单晶半导体材料,其中,所述电阻半导体材料位于所述第一绝缘体和所述第二绝缘体下方。

19.根据权利要求14所述的方法,其中,所述单晶半导体材料包括与所述第一多晶半导体材料和所述第一绝缘体相邻的第一侧壁,以及与所述第二多晶半导体材料和所述第二绝缘体相邻的第二侧壁。

20.根据权利要求14所述的方法,其中,形成所述单晶半导体材料包括在三阱半导体结构内形成掺杂半导体。

技术总结

本公开的实施例提供了半导体可控整流器(SCR)结构及其形成方法。SCR结构可以包括位于第一绝缘体上并且在其中包括第一阱的第一多晶半导体材料。单晶半导体材料与第一多晶半导体材料相邻并且在其中包括阳极区域和阴极区域。第二多晶半导体材料位于第二绝缘体上并且在其中包括第二阱。

技术研发人员:A·纳特,A·F·卢瓦索,R·J·小戈捷,S·米特拉

受保护的技术使用者:格芯(美国)集成电路科技有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!