一种功率器件的漏源极漏电流的软失效分析方法与流程

本发明涉及半导体制造,特别涉及一种功率器件的漏源极漏电流的软失效分析方法。

背景技术:

1、当前,对芯片级功率器件的失效分析通常包括两种方法,其一为芯片正面分析方法:先去层(即剥离芯片正面的钝化层和正面金属层),再从芯片正面进行失效定位,最后再进行pfa分析(即物理失效分析)。在该方法中,在去层时很容易破坏芯片的钝化层和场限环结构,从而导致失效模式(fail mode)改变。其二为芯片背面分析方法:先对芯片进行封装,再从芯片的背面开封,再从芯片背面去除层(即剥离背面金属层),再从芯片背面进行失效定位,最后再进行pfa分析。在该方法中,芯片封装增加了成本,且封装所需周期较长,加长了分析所花费的时间;同时,在芯片封装时的高温处理过程使得芯片的失效参数可能恢复正常,从而导致失效模式改变。

技术实现思路

1、本发明的目的在于,提供一种功率器件的漏源极漏电流的软失效分析方法,可以不改变失效模式以提高分析成功率,还可以提高时效性并控制成本。

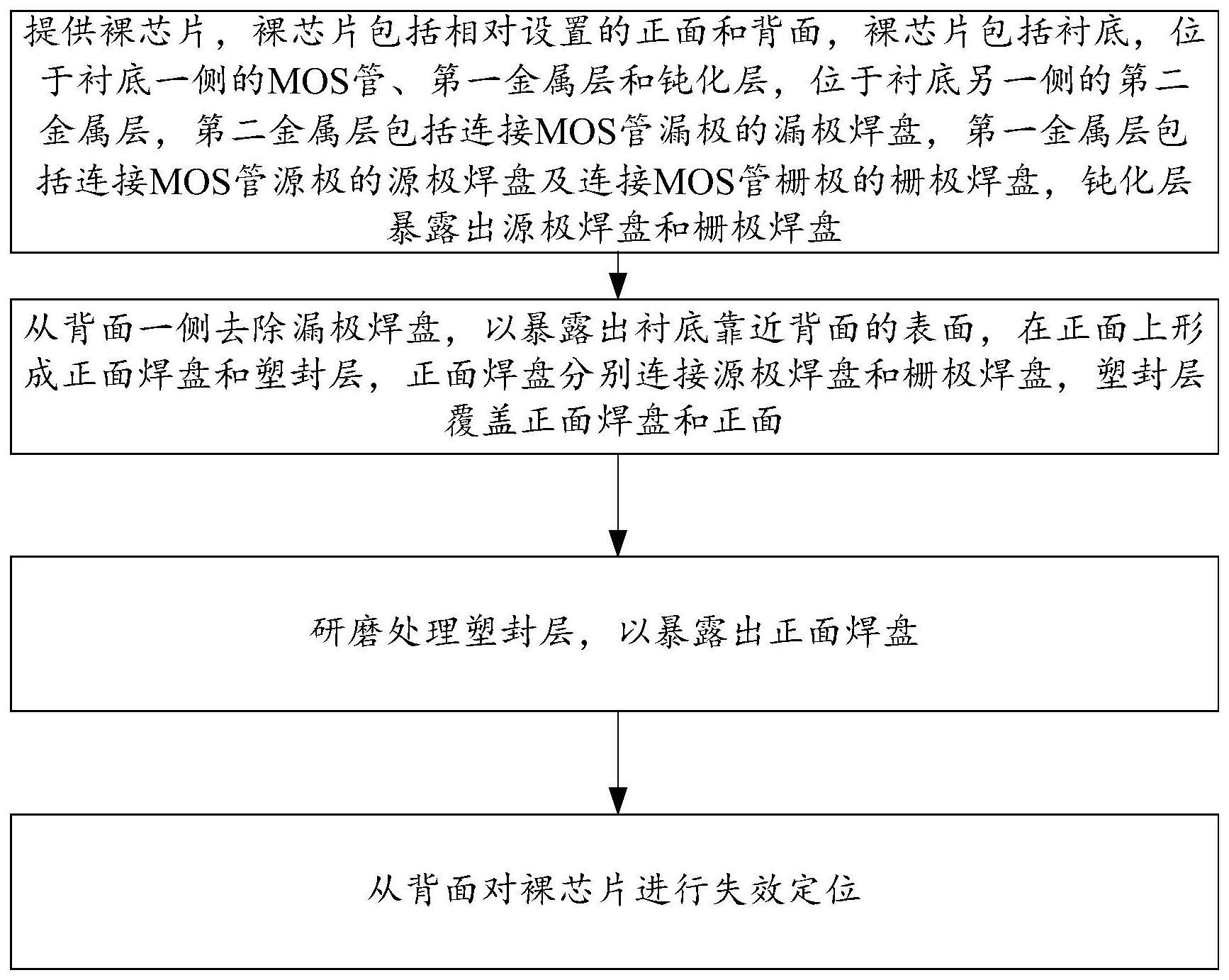

2、为了解决上述问题,本发明提供一种功率器件的漏源极漏电流的软失效分析方法,包括以下步骤:

3、提供裸芯片,所述裸芯片包括相对设置的正面和背面,包括衬底,位于衬底一侧的mos管、第一金属层和钝化层,位于衬底另一侧的第二金属层,所述第二金属层包括连接mos管(mosfet)漏极的漏极焊盘,所述第一金属层包括连接mos管源极的源极焊盘及连接mos管栅极的栅极焊盘,所述钝化层暴露出所述源极焊盘和栅极焊盘;

4、从所述背面一侧去除所述漏极焊盘,以暴露出所述衬底靠近所述背面的表面,在所述正面上形成正面焊盘和塑封层,所述正面焊盘分别连接所述源极焊盘和栅极焊盘,所述正面焊盘外侧围设有所述塑封层;

5、从所述背面对所述裸芯片进行失效定位。

6、可选的,所述正面包括第一部分和第二部分,所述第二部分围设在所述第一部分外侧;所述第一部分具有所述栅极焊盘以及所述栅极焊盘附近的钝化层和部分所述源极焊盘,且所述正面焊盘覆盖所述第一部分。

7、进一步的,去除所述漏极焊盘以及形成正面焊盘和塑封层的具体步骤为:

8、从所述背面研磨去除所述漏极焊盘,以暴露出所述漏极;

9、利用塑封胶在所述正面形成塑封层,所述塑封层覆盖所述第二部分;

10、将焊料焊接在所述第一部分上,以形成正面焊盘,所述正面焊盘将所述源极焊盘和栅极焊盘短路。

11、可选的,所述正面焊盘上也覆盖有塑封层。

12、进一步的,在步骤从所述背面对所述裸芯片进行失效定位之前,研磨处理正面焊盘上的塑封层,以暴露出所述正面焊盘。

13、进一步的,去除所述漏极焊盘以及形成正面焊盘和塑封层的具体步骤为:

14、将焊料焊接在所述第一部分上形成正面焊盘,所述正面焊盘将所述源极焊盘和栅极焊盘短路;

15、利用塑封胶在所述正面形成塑封层,所述塑封层覆盖所述正面焊盘和所述第二部分;

16、从所述背面研磨去除所述漏极焊盘,以暴露出所述漏极。

17、进一步的,去除所述漏极焊盘以及形成正面焊盘和塑封层的具体步骤为:

18、从所述背面研磨去除所述漏极焊盘,以暴露出所述漏极;

19、将焊料焊接在所述第一部分上形成正面焊盘,所述正面焊盘将所述源极焊盘和栅极焊盘短路;

20、利用塑封胶在所述正面形成塑封层,所述塑封层覆盖所述正面焊盘和所述第二部分。

21、进一步的,所述焊料采用熔点低于70℃的固态金属。

22、进一步的,所述焊料采用伍德合金。

23、进一步的,所述塑封层采用固化温度小于70℃的塑封胶。

24、进一步的,所述塑封层采用ab胶。

25、进一步的,对所述裸芯片进行失效定位的方法为:

26、从所述背面扎针以给所述漏极提供高电位,给所述正面焊盘提供低电位,以实现对所述裸芯片的失效位置进行定位;

27、利用fib或tem对所述失效位置进行结构分析。

28、与现有技术相比,本发明具有以下有益效果:

29、本发明提供的一种功率器件的漏源极漏电流的软失效分析方法,包括提供裸芯片,所述裸芯片包括相对设置的正面和背面,所述裸芯片包括衬底,位于所述衬底一侧的mos管、第一金属层和钝化层,位于所述衬底另一侧的第二金属层,所述第二金属层包括连接mos管(mosfet)漏极的漏极焊盘,所述第一金属层包括连接mos管源极的源极焊盘及连接mos管栅极的栅极焊盘,所述钝化层暴露出所述源极焊盘和栅极焊盘;从所述背面一侧去除所述漏极焊盘,以暴露出所述衬底靠近所述背面的表面,在所述正面上形成正面焊盘和塑封层,所述正面焊盘分别连接所述源极焊盘和栅极焊盘,所述正面焊盘外侧围设有所述塑封层;从所述背面对所述裸芯片进行失效定位。本发明的芯片背面分析过程中,通过在所述正面上形成正面焊盘和塑封层替代了现有技术中的封装,大大节省了封装成本、提高了裸芯片的失效分析时效性,裸芯片样品处理时间例如从现有的30天缩短至0.5小时。

30、另外,本发明的失效分析的全过程都在低于70℃的低温中完成,避免了现有技术从背面分析过程中封装时的高温过程,保证芯片失效模式不变,提高分析成功率。

技术特征:

1.一种功率器件的漏源极漏电流的软失效分析方法,其特征在于,包括以下步骤:

2.如权利要求1所述的功率器件的漏源极漏电流的软失效分析方法,其特征在于,所述正面包括第一部分和第二部分,所述第二部分围设在所述第一部分外侧;所述第一部分具有所述栅极焊盘以及所述栅极焊盘附近的钝化层和部分所述源极焊盘,且所述正面焊盘覆盖所述第一部分。

3.如权利要求2所述的功率器件的漏源极漏电流的软失效分析方法,其特征在于,去除所述漏极焊盘以及形成正面焊盘和塑封层的具体步骤为:

4.如权利要求1所述的功率器件的漏源极漏电流的软失效分析方法,其特征在于,所述正面焊盘上也覆盖有塑封层。

5.如权利要求4所述的功率器件的漏源极漏电流的软失效分析方法,其特征在于,在步骤从所述背面对所述裸芯片进行失效定位之前,研磨处理正面焊盘上的塑封层,以暴露出所述正面焊盘。

6.如权利要求5所述的功率器件的漏源极漏电流的软失效分析方法,其特征在于,去除所述漏极焊盘以及形成正面焊盘和塑封层的具体步骤为:

7.如权利要求5所述的功率器件的漏源极漏电流的软失效分析方法,其特征在于,去除所述漏极焊盘以及形成正面焊盘和塑封层的具体步骤为:

8.如权利要求3、6或7中任一项所述的功率器件的漏源极漏电流的软失效分析方法,其特征在于,所述焊料采用熔点低于70℃的固态金属。

9.如权利要求8所述的功率器件的漏源极漏电流的软失效分析方法,其特征在于,所述焊料采用伍德合金。

10.如权利要求1-7中任一项所述的功率器件的漏源极漏电流的软失效分析方法,其特征在于,所述塑封层采用固化温度小于70℃的塑封胶。

11.如权利要求10所述的功率器件的漏源极漏电流的软失效分析方法,其特征在于,所述塑封层采用ab胶。

12.如权利要求1-7中任一项所述的功率器件的漏源极漏电流的软失效分析方法,其特征在于,对所述裸芯片进行失效定位的方法为:

技术总结

本发明提供的一种功率器件的漏源极漏电流的软失效分析方法,包括提供裸芯片,裸芯片包括正面和背面,包括衬底,位于衬底一侧的MOS管、第一金属层和钝化层,位于衬底另一侧的第二金属层,第二金属层包括连接MOS管漏极的漏极焊盘,第一金属层包括源极焊盘及栅极焊盘,钝化层暴露出源极焊盘和栅极焊盘;从背面一侧去除漏极焊盘,暴露出衬底靠近背面的表面,在正面形成正面焊盘和塑封层,塑封层覆盖所述正面和所述正面焊盘,正面焊盘外侧围设有塑封层;从所述背面对裸芯片进行失效定位,在芯片背面分析过程中,通过在正面上形成正面焊盘和塑封层替代了现有技术中的封装,大大节省了封装成本、提高了裸芯片的失效分析时效性。

技术研发人员:王志明

受保护的技术使用者:绍兴中芯集成电路制造股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!