一种时间同步芯片装置以及时间同步方法与流程

本发明属于芯片,具体涉及一种时间同步芯片装置以及时间同步方法。

背景技术:

1、在芯片设计中,时间同步芯片是芯片中的一种,该芯片中的多个时钟模块的时钟需要保持同步,以确保数据传输,一般情况下,每个芯片均会有一个全局时钟模块用于基于校准时钟源来更新芯片的全局时钟,然后再根据更新后的全局时钟来同步芯片上的各个本地时钟。

2、在公布号cn116306414a中公开了一种芯片及其时间同步方法,该专利通过在每个子时钟内设置寄存器,实现动态配置全局时钟模块和本地时钟模块,但并没有公开对芯片本身结构做出改进,在实际使用中,整体防护性不足,以及在时间同步上过于依赖寄存器实现时间同步,在同步方法上较为单一,因此如何多元化实现时间同步时目前丞需解决的主要问题。

技术实现思路

1、本发明的目的在于提供一种时间同步芯片装置以及时间同步方法,以解决上述背景技术中提出的现有时间同步芯片在自身防护上存在不足,以及同步方法过于单一的问题。

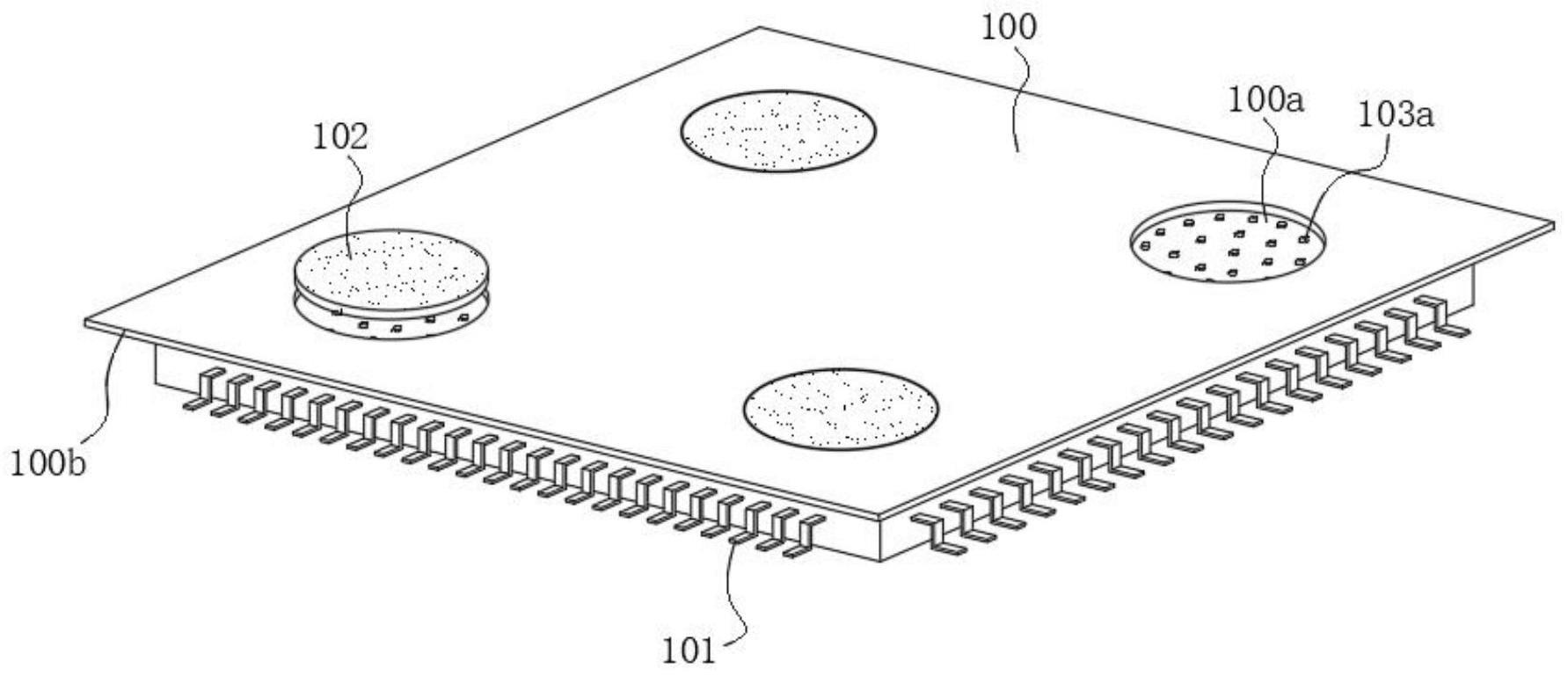

2、为实现上述目的,本发明提供如下技术方案:一种时间同步芯片装置,包括封装外壳,所述封装外壳的侧边均匀连接有引脚,所述封装外壳上设置有功能组件,该功能组件包括:

3、防护件,一体式设置在所述封装外壳的顶部,且该防护件将所述引脚部分或者整体覆盖;

4、散热件,由传导部和散热部构成,其中传导部设置在封装外壳内,而所述散热部设置在所述封装外壳的外部,并与所述散热部连接。

5、作为本发明中一种优选的技术方案,所述防护件为防护部,该防护部处于封装外壳的顶部位置,并朝向引脚的方向延伸,所述防护部与引脚之间不接触,从而预留空间方便对引脚与电路板的点焊操作。

6、作为本发明中一种优选的技术方案,所述散热件包括散热部包括内置在封装外壳内部的传导板,所述传导板的中部呈镂空状,避免与封装外壳内部的芯片接触,该传导板的四角处固定有一体式的传导柱,同样不与芯片接触,将芯片四周的热量进行收集,并方便后期的散热降温;所述封装外壳的顶端面开设有槽孔,而所述散热部为卡入至槽孔内的金属片,所述金属片与传导柱贴合连接,所述金属片的顶端面形成有散热翅片,当金属片接收到传导柱传输的热量后,可以通过金属片以及散热翅片实现快速散热;所述传导板的四角处形成有一体式的防护块,通过防护块能够方便传导板与封装外壳内部的分隔安装,使得传导板整体呈悬空状。

7、作为本发明中一种优选的技术方案,所述封装外壳内设置有芯片主体,该新篇章主体上集成有用于将外部时间参考信号与本地时钟进行同步的时钟同步模块、用于对本地时钟进行校准的时间同步算法模块,以及用于输出同步后的本地时钟信号的输出模块;

8、作为本发明中一种优选的技术方案,所述时钟同步模块包括:

9、时钟接收器,用于接收外部时间参考信号;

10、时钟生成器,用于生成本地时钟信号;

11、时钟比较器,用于比较外部时间参考信号和本地时钟信号的时间戳;

12、所述时间同步算法模块包括:

13、时间差计算器,用于计算外部时间参考信号和本地时钟信号的时间差;

14、频率和相位调整器,用于根据时间差调整本地时钟的频率和相位。

15、本发明还公开了一种时间同步芯片的时间同步方法,包括封装外壳,具体包括如下步骤:

16、步骤一:通过主方法同步时间,包括以下子步骤:

17、ⅰ、通过封装外壳内的时钟接收器接收外部时间参考信号,通过特定的验证算法对外部时间参考信号进行验证;

18、ⅱ、将外部时间参考信号与本地时钟进行同步;

19、ⅲ、通过时间同步算法对时钟生成器生成的本地时钟信号进行校准,以实现时间同步;

20、ⅳ、通过输出模块输出同步后的本地时钟信号;

21、步骤二:通过从方法同步时间,确保时间同步的准确性和稳定性,其中从方法具体包括以下子步骤:

22、ⅰ、验证主方法同步的时间准确性;

23、ⅱ、当主方法无法使用时,使用从方法进行时间同步;

24、ⅲ、接收外部时间参考信号,通过特定的验证算法对外部时间参考信号进行验证;

25、ⅳ、将外部时间参考信号与本地时钟进行同步;

26、ⅴ、通过时间同步算法对本地时钟进行校准,以实现时间同步;

27、ⅵ、输出同步后的本地时钟信号。

28、作为本发明中一种优选的技术方案,所述时间同步算法包括以下步骤:

29、a、分析外部时间参考信号的时间戳;

30、b、与本地时钟的时间戳进行比较,计算时间差;

31、c、根据时间差调整本地时钟的频率和相位;

32、d、重复步骤a至c直至本地时钟与外部时间参考信号同步。

33、作为本发明中一种优选的技术方案,所述步骤一与步骤二中,特定的验证算法包括一下算法中的任意一种:

34、时间戳比较算法:将外部时间参考信号的时间戳与本地时钟的时间戳进行比较,如果两者之间的差异在可接受的范围内,则认为外部时间参考信号是有效的;

35、时钟频率比较算法:通过比较外部时间参考信号的时钟频率与本地时钟的时钟频率,如果两者之间的差异在可接受的范围内,则认为外部时间参考信号是有效的;

36、时钟相位比较算法:通过比较外部时间参考信号的时钟相位与本地时钟的时钟相位,如果两者之间的差异在可接受的范围内,则认为外部时间参考信号是有效的。

37、与现有技术相比,本发明的有益效果是:

38、通过本发明的设计,能够提升芯片的防护、散热能力,避免在后期使用中出现损坏,有效延长使用寿命,保证正常使用不受影响,同时在本发明中,优化了时间同步的方法,采用主方法同步时间,从方法验证时间,并且在主方法无法使用中,通过从方法同步时间,提升时间同步的准确性和稳定性,完善了现有时间同步方法中存在的不足。

技术特征:

1.一种时间同步芯片装置,包括封装外壳(100),所述封装外壳(100)的侧边均匀连接有引脚(101),其特征在于:所述封装外壳(100)上设置有功能组件,该功能组件包括:

2.根据权利要求1所述的一种时间同步芯片装置,其特征在于:所述防护件为防护部(100b),该防护部(100b)处于封装外壳(100)的顶部位置,并朝向引脚(101)的方向延伸,所述防护部(100b)与引脚(101)之间不接触。

3.根据权利要求2所述的一种时间同步芯片装置,其特征在于:所述散热件包括散热部包括内置在封装外壳(100)内部的传导板(103),所述传导板(103)的中部呈镂空状,该传导板(103)的四角处固定有一体式的传导柱(103a);所述封装外壳(100)的顶端面开设有槽孔(100a),而所述散热部为卡入至槽孔(100a)内的金属片(102),所述金属片(102)与传导柱(103a)贴合连接,所述金属片(102)的顶端面形成有散热翅片(102a);所述传导板(103)的四角处形成有一体式的防护块(103b)。

4.根据权利要求1所述的一种时间同步芯片装置,其特征在于:所述封装外壳(100)内设置有芯片主体,该新篇章主体上集成有用于将外部时间参考信号与本地时钟进行同步的时钟同步模块、用于对本地时钟进行校准的时间同步算法模块,以及用于输出同步后的本地时钟信号的输出模块。

5.根据权利要求4所述的一种时间同步芯片装置,其特征在于:所述时钟同步模块包括:

6.一种时间同步芯片的时间同步方法,包括权利要求1至权利要求5中任一项所述的封装外壳(100),其特征在于:具体包括如下步骤:

7.根据权利要求1所述的一种时间同步芯片的时间同步方法,其特征在于:所述时间同步算法包括以下步骤:

8.根据权利要求1所述的一种时间同步芯片的时间同步方法,其特征在于:所述步骤一与步骤二中,特定的验证算法包括一下算法中的任意一种:

技术总结

本发明公开了一种时间同步芯片装置以及时间同步方法,包括封装外壳,所述封装外壳的侧边均匀连接有引脚,所述封装外壳上设置有功能组件,该功能组件包括防护件,一体式设置在所述封装外壳的顶部,且该防护件将所述引脚部分或者整体覆盖;散热件,由传导部和散热部构成,其中传导部设置在封装外壳内;通过本发明的设计,能够提升芯片的防护、散热能力,避免在后期使用中出现损坏,有效延长使用寿命,保证正常使用不受影响,同时在本发明中,优化了时间同步的方法,采用主方法同步时间,从方法验证时间,并且在主方法无法使用中,通过从方法同步时间,提升时间同步的准确性和稳定性,完善了现有时间同步方法中存在的不足。

技术研发人员:周经亚,王玉和

受保护的技术使用者:苏州时同奥科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!