半导体装置的制作方法

本发明涉及半导体装置。

背景技术:

1、专利文献1的图14公开了一种半导体装置,其包含:形成有栅极沟槽的sic外延层、因栅极沟槽而以彼此分离的方式形成于sic外延层的肖特基单元和pn二极管单元。

2、在该半导体装置中,利用肖特基单元形成了肖特基势垒二极管。另外,利用pn二极管单元形成了misfet(metal insulator semiconductor field effect transistor:金属绝缘体半导体场效应晶体管)。

3、在sic外延层由一个肖特基单元、和围绕该一个肖特基单元的多个pn二极管单元形成了一个单元组。在sic外延层呈矩阵状排列有多个这种结构的单元组。

4、现有技术文献

5、专利文献

6、专利文献1:国际公开第2012/105611a1号

技术实现思路

1、发明所要解决的课题

2、本案发明人对于专利文献1的半导体装置进行了深入研究,结果发现肖特基势垒二极管的导通损失仍有降低的余地。如果正向电流的增加率相对于正向电压的增加率而言越大,则肖特基势垒二极管的导通损失就越小。

3、专利文献1的半导体装置具有肖特基单元和pn二极管单元彼此分开地做成的结构。在这种结构中,肖特基单元用的电流路径和pn二极管单元用的电流路径在半导体层内分散。

4、因此,即使增加正向电压也无法使正向电流如期待的那样上升。这种问题会妨碍肖特基势垒二极管的导通损失的降低。

5、因此,本发明的一实施方式提供一种半导体装置,其能够降低肖特基势垒二极管的导通损失。

6、用于解决课题的方案

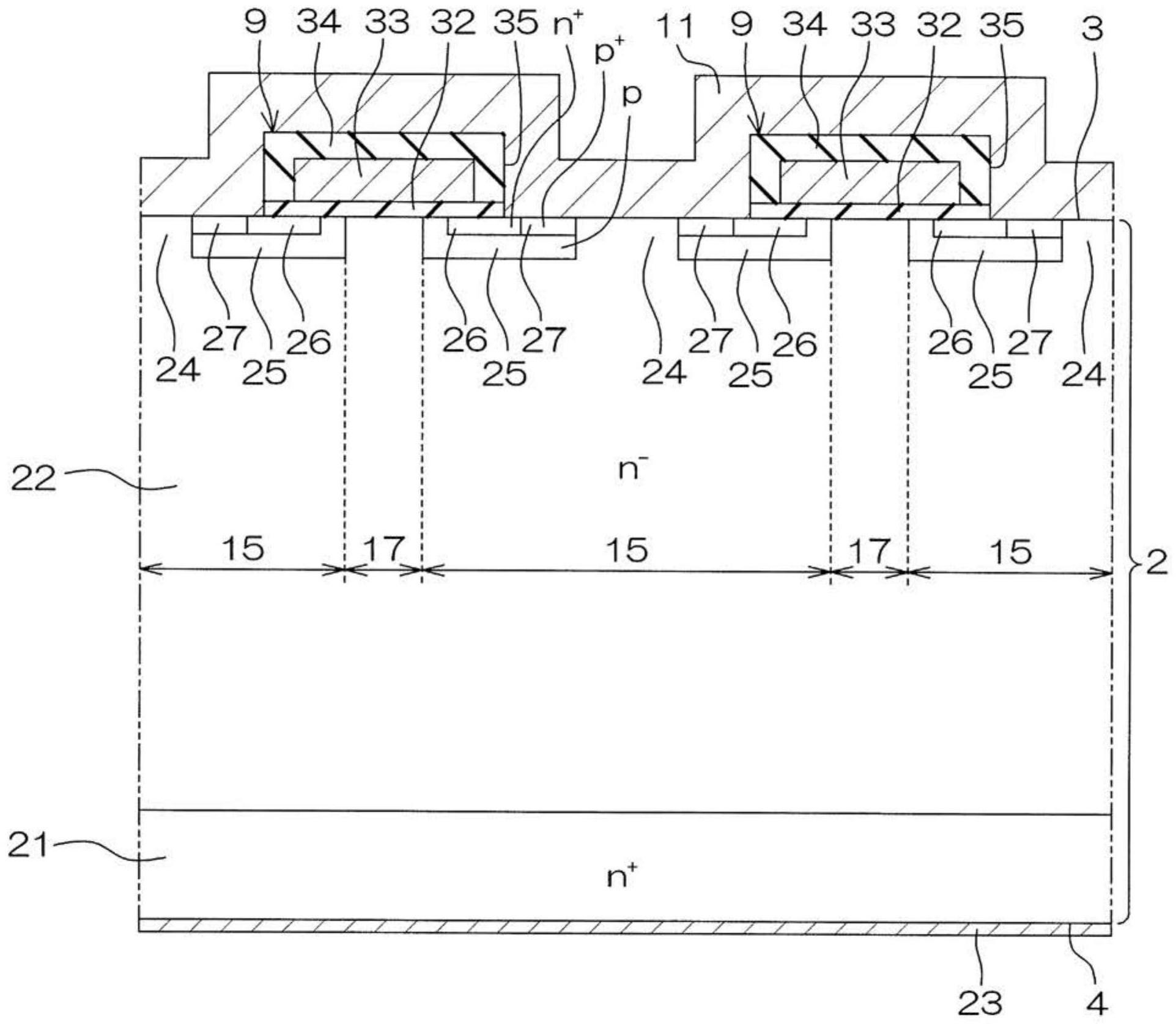

7、本发明的一实施方式提供一种半导体装置,其包含:半导体层,其具有一侧的第一主面和另一侧的第二主面;单位单元,其包含:在所述半导体层的所述第一主面的表层部形成的第一导电型的二极管区域、在所述半导体层的所述第一主面的表层部沿着所述二极管区域的周缘形成的第二导电型的阱区、以及在所述阱区的表层部形成的第一导电型区域;栅极电极层,其隔着栅极绝缘层与所述阱区及所述第一导电型区域对置;以及第一主面电极,其在所述半导体层的所述第一主面上包覆所述二极管区域和所述第一导电型区域,并在与所述二极管区域之间形成肖特基接合,且在与所述第一导电型区域之间形成欧姆接合。

8、根据该半导体装置,第一主面电极在与二极管区域之间形成了肖特基接合,并在与晶体管的第一导电型区域之间形成了欧姆接合。由此,在一个单位单元中形成了肖特基势垒二极管以及绝缘栅极型的晶体管。

9、因此,肖特基势垒二极管用的电流路径以及晶体管用的电流路径在半导体层形成于单位单元的正下方的区域。由此,能够抑制肖特基势垒二极管用的电流路径以及晶体管用的电流路径在半导体层内分散的情况。其结果是,能够相对于正向电压的增加率而言提高正向电流的增加率,从而能够降低肖特基势垒二极管的导通损失。

10、关于本发明的上述的、或者此外其它的目的、特征以及效果,通过参照附图对下述实施方式进行说明而更加明了。

技术特征:

1.一种半导体装置,其特征在于,包含:

2.根据权利要求1所述的半导体装置,其特征在于,

3.根据权利要求1或2所述的半导体装置,其特征在于,

4.根据权利要求1至3中任一项所述的半导体装置,其特征在于,

5.根据权利要求4所述的半导体装置,其特征在于,

6.根据权利要求1至5中任一项所述的半导体装置,其特征在于,

7.根据权利要求6所述的半导体装置,其特征在于,

8.根据权利要求7所述的半导体装置,其特征在于,

9.根据权利要求7所述的半导体装置,其特征在于,

10.根据权利要求1至9中任一项所述的半导体装置,其特征在于,

11.根据权利要求1至10中任一项所述的半导体装置,其特征在于,

12.根据权利要求1至11中任一项所述的半导体装置,其特征在于,

13.根据权利要求12所述的半导体装置,其特征在于,

14.根据权利要求12或13所述的半导体装置,其特征在于,

15.根据权利要求1至14中任一项所述的半导体装置,其特征在于,

16.根据权利要求15所述的半导体装置,其特征在于,

17.根据权利要求15或16所述的半导体装置,其特征在于,

18.根据权利要求1至17中任一项所述的半导体装置,其特征在于,

19.根据权利要求1至18中任一项所述的半导体装置,其特征在于,

20.根据权利要求19所述的半导体装置,其特征在于,

21.根据权利要求1至20中任一项所述的半导体装置,其特征在于,

22.根据权利要求1至21中任一项所述的半导体装置,其特征在于,

23.一种半导体装置,其特征在于,包含:

24.一种半导体装置,其特征在于,包含:

25.一种半导体装置,其特征在于,包含:

26.一种半导体装置,其特征在于,包含:

27.一种半导体装置,其特征在于,包含:

28.一种半导体装置,其特征在于,包含:

29.一种半导体装置,其特征在于,包含:

30.一种半导体装置,其特征在于,包含:

技术总结

本发明提供一种半导体装置,其包含:半导体层,其具有一侧的第一主面和另一侧的第二主面;单位单元,其包含:在所述半导体层的所述第一主面的表层部形成的第一导电型的二极管区域、在所述半导体层的所述第一主面的表层部沿着所述二极管区域的周缘形成的第二导电型的阱区、以及在所述阱区的表层部形成的第一导电型区域;栅极电极层,其隔着栅极绝缘层与所述阱区及所述第一导电型区域对置;以及第一主面电极,其在所述半导体层的所述第一主面上包覆所述二极管区域和所述第一导电型区域,并在与所述二极管区域之间形成肖特基接合,且在与所述第一导电型区域之间形成欧姆接合。

技术研发人员:坂口拓生,明田正俊,中野佑纪

受保护的技术使用者:罗姆股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!