一种半导体器件的形成方法及半导体器件与流程

本发明涉及半导体器件的形成方法,特别涉及一种半导体器件保护层的形成方法。

背景技术:

1、在半导体领域中,功率器件(例如mosfet)因为其具有电压控制、单极导电等特点被广泛应用于高频低功耗的场合中。近年来,随着新能源产业的兴起,功率器件被大量运用于电动汽车的电控系统中,因此mosfet器件的可靠性稳定性就越来越被人们重视。

2、现有技术中,造成功率mosfet器件可靠性失效的因素很多。其中晶圆与封装工艺应力不匹配,导致晶圆端保护层(passivationlayer,简称pa)失效是常见的原因之一。一般情况下,保护层是由氮化硅层(sin)组成,但是氮化硅层(sin)具有较好的致密性可以很好的隔绝外界可动离子及湿气进入器件内部。但是sin本身应力值较大,容易造成氮化硅层(sin)与封装材料应力不匹配,在严重的情况下巨大的应力会导致保护层开裂(pa crack),这对于器件的可靠性及稳定性均带来极大的隐患。

3、因此急需一种防开裂的保护层,提高功率器件的稳定性。

技术实现思路

1、本发明的目的是提供一种半导体器件的形成方法,从而有效降低保护层与封装材料的应力。

2、为了实现以上目的,本发明通过以下技术方案实现:

3、提供一种半导体器件的形成方法,包括步骤:

4、s1、形成初步半导体器件;

5、s2、在所述初步半导体器件上沉积氮化硅层;

6、s3、在所述氮化硅层上沉积顶部氧化层,以形成保护层。

7、进一步,在所述步骤s2之前还包括步骤:在所述初步半导体器件上沉积底部氧化层。

8、进一步,所述顶部氧化层的厚度为

9、进一步,在所述步骤s1中,所述初步半导体器件为mosfet。

10、进一步,在所述步骤s1中,所述初步半导体器件为sgt-mosfet、igbt或超结。

11、进一步,在所述步骤s1中,形成初步半导体器件包括:

12、s11、提供一衬底,在所述衬底上沉积外延层;然后在外延层上通过刻蚀法刻蚀出沟槽;

13、s12、在所述沟槽及外延层的表面形成热氧化层;

14、s13、在所述热氧化层表面沉积栅极多晶硅;

15、s14、通过刻蚀法刻蚀所述栅极多晶硅;

16、s15、主体离子注入及推阱,形成p型阱;

17、s16、源离子注入及激活,形成源区;

18、s17、沉积层间介质层;

19、s18、接触孔刻蚀,在所述接触孔中沉积钨金属;

20、s19、沉积顶部金属层及刻蚀,形成初步半导体器件。

21、本发明还提供一种半导体器件,通过上述的半导体器件的形成方法制造。

22、与现有技术相比,本发明具有如下优点:

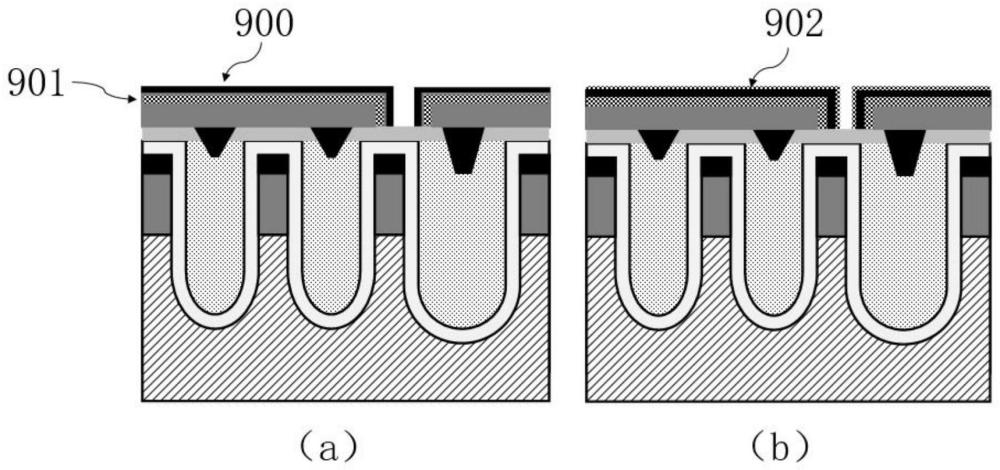

23、本发明提供的功率器件形成方法,保护层由氮化硅层和顶部氧化层组成,或由底部氧化层、氮化硅层和顶部氧化层(ono,即oxide+sin+oxide)组成,利用顶部氧化层本身应力值比氮化硅层低的特点可以更好的与封装材料做应力匹配,从而提高器件的稳定性。

技术特征:

1.一种半导体器件的形成方法,其特征在于,包括步骤:

2.如权利要求1所述的半导体器件的形成方法,其特征在于,在所述步骤s2之前还包括步骤:在所述初步半导体器件上沉积底部氧化层。

3.如权利要求1所述的半导体器件的形成方法,其特征在于,所述顶部氧化层的厚度为

4.如权利要求1所述的半导体器件的形成方法,其特征在于,在所述步骤s1中,所述初步半导体器件为mosfet。

5.如权利要求1所述的半导体器件的形成方法,其特征在于,在所述步骤s1中,所述初步半导体器件为sgt-mosfet、igbt或超结。

6.如权利要求1所述的半导体器件的形成方法,其特征在于,在所述步骤s1中,形成初步半导体器件包括:

7.一种半导体器件,通过如权利要求1-6任一所述的半导体器件的形成方法制造。

技术总结

本发明提供一种半导体器件的形成方法,包括步骤:S1、形成初步半导体器件;S2、在所述初步半导体器件上沉积氮化硅层;S3、在所述氮化硅层上沉积顶部氧化层,以形成保护层。本发明提供的保护层可以有效降低保护层与封装材料的应力,最终提高器件的可靠性及稳定性。

技术研发人员:刘科科,钟义栋,董云

受保护的技术使用者:中晶新源(上海)半导体有限公司

技术研发日:

技术公布日:2024/1/5

- 还没有人留言评论。精彩留言会获得点赞!