一种刻蚀方法与流程

本发明涉及半导体,具体涉及一种刻蚀方法。

背景技术:

1、在半导体微纳制造中,通过光刻技术将掩模版上的图案转移到光刻胶上,然后利用干法刻蚀将光刻胶上的图案转移到半导体衬底上,是一种广泛被用来制造各种微纳器件的通用方法。ⅲ-ⅴ族化合物半导体材料如gaas、gan和inp等半导体在以光刻后的光刻胶作为掩膜图案进行干法刻蚀时,其选择比通常较低,难以在一定光刻胶厚度下实现较深的半导体材料刻蚀,也就是说刻蚀图形的高宽比较小。目前为了提高光刻胶和ⅲ-ⅴ族化合物半导体材料的刻蚀选择比,经常通过增加一层介质层如sin、sio2和al2o3等硬膜进行掩膜刻蚀,然而上述的方法会导致器件的制备工艺流程复杂、成本增加并且产品的生产效率及良率降低,且刻蚀图形的高宽比还有待提高。

技术实现思路

1、因此,本发明要解决的技术问题在于刻蚀图形的高宽比较小的问题,从而提供一种刻蚀方法。

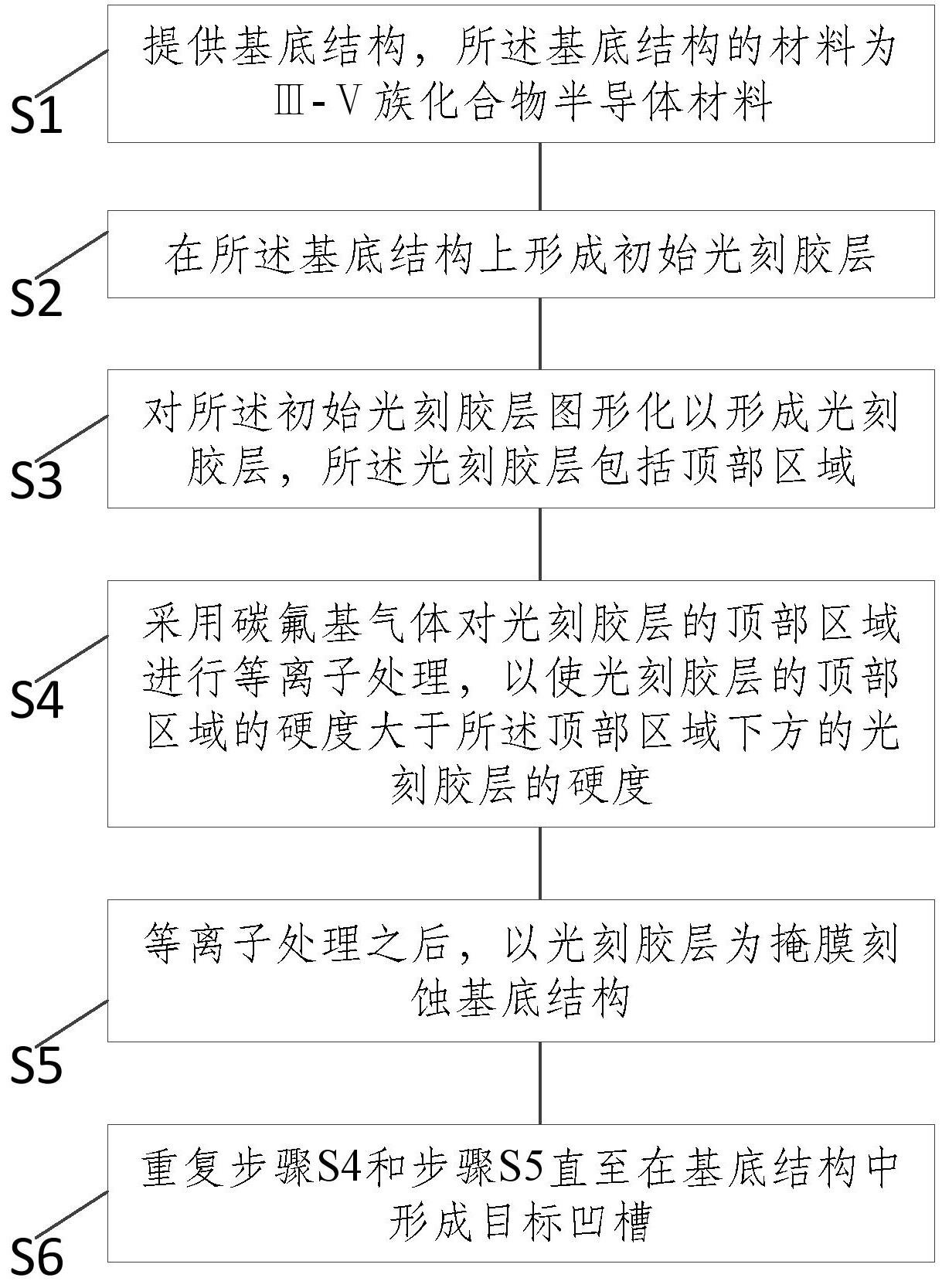

2、本发明提供一种刻蚀方法,包括:步骤s1:提供基底结构,所述基底结构的材料为ⅲ-ⅴ族化合物半导体材料;步骤s2:在所述基底结构上形成初始光刻胶层;步骤s3:对所述初始光刻胶层图形化以形成光刻胶层,所述光刻胶层包括顶部区域;步骤s4:采用碳氟基气体对光刻胶层的顶部区域进行等离子处理,以使光刻胶层的顶部区域的硬度大于所述顶部区域下方的光刻胶层的硬度;步骤s5:等离子处理之后,以光刻胶层为掩膜刻蚀基底结构;步骤s6:重复步骤s4和步骤s5直至在基底结构中形成目标凹槽。

3、可选的,重复步骤s4和步骤s5的次数为1次~20次。

4、可选的,在步骤s3中,顶部区域的高度为10nm~100nm。

5、可选的,所述等离子处理采用的等离子体设备为反应离子刻蚀机、电感耦合等离子刻蚀机、电子回旋共振等离子体刻蚀机。

6、可选的,所述碳氟基气体包括cf4、chf3或c4f8。

7、可选的,所述等离子处理采用的射频功率为500w~2000w。

8、可选的,所述等离子处理采用的温度为20℃-80℃。

9、可选的,所述等离子处理采用的时间范围为1s-3600s。

10、可选的,步骤s4和步骤s5在同一工艺腔室内进行。

11、本发明技术方案提供具有以下有益效果:

12、本发明技术方案提供的刻蚀方法,采用碳氟基气体对光刻胶层的顶部区域进行等离子处理,以使光刻胶层的顶部区域的硬度大于所述顶部区域下方的光刻胶层的硬度,所述光刻胶层的顶部区域为碳化交联聚合物硬壳。以光刻胶层为掩膜刻蚀基底结构。重复步骤s4和步骤s5直至在基底结构中形成目标凹槽。这样使得光刻胶层和基底结构的刻蚀选择比提高,目标凹槽的深度提高,目标凹槽的高宽比较大。重复刻蚀多次的好处包括:目标凹槽的深度提高时,重复刻蚀多次能够能使每次刻蚀持续的时间降低,避免刻蚀时间过长导致基底结构的温度升高很多,进而避免影响光刻胶层的形貌,避免影响目标凹槽的刻蚀形貌,这种重复刻蚀过程能够有利于刻蚀过程中基底结构的温度的控制和目标凹槽形貌的保持。光刻胶层的重复硬化都只发生在光刻胶层的顶部,不会影响重复刻蚀后剩余光刻胶层的去除,且在碳氟基气体的等离子处理过程中,光刻胶层的侧壁形貌保持稳定。重复刻蚀能够在以光刻胶层为掩膜前提下实现较大的深宽比刻蚀,能够解决生产过程中刻蚀选择比低及刻蚀深度不足的问题。

13、进一步,重复步骤s4和步骤s5在同一工艺腔室内进行,不会增加工艺操作上的复杂程度,降低生产过程中成本高、流程复杂等问题。

技术特征:

1.一种刻蚀方法,其特征在于,包括:

2.根据权利要求1所述的刻蚀方法,其特征在于,重复步骤s4和步骤s5的次数为1次~20次。

3.根据权利要求1所述的刻蚀方法,其特征在于,在步骤s3中,顶部区域的高度为10nm~100nm。

4.根据权利要求1所述的刻蚀方法,其特征在于,所述等离子处理采用的等离子体设备为反应离子刻蚀机、电感耦合等离子刻蚀机、电子回旋共振等离子体刻蚀机。

5.根据权利要求1所述的刻蚀方法,其特征在于,所述碳氟基气体包括cf4、chf3或c4f8。

6.根据权利要求1所述的刻蚀方法,其特征在于,所述等离子处理采用的射频功率为500w~2000w。

7.根据权利要求1所述的刻蚀方法,其特征在于,所述等离子处理采用的温度为20℃-80℃。

8.根据权利要求1所述的刻蚀方法,其特征在于,所述等离子处理采用的时间范围为1s-3600s。

9.根据权利要求1所述的刻蚀方法,其特征在于,步骤s4和步骤s5在同一工艺腔室内进行。

技术总结

本发明揭示了一种刻蚀方法,包括:步骤S1:提供基底结构,所述基底结构的材料为Ⅲ‑Ⅴ族化合物半导体材料;步骤S2:在所述基底结构上形成初始光刻胶层;步骤S3:对所述初始光刻胶层图形化以形成光刻胶层,所述光刻胶层包括顶部区域;步骤S4:采用碳氟基气体对光刻胶层的顶部区域进行等离子处理,以使光刻胶层的顶部区域的硬度大于所述顶部区域下方的光刻胶层的硬度;步骤S5:等离子处理之后,以光刻胶层为掩膜刻蚀基底结构;步骤S6:重复步骤S4和步骤S5直至在基底结构中形成目标凹槽。所述刻蚀方法具有高的刻蚀选择比。

技术研发人员:李刘晶,刘恒,王俊,赵武,李顺峰

受保护的技术使用者:苏州长光华芯光电技术股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!