一种半导体器件结构及其制备方法与流程

本发明实施例涉及半导体器件,尤其涉及一种半导体器件结构及其制备方法。

背景技术:

1、随着半导体技术的发展,金属-氧化物-半导体场效应晶体管(metal oxidesemiconductor field effect transistor,mosfet)发展出平面栅型mosfet、沟槽栅型mosfet、屏蔽栅沟槽型mosfet和超结mosfet等多种mos管结构。其中,沟槽型mosfet具有较大的沟道密度、较低的功耗损失,

2、目前,现有的沟槽栅型mosfet器件,其栅极电阻通常较大,mosfet器件的开关响应速率较低。现有技术通过改进器件结构以降低栅极电阻,但器件结构的耐受非嵌位感性负载开关过程的能力(unclamped inductive switching,uis能力)不稳定且较差。

3、基于此,设计一种既可降低栅极电阻,又具有稳定且较强的耐受uis能力的mosfet器件成为亟待解决的问题。

技术实现思路

1、本发明提供一种半导体器件结构及其制备方法,以降低栅极电阻,增强耐受uis能力。

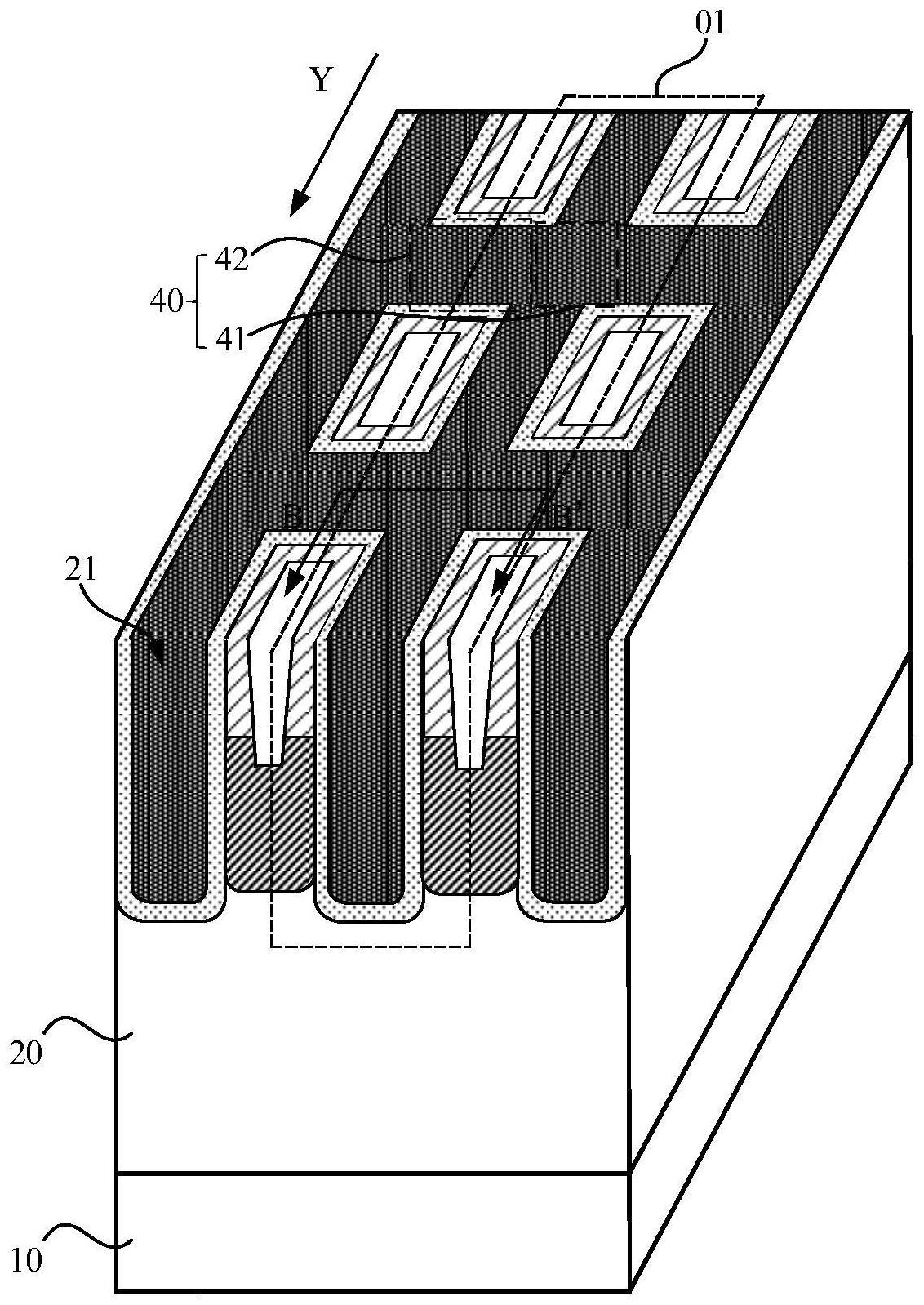

2、根据本发明的一方面,提供了一种半导体器件结构,包括:

3、衬底;

4、外延层,位于所述衬底一侧,所述外延层设置有多个沟槽,所述外延层在相邻所述沟槽之间的表面为平面,所述沟槽内设置栅极,以及设置于所述沟槽与所述栅极之间的栅极绝缘层,所述栅极绝缘层延伸至所述外延层在相邻所述沟槽之间的表面;

5、掺杂区,位于所述外延层中所述沟槽的两侧;

6、栅极连接部,位于相邻两所述沟槽之间的所述栅极绝缘层上以及部分所述栅极上,所述栅极连接部连接相邻所述沟槽中的所述栅极。

7、可选地,所述栅极连接部包括第一子连接部和第二子连接部;

8、所述第一子连接部设置于所述栅极远离所述衬底一侧的表面,所述第二子连接部设置于相邻所述沟槽之间的所述外延层表面;

9、所述第一子连接部与所述第二子连接部一体设置。

10、可选地,沿所述沟槽的延伸方向,多个所述栅极连接部在所述栅极绝缘层上以及部分所述栅极上间隔平行排布。

11、可选地,所述半导体器件结构包括至少一个元胞;所述栅极连接部在所述衬底上的正投影将所述元胞的正投影划分为多个矩形区域。

12、可选地,所述掺杂区包括层叠设置的p-阱区和n+阱区;

13、所述p-阱区的深度小于所述沟槽的深度。

14、可选地,该半导体器件结构,还包括:介电层、第一金属层和第二金属层;

15、所述介电层设置于所述栅极连接部远离所述衬底一侧的表面,所述介电层设置有接触孔;所述接触孔贯穿所述n+阱区,且所述接触孔的底部延伸至所述p-阱区;

16、所述第一金属层设置于所述介电层远离所述栅极连接部一侧的表面;其中,所述第一金属层在对应于所述接触孔的位置填充于所述接触孔中;

17、所述第二金属层设置于所述衬底远离所述外延层的一侧。

18、根据本发明的另一方面,提供了一种半导体器件结构的制备方法,包括:

19、提供一衬底;

20、在所述衬底一侧形成外延层;所述外延层中设置有多个沟槽,所述外延层在相邻所述沟槽之间的表面为平面,所述沟槽内设置栅极,以及设置于所述沟槽与所述栅极之间的栅极绝缘层,所述栅极绝缘层延伸至所述外延层在相邻所述沟槽之间的表面;

21、在所述外延层中所述沟槽的两侧形成掺杂区;

22、在相邻两所述沟槽之间的所述栅极绝缘层上以及部分所述栅极上形成栅极连接部;所述栅极连接部连接相邻所述沟槽中的所述栅极。

23、可选地,所述在所述衬底一侧形成外延层,包括:

24、对所述外延层远离所述衬底一侧的表面进行图形化形成刻蚀图案,并由刻蚀图案向所述衬底方向刻蚀形成沟槽;

25、在所述外延层远离所述衬底一侧的表面形成栅极绝缘层;

26、在所述栅极绝缘层远离所述外延层一侧的表面形成栅极材料层,栅极材料层将所述沟槽填充满,形成栅极。

27、可选地,所述在相邻两所述沟槽之间的所述栅极绝缘层上以及部分所述栅极上形成栅极连接部,包括:

28、对所述栅极绝缘层和所述栅极材料层进行图形化,刻蚀形成设置于所述栅极远离所述衬底一侧表面的第一子连接部,以及设置于相邻所述沟槽之间的所述外延层表面的第二子连接部;

29、和/或,

30、所述掺杂区包括层叠设置的p-阱区和n+阱区;

31、所述在所述外延层中所述沟槽的两侧形成掺杂区,包括:

32、在形成所述栅极绝缘层后,在所述栅极绝缘层远离所述衬底一侧的表面向所述衬底的方向,形成p-阱区;在形成所述栅极连接部后,在所述栅极连接部远离所述衬底一侧的表面向所述衬底的方向,形成n+阱区。

33、可选地,该半导体器件结构的制备方法,还包括:

34、在所述栅极连接部远离所述衬底一侧的表面形成介电层;所述介电层设置有接触孔;所述接触孔贯穿所述n+阱区,且所述接触孔的底部延伸至所述p-阱区;

35、在所述介电层远离所述栅极连接部一侧的表面形成第一金属层;其中,所述第一金属层在对应于所述接触孔的位置填充于所述接触孔中;

36、在所述衬底远离所述外延层的一侧形成第二金属层。

37、本发明实施例提供的技术方案通过在设置于衬底一侧的外延层中设置多个沟槽,沟槽中设置有栅极。在沟槽两侧的外延层中设置有掺杂区,并将掺杂区作为半导体器件中元胞的沟道。在掺杂区远离衬底一侧的栅极绝缘层表面以及相邻两沟槽中栅极的部分表面,设置有栅极连接部,使得栅极连接部可将相邻两沟槽中的栅极实现电连接,增加半导体器件中的电流传输通道的数量,从而有利于降低栅极电阻。并且在与相邻两沟槽之间的掺杂区对应的位置,栅极连接部仅在掺杂区远离衬底一侧的表面设置,使得相邻两沟槽之间的掺杂区仍为连续的条形,因此,半导体器件产生的工作电流可在连续的条形掺杂区内均匀流动,从而使半导体器件具有稳定且较强的耐受uis的能力。

38、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种半导体器件结构,其特征在于,包括:

2.根据权利要求1所述的半导体器件结构,其特征在于,所述栅极连接部包括第一子连接部和第二子连接部;

3.根据权利要求1所述的半导体器件结构,其特征在于,

4.根据权利要求3所述的半导体器件结构,其特征在于,所述半导体器件结构包括至少一个元胞;所述栅极连接部在所述衬底上的正投影将所述元胞的正投影划分为多个矩形区域。

5.根据权利要求1所述的半导体器件结构,其特征在于,所述掺杂区包括层叠设置的p-阱区和n+阱区;

6.根据权利要求5所述的半导体器件结构,其特征在于,还包括:介电层、第一金属层和第二金属层;

7.一种半导体器件结构的制备方法,其特征在于,包括:

8.根据权利要求7所述的半导体器件结构的制备方法,其特征在于,所述在所述衬底一侧形成外延层,包括:

9.根据权利要求8所述的半导体器件结构的制备方法,其特征在于,所述在相邻两所述沟槽之间的所述栅极绝缘层上以及部分所述栅极上形成栅极连接部,包括:

10.根据权利要求9所述的半导体器件结构的制备方法,其特征在于,还包括:

技术总结

本发明公开了一种半导体器件结构及其制备方法。该半导体器件结构包括:衬底、外延层、掺杂区和栅极连接部;外延层位于衬底一侧,外延层设置有多个沟槽,外延层在相邻沟槽之间的表面为平面,沟槽内设置栅极,以及设置于沟槽与栅极之间的栅极绝缘层,栅极绝缘层延伸至外延层在相邻沟槽之间的表面;掺杂区位于外延层中沟槽的两侧;栅极连接部位于相邻两沟槽之间的栅极绝缘层上以及部分栅极上,栅极连接部连接相邻沟槽中的栅极。本发明实施例的技术方案有利于降低栅极电阻,且提高半导体器件耐受UIS的能力,使其具有稳定的耐受UIS的能力。

技术研发人员:田甜,张伟,蔡政坤,廖光朝

受保护的技术使用者:深圳云潼微电子科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!