一种半导体功率器件的制作方法

本发明涉及半导体,尤其涉及一种半导体功率器件。

背景技术:

1、对功率器件vdmos而言,具体的结构设计常常需要在导通电阻和最大阻断耐压值之间取得平衡。提高外延层的掺杂浓度或增加结型场效应(jfet)区域的宽度,都能提高导通电阻。但无论是高的外延层浓度还是宽的jfet宽度,都会使器件的阻断(耐击穿)性能恶化。宽的jfet还会使场氧化层在阻断模式中承受更高的电场,从而降低场氧的长期可靠性。

2、在vdmos的结构设计中,需要同时虑及导通电阻和阻断耐压性能。为了保证阻断耐压性能,外延n-的掺杂浓度必须足够低。以保证阻断状态时n-的耗尽区有足够的宽度来承担漏极的高压。但因为外延层,特别是jfet区域,是电流通道的重要部分,低掺杂的外延n-会显著增加器件的导通电阻。

3、为了在有限的外延n-的掺杂浓度下增加导电性能,常常使用的一种方法是增加jfet区域的宽度。但是jfet的最大宽度受阻断性能的制约。同时,宽的jfet会使场氧直接更多地暴露在高电场之下,因此会降低器件的长期可靠性,特别是氧化物相关的可靠性,例如tddb(time to breakdown),nbti(negative bias temperature instability)等等。其中ntbi还会引起阈值电压漂移,造成器件操作窗口变化。

4、如上文所言,导通电阻跟阻断耐压是一对互相制约的参数。在现有的器件结构上,原则上不可能提升一个参数性能而不影响另外一个性能。

技术实现思路

1、本发明为了解决至少一种现有技术中的缺点,提供了一种采用超结结构来平衡vdmos耐压性能和导通电阻的半导体功率器件。

2、具体方案如下文:

3、一种半导体功率器件,包括:

4、衬底,

5、漂移层,漂移层位于所述衬底的上表面;

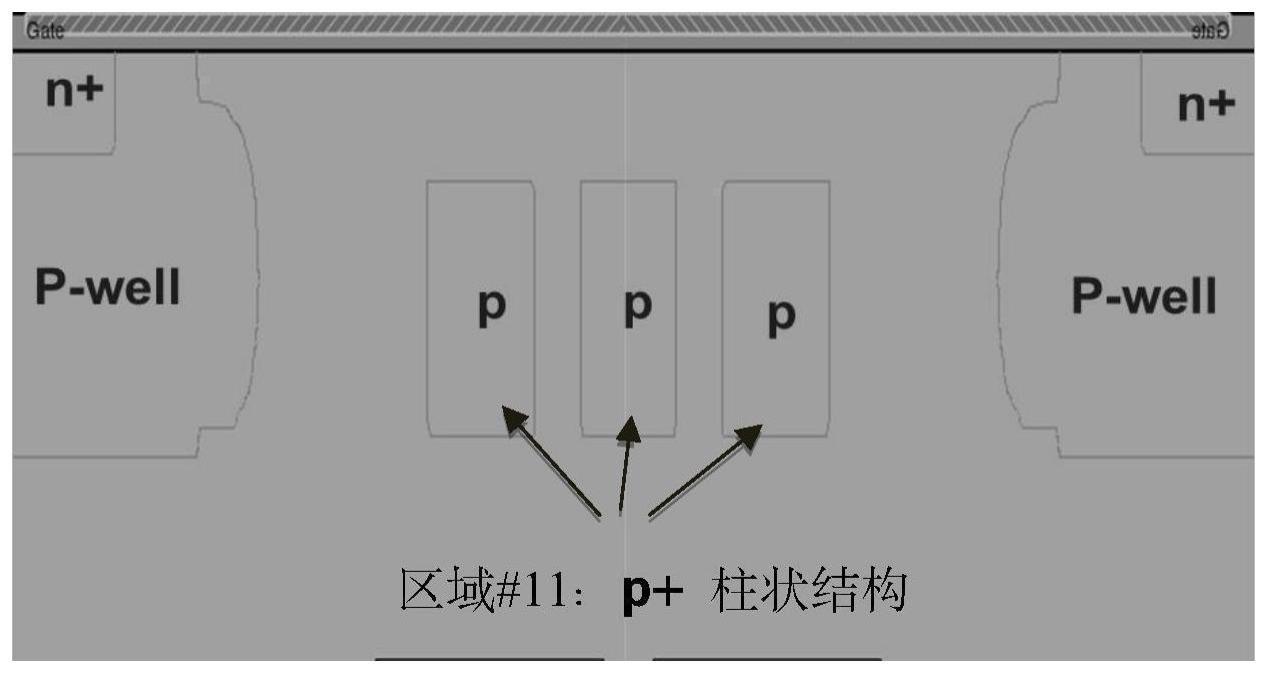

6、阱区,阱区之间形成jfet区,其中漂移层的jfet区设置有一个以上柱状结构;

7、其中所述漂移区为第一导电类型,漂移层的jfet区设置的柱状结构是与所述第一导电类型相反的第二导电类型;

8、源区,设置在阱区的上表面;

9、栅氧层,栅氧层位于漂移层的上表面,且与所述阱区和源区接触;

10、栅电极、源电极和漏电极。

11、优选的,所述柱状结构的掺杂浓度在5x1017/cm3到5x1018/cm3之间。

12、优选的,所述柱状结构的下沿与阱区下沿对齐。以保证柱状结构能与阱区在阻断过程中的耗尽区前沿能一致变化。

13、优选的,所述柱状结构之间的间隔为0.2微米至1微米。

14、优选的,所述柱状结构与场氧层的距离为0.2微米至1微米之间。

15、优选的,所述柱状结构在半导体功率器件横切面上的分布包括蜂窝分布、阵列分布或单列分布;

16、所述柱状结构在半导体功率器件横切面上的形状包括三角形、圆形、椭圆形、矩形、正n边形中的任意一种或多种。

17、优选的,所有所述柱状结构尺寸均相同。

18、优选的,至少有一个所述柱状结构的尺寸与其他所述柱状结构的尺寸不同。

19、优选的,器件包括n沟道功率器件。

20、优选的,器件包括p沟道功率器件。

21、本发明的有益效果:

22、本发明通过在jfet区域引入超结(super junction)结构,使耗尽区域在横向能通过超结原理而具有可延展性。优化的超结结构能保证导通通道的扩展的同时,不影响阻断耐压性能。同时也能确保场氧不会直接暴露于高电压之下,因此器件长期的可靠性不会受到损害。

23、相比于传统vdmos或者jfet掺杂增强的vdmos器件,本技术能同时改善导通电流、阻断电压和场氧在阻断偏压下的场强。

24、本技术具有可延展性,能够依靠增加超结单元的数目而持续提升导通电流,而不会影响阻断电压和场氧在阻断偏压下的场强。

技术特征:

1.一种半导体功率器件,其特征在于,包括:

2.根据权利要求1所述的半导体功率器件,其特征在于,所述柱状结构的掺杂浓度在5x1017/cm3到5x1018/cm3之间。

3.根据权利要求1所述的半导体功率器件,其特征在于,所述柱状结构的下沿与阱区下沿对齐。

4.根据权利要求1所述的半导体功率器件,其特征在于,所述柱状结构之间的间隔为0.2微米至1微米。

5.根据权利要求1所述的半导体功率器件,其特征在于,所述柱状结构与场氧层的距离为0.2微米至1微米之间。

6.根据权利要求1所述的半导体功率器件,其特征在于,所述柱状结构在半导体功率器件横切面上的分布包括蜂窝分布、阵列分布或单列分布;

7.根据权利要求1所述的半导体功率器件,其特征在于,所有所述柱状结构尺寸均相同。

8.根据权利要求1所述的半导体功率器件,其特征在于,至少有一个柱状结构的尺寸与其他柱状结构的尺寸不同。

9.根据权利要求1所述的半导体功率器件,其特征在于,器件包括n沟道功率器件。

10.根据权利要求1所述的半导体功率器件,其特征在于,器件包括p沟道功率器件。

技术总结

本发明公开一种半导体功率器件,涉及半导体技术领域,包括:衬底,漂移层,漂移层位于所述衬底的上表面;阱区,阱区之间形成JFET区,其中漂移层的JFET区设置有一个以上柱状结构;其中所述漂移区为第一导电类型,漂移层的JFET区设置的柱状结构是与所述第一导电类型相反的第二导电类型;源区,设置在阱区的上表面;栅氧层,栅氧层位于漂移层的上表面,且与所述阱区和源区接触;栅电极、源电极和漏电极。本发明引入一个以上柱状掺杂区域。此种n/p交替的结构,平衡VDMOS耐压性能和导通电阻的半导体功率器件。

技术研发人员:朱炎

受保护的技术使用者:海科(嘉兴)电力科技有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!