半导体测试结构的制作方法

本申请涉及半导体,具体涉及一种半导体测试结构。

背景技术:

1、动态随机存储器等半导体器件内部,通常容易发生短路和/或开路等缺陷,例如wl(字线)等导线之间容易发生短路缺陷,又例如相邻功能结构之间的接触插塞容易出现开路缺陷等等。

2、检测设备可以向半导体器件施加检测信号实现对半导体器件的检测,例如电子束缺陷检测(ebi)设备可以利用电子束检测技术对半导体器件表面进行高分辨率成像,通过相关算法检测半导体器件的缺陷等等,如何将ebi技术等检测技术应用至结构复杂的半导体器件,检测其中多类缺陷亟需解决。

技术实现思路

1、鉴于此,本申请提供一种半导体测试结构,以检测半导体器件的缺陷。

2、本申请提供一种半导体测试结构,包括:

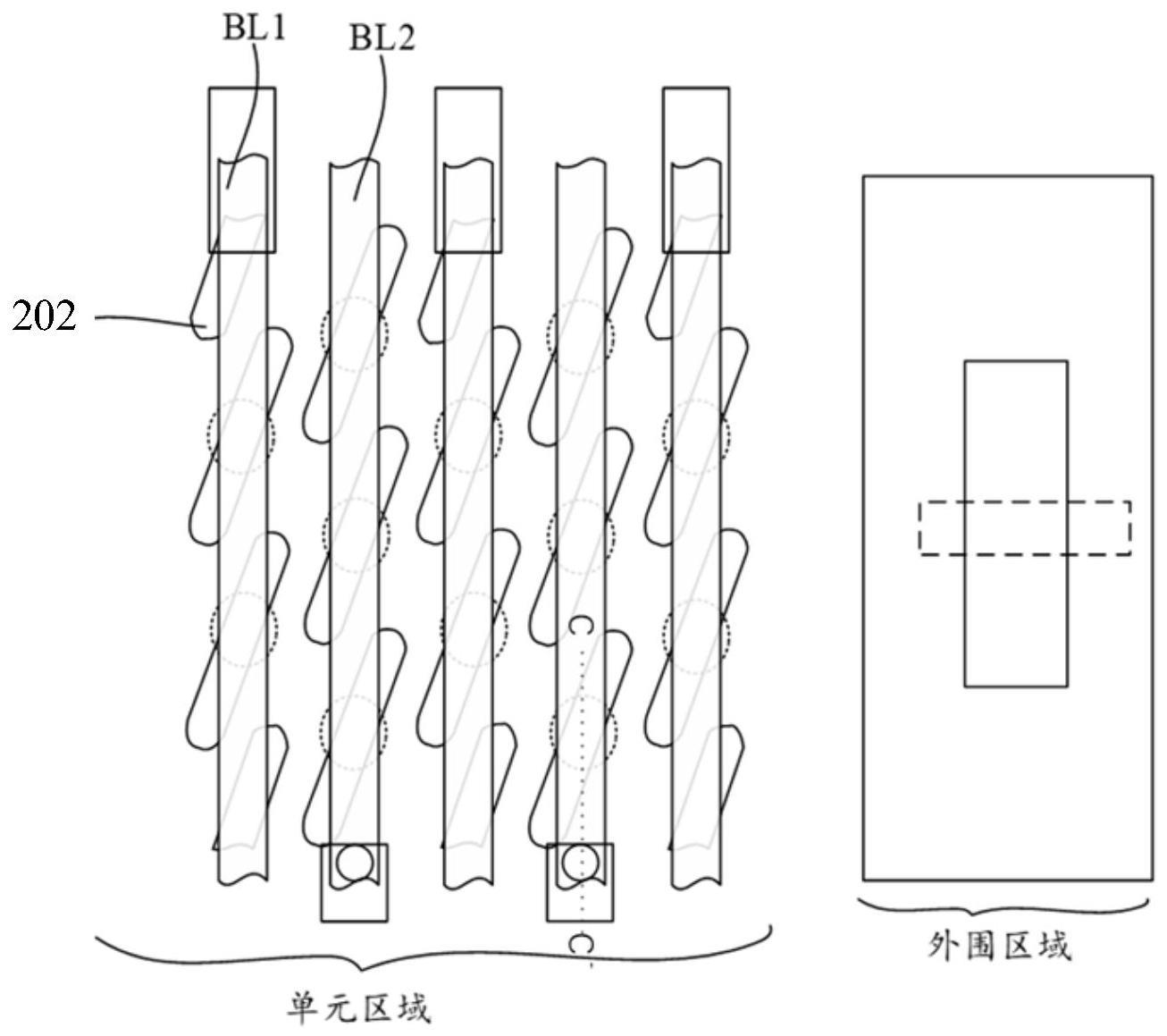

3、基底,包括单元区域和与所述单元区域相邻的外围区域,所述单元区域还包括单元隔离区和由所述单元隔离区定义的单元有源区;

4、多条位线,相互间隔地设置在所述基底上;

5、第一外围接触结构设置在所述外围区域上,其中,所述位线包括至少一条第一位线,所述至少一条第一位线不与所述第一外围接触结构电性连接。

6、可选地,半导体测试结构还包括:

7、第二外围接触结构,设置在所述外围区域上;

8、所述位线还包括第二位线,所述第二位线与所述第一位线在所述基底上交替排列设置;

9、所述第二位线与所述第二外围接触结构电性连接。

10、可选地,半导体测试结构还包括接触柱,所述接触柱设置在所述位线bl的一侧,且连接到所述单元有源区。

11、可选地,所述第一外围接触结构包括依序堆叠的外围有源区、绝缘层、金属图案。

12、可选地,所述第一外围接触结构包括依序堆叠的外围有源区、绝缘层,以及位线接触插塞,所述位线接触插塞穿过所述绝缘层连接所述外围有源区。

13、可选地,所述第二外围接触结构包括依序堆叠的外围有源区、绝缘层、金属图案;以及位线接触插塞,所述位线接触插塞一端连接所述金属图案,另一端穿过绝缘层与所述外围有源区连接。

14、本申请还提供一种半导体测试结构,包括:

15、基底,包括单元区域和与所述单元区域相邻的外围区域,所述单元区域还包括单元隔离区和由所述单元隔离区定义的单元有源区;

16、多条字线,相互间隔地设置在所述基底上;

17、多条位线,横跨所述多条字线,所述多条位线连接到所述单元有源区;

18、第一外围接触结构,设置在所述外围区域上,其中,所述字线包括至少一条第一字线,所述至少一条第一字线不与所述第一外围接触结构电性连接。

19、可选地,半导体测试结构还包括:

20、第二外围接触结构,设置在所述外围区域上;

21、所述字线还包括第二字线,所述第二字线与所述第一字线在所述基底上交替排列设置;

22、所述第二字线、所述位线分别与所述第二外围接触结构电性连接。

23、可选地,半导体测试结构还包括接触柱,所述接触柱设置在所述位线bl的一侧,且连接到所述单元有源区。

24、可选地,所述第一外围接触结构包括依序堆叠的外围有源区、绝缘层、金属图案。

25、可选地,所述第一外围接触结构包括依序堆叠的外围有源区、绝缘层,以及位线接触插塞,所述位线接触插塞穿过所述绝缘层连接所述外围有源区。

26、可选地,所述第二外围接触结构包括依序堆叠的外围有源区、绝缘层、金属图案;以及位线接触插塞,所述位线接触插塞一端连接所述金属图案,另一端穿过绝缘层与所述外围有源区连接。

27、上述半导体测试结构,在接入检测信号之后,其中相关区域或者相关组件可以对检测信号进行响应,响应特征可以表征上述半导体测试结构是否具有电性缺陷以及对应电性缺陷的类型,以此可以将对应检测设备对应的检测技术应用至复杂的半导体测试结构,实现对复杂半导体测试结构的测试,及时定位和处理对应缺陷,能够提升半导体测试结构在工作过程中的可靠性。

技术特征:

1.一种半导体测试结构,其中,包括:

2.根据权利要求1所述的半导体测试结构,其中,还包括:

3.根据权利要求1所述的半导体测试结构,其中,还包括接触柱,所述接触柱设置在所述位线的一侧,且连接到所述单元有源区。

4.根据权利要求1所述的半导体测试结构,其中,所述第一外围接触结构包括依序堆叠的外围有源区、绝缘层、金属图案。

5.根据权利要求1所述的半导体测试结构,其中,所述第一外围接触结构包括依序堆叠的外围有源区、绝缘层,以及位线接触插塞,所述位线接触插塞穿过所述绝缘层连接所述外围有源区。

6.根据权利要求2所述的半导体测试结构,其中,所述第二外围接触结构包括依序堆叠的外围有源区、绝缘层、金属图案;以及位线接触插塞,所述位线接触插塞一端连接所述金属图案,另一端穿过绝缘层与所述外围有源区连接。

7.一种半导体测试结构,其中,所述半导体测试结构包括:

8.根据权利要求7所述的半导体测试结构,其中,还包括:

9.根据权利要求7所述的半导体测试结构,其中,还包括接触柱,所述接触柱设置在所述位线的一侧,且连接到所述单元有源区。

10.根据权利要求7所述的半导体测试结构,其中,所述第一外围接触结构包括依序堆叠的外围有源区、绝缘层、金属图案。

11.根据权利要求7所述的半导体测试结构,其中,所述第一外围接触结构包括依序堆叠的外围有源区、绝缘层,以及位线接触插塞,所述位线接触插塞穿过所述绝缘层连接所述外围有源区。

12.根据权利要求8所述的半导体测试结构,其中,所述第二外围接触结构包括依序堆叠的外围有源区、绝缘层、金属图案;以及位线接触插塞,所述位线接触插塞一端连接所述金属图案,另一端穿过绝缘层与所述外围有源区连接。

技术总结

本申请公开一种半导体测试结构,包括:基底,包括单元区域和与所述单元区域相邻的外围区域,所述单元区域还包括单元隔离区和由所述单元隔离区定义的单元有源区;多条位线,相互间隔地设置在所述基底上;第一外围接触结构设置在所述外围区域上,其中,所述位线包括至少一条第一位线,所述至少一条第一位线不与所述第一外围接触结构电性连接。本申请可以将对应检测设备对应的检测技术应用至复杂的半导体测试结构,实现对复杂半导体测试结构的测试。

技术研发人员:洪朝臻,翁文毅,陈煌彬,陈瑛蕙

受保护的技术使用者:福建省晋华集成电路有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!