芯片封装体、形成芯片封装体的方法和芯片系统与流程

各种实施例总体上涉及一种芯片封装体、一种形成芯片封装体的方法以及一种芯片系统。

背景技术:

1、功率级封装体构造通常组合功率芯片(其例如可以相应地形成功率级封装体的高侧和/或低侧)和逻辑芯片。这种构造的优点可以是可以达到高峰值效率和高负载效率。这样的构造可以例如由包括再分布层的封装体来支持,以便最小化寄生效应并且允许逻辑芯片互连通常所需的必要的紧密间距。这种紧密的互连间距通常不能通过本领域目前使用的芯片嵌入技术来实现。

技术实现思路

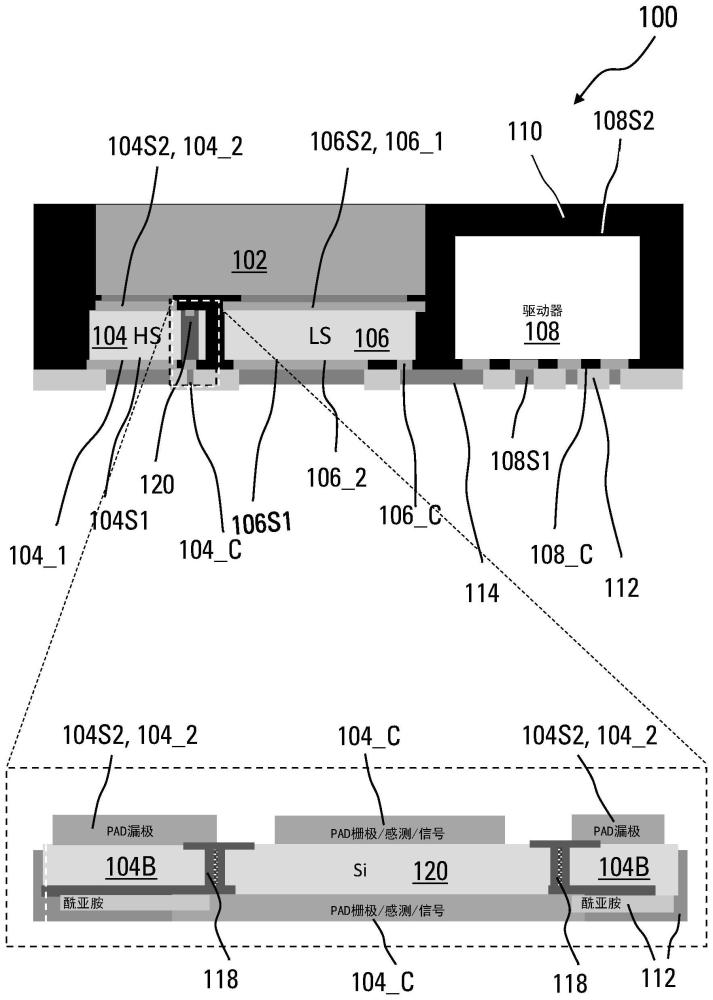

1、提供了一种芯片封装体。所述芯片封装体包括:导电载体结构;第一功率芯片,其布置在所述载体结构上,其中,所述第一功率芯片包括具有控制接触焊盘和第一类型的受控接触焊盘的第一侧、与所述第一侧相反且包括第二类型的受控接触焊盘的第二侧和用于控制所述受控接触焊盘之间的电流的控制结构,其中,所述控制接触焊盘通过过孔电连接到所述控制结构;第二功率芯片,其布置在所述载体结构上,其中,所述第二功率芯片包括具有控制接触焊盘和第二类型的受控接触焊盘的第一侧、与所述第一侧相反且包括第一类型的受控接触焊盘的第二侧和用于控制所述第二功率芯片的受控接触焊盘之间的电流的控制结构,其中,所述控制接触焊盘电连接到所述控制结构;具有逻辑接触焊盘的逻辑芯片;再分布层;以及模制材料,其至少部分地包封所述载体结构、所述第一功率芯片、所述第二功率芯片和所述逻辑芯片;其中,所述第一功率芯片和所述第二功率芯片被布置成使得它们相应的控制接触焊盘面向所述再分布层,并且所述逻辑芯片被布置成使得所述逻辑接触焊盘面向所述再分布层;并且其中,所述再分布层将所述逻辑接触焊盘与所述第一功率芯片和所述第二功率芯片的相应的控制接触焊盘电连接。

技术特征:

1.一种芯片封装体,包括:

2.根据权利要求1所述的芯片封装体,

3.根据权利要求1或2所述的芯片封装体,

4.根据权利要求1-3中任一项所述的芯片封装体,

5.根据权利要求1-4中任一项所述的芯片封装体,

6.根据权利要求1-5中任一项所述的芯片封装体,

7.根据权利要求1-6中任一项所述的芯片封装体,

8.根据权利要求1-7中任一项所述的芯片封装体,

9.根据权利要求1-8中任一项所述的芯片封装体,

10.根据权利要求1-9中任一项所述的芯片封装体,

11.一种形成芯片封装体的方法,所述方法包括:

12.根据权利要求11所述的方法,

13.根据权利要求12所述的方法,

14.根据权利要求11-13中任一项所述的方法,

15.根据权利要求11-14中任一项所述的方法,

16.根据权利要求11-15中任一项所述的方法,

17.根据权利要求11-16中任一项所述的方法,

18.根据权利要求11-17中任一项所述的方法,

19.根据权利要求11-18中任一项所述的方法,

20.根据权利要求11-19中任一项所述的方法,

21.根据权利要求11-20中任一项所述的方法,

22.根据权利要求11-21中任一项所述的方法,所述方法还包括:

23.根据权利要求11-22中任一项所述的方法,

24.根据权利要求11-23中任一项所述的方法,

25.一种芯片系统,包括:

技术总结

一种芯片封装体包括:导电载体结构;第一功率芯片,其布置在载体结构上且包括具有控制接触焊盘和第一类型的受控接触焊盘的第一侧、包括第二类型的受控接触焊盘的相反的第二侧和用于控制受控接触焊盘之间的电流的控制结构,控制接触焊盘通过过孔电连接到控制结构;第二功率芯片,其布置在载体结构上且包括具有控制接触焊盘和第二类型的受控接触焊盘的第一侧、包括第一类型的受控接触焊盘的相反的第二侧和用于控制受控接触焊盘之间的电流的控制结构,控制接触焊盘电连接到控制结构;逻辑芯片;再分布层;和模制材料;功率芯片的控制接触焊盘面向再分布层,逻辑芯片的逻辑接触焊盘面向再分布层;再分布层将逻辑接触焊盘与相应的控制接触焊盘连接。

技术研发人员:T·迈尔,A·凯斯勒,T·沙夫

受保护的技术使用者:英飞凌科技股份有限公司

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!