包括通孔阵列的集成电路的制作方法

本发明概念涉及一种集成电路(ic),且更具体来说涉及一种包括通孔阵列的集成电路及其制造方法。

背景技术:

1、随着半导体工艺的小型化,集成电路中所包括的图案可具有减小的宽度和/或厚度。因此,由图案造成的电压(ir)降的影响可能增加。为了减小在不同的导电层中形成的导电图案之间的电压降(ir drop),可使用包括多个通孔的通孔阵列。在通孔阵列中所包括的通孔可彼此间隔开以符合设计规则,且连接到通孔的导电图案可包括附加区域,所述附加区域可被称为通孔交叠(via overlap)。因此,由通孔阵列产生的通孔及通孔交叠可降低在集成电路的布局中的可布线性并导致布线拥塞(routing congestion)。

技术实现思路

1、本发明概念提供一种包括通孔阵列的集成电路(integrated circuit,ic)。更具体来说,本发明概念提供被配置成提供改善的可布线性的通孔阵列、包括所述通孔阵列的集成电路及制造所述集成电路的方法。

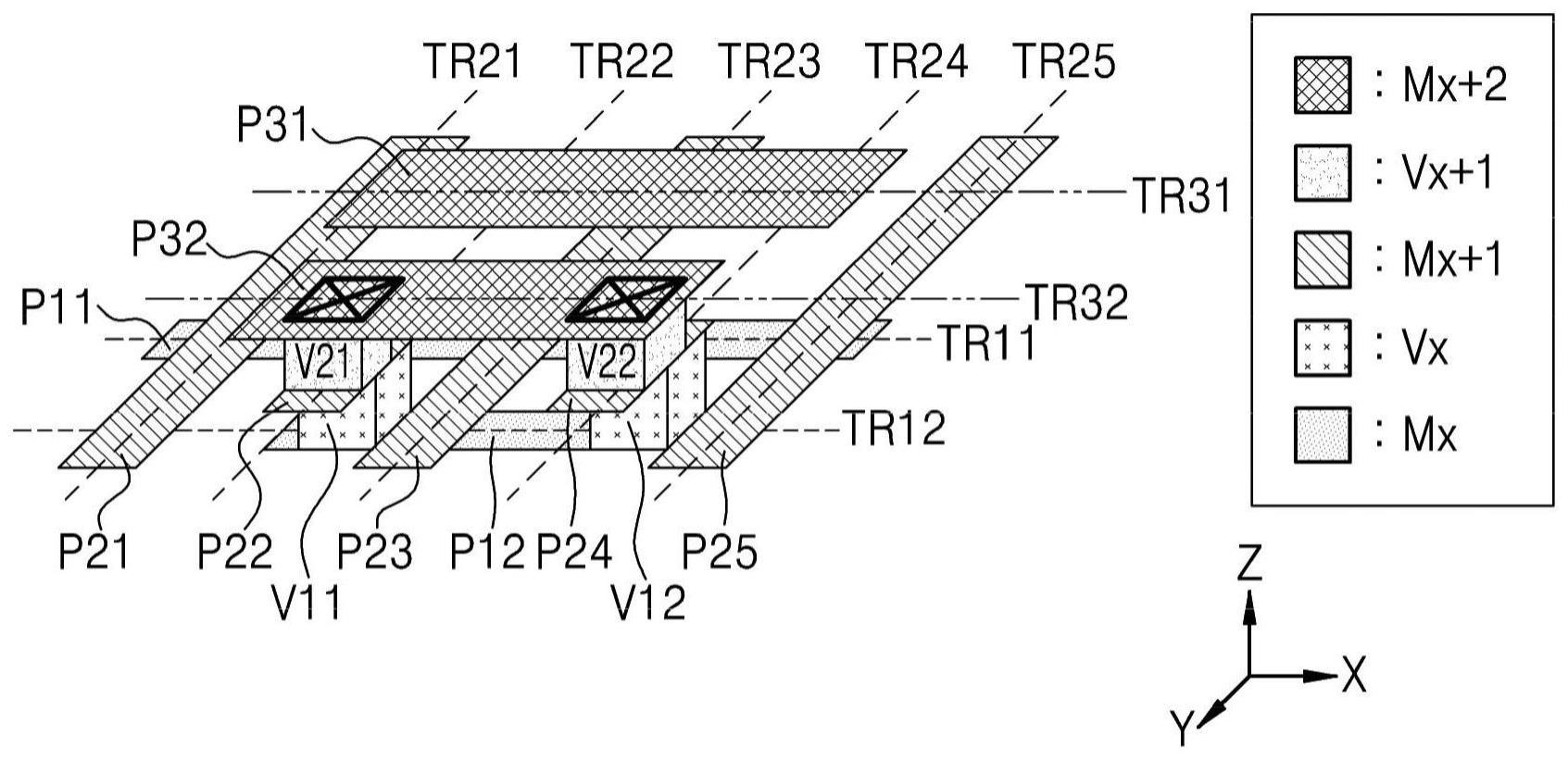

2、根据本发明概念的方面,提供一种集成电路,所述集成电路包括:第一导电层,包括在第一横向方向上彼此平行地延伸的第一迹线(track)上的导电图案中的第一导电图案;第二导电层,包括在第二横向方向上彼此平行地延伸的第二迹线上的导电图案中的第二导电图案及第三导电图案;第三导电层,包括在所述第一横向方向上彼此平行地延伸的第三迹线上的导电图案中的第四导电图案;第一通孔阵列,包括第一通孔及第二通孔,其中所述第一通孔连接到所述第一导电图案的顶表面及所述第二导电图案的底表面,且其中所述第二通孔连接到所述第一导电图案的所述顶表面及所述第三导电图案的底表面;以及第二通孔阵列,包括第三通孔及第四通孔,其中所述第三通孔连接到所述第二导电图案的顶表面及所述第四导电图案的底表面,且其中所述第四通孔连接到所述第三导电图案的顶表面及所述第四导电图案的所述底表面。所述第二导电层还包括第五导电图案,所述第五导电图案对准所述第二迹线中位于所述第二导电图案与所述第三导电图案之间的一者,所述第五导电图案在所述第二横向方向上延伸且不与所述第二导电图案及所述第三导电图案耦合。

3、根据本发明概念的另一方面,提供一种集成电路,所述集成电路包括:第一导电层,包括在第一横向方向上彼此平行地延伸的第一迹线上的导电图案中的第一导电图案以及在所述第一横向方向上延伸的第一导电图案;第二导电层,包括在第二横向方向上彼此平行地延伸的第二迹线上的导电图案中的第二导电图案及第三导电图案,所述第二横向方向与所述第一横向方向正交;以及第一通孔阵列,包括第一通孔及第二通孔,其中所述第一通孔连接到所述第一导电图案的顶表面及所述第二导电图案的底表面,且其中所述第二通孔连接到所述第一导电图案的所述顶表面及所述第三导电图案的底表面。所述第一导电图案、所述第一通孔及所述第二通孔中的每一者在所述第二横向方向上的长度大于所述第一导电层的所述第一迹线上的所述导电图案在所述第二横向方向上的长度。所述第一导电图案的中心对准所述第一导电层的所述第一迹线中的一者或者对准所述第一导电层的两个相邻的第一迹线之间的中心线。

4、根据本发明概念的方面,提供一种集成电路,所述集成电路包括:第一导电层,包括在第一横向方向上彼此平行地延伸的第一迹线上的导电图案中的第一导电图案;第二导电层,包括在第二横向方向上彼此平行地延伸的第二迹线上的导电图案中的第二导电图案及第三导电图案;第三导电层,包括在所述第一横向方向上彼此平行地延伸的第三迹线上的导电图案中的第四导电图案;第一通孔阵列,包括第一通孔,所述第一通孔中的每一者连接到所述第一导电图案的顶表面以及连接到所述第二导电图案的底表面及所述第三导电图案的底表面中的至少一者;以及第二通孔阵列,包括第二通孔,所述第二通孔中的每一者连接到所述第二导电图案的顶表面及所述第三导电图案的顶表面中的至少一者,且连接到所述第四导电图案的底表面。所述第一通孔阵列的所述第一通孔位于所述第一迹线与所述第二迹线在平面图中的交叉处。所述第二通孔阵列的所述第二通孔位于所述第二迹线与所述第三迹线在所述平面图中的交叉处。

5、根据本发明概念的另一方面,提供一种制造集成电路的方法。所述方法包括:基于胞元库及用于界定所述集成电路的输入数据来放置及布线多个标准胞元,其中所述放置及布线所述多个标准胞元包括:添加通孔堆叠,所述通孔堆叠被配置成对所述多个标准胞元的电源轨(power rail)与电源网(power mesh)进行互连。所述添加所述通孔堆叠包括:将通孔排列在所述集成电路的相邻的导电层的迹线之间的在平面图中的交叉处。

技术特征:

1.一种集成电路,所述集成电路包括:

2.根据权利要求1所述的集成电路,其中,如果所述第一导电图案的宽度w满足式子2np-m-2s<w≤(2n+1)p-m-2s,则所述第一导电图案与所述第一导电层的所述两个相邻第一迹线之间的所述中心线对准,并且

3.根据权利要求1所述的集成电路,其中,所述第一导电图案、所述第一通孔和所述第二通孔在所述第二横向方向上具有相同的长度。

4.根据权利要求1所述的集成电路,其中,所述第一通孔与所述第二通孔之间的第一节距是所述第二导电层的所述第二迹线之间的第二节距的倍数。

5.根据权利要求1所述的集成电路,所述集成电路还包括:

6.根据权利要求5所述的集成电路,其中,所述第四导电图案、所述第三通孔和所述第四通孔中的每者在所述第二横向方向上的长度大于所述第三导电层的所述第三迹线上的所述导电图案在所述第二横向方向上的长度,并且

7.一种集成电路,所述集成电路包括:

8.根据权利要求7所述的集成电路,其中,如果所述第一导电图案的宽度w满足式子2np-m-2s<w≤(2n+1)p-m-2s,则所述第一导电图案与所述第一导电层的两个相邻第一迹线之间的所述中心线对准,并且

9.根据权利要求7所述的集成电路,其中,所述第一导电图案、所述第一通孔和所述第二通孔在所述第二横向方向上具有相同的长度。

10.根据权利要求7所述的集成电路,其中,所述第一通孔与所述第二通孔之间的第一节距是所述第二导电层的所述第二迹线之间的第二节距的倍数。

11.根据权利要求7所述的集成电路,所述集成电路还包括:

12.根据权利要求11所述的集成电路,其中,所述第四导电图案在所述第二横向方向上的长度大于所述第三导电层的所述第三迹线的节距,并且

13.一种集成电路,所述集成电路包括:

14.根据权利要求13所述的集成电路,其中,所述第一导电图案在所述第二横向方向上的长度大于所述第一导电层的所述第一迹线的节距。

15.根据权利要求14所述的集成电路,其中,所述第一导电图案在所述第二横向方向上的长度小于所述第一导电层的所述第一迹线的两个节距。

16.根据权利要求13所述的集成电路,其中,所述第一通孔和所述第二通孔在所述第二横向方向上的长度大于所述第一导电层的所述第一迹线的节距。

17.根据权利要求13所述的集成电路,其中,所述第一通孔的中心和所述第二通孔的中心与所述第一导电层的所述两个相邻第一迹线之间的所述中心线对准。

18.根据权利要求13所述的集成电路,其中,所述第一通孔与所述第二通孔之间的第一节距是所述第二导电层的所述第二迹线之间的第二节距的倍数。

19.根据权利要求13所述的集成电路,所述集成电路还包括:

20.根据权利要求19所述的集成电路,其中,所述第四导电图案在所述第二横向方向上的长度大于所述第三导电层的所述第三迹线的节距,并且

技术总结

本公开提供一种集成电路(IC)。集成电路包括通孔堆叠,且所述通孔堆叠包括包含位于相同水平高度处的多个通孔的通孔阵列。通孔阵列的多个通孔排列在相邻的导电层的迹线之间的交叉处且沿所述迹线之间的中心线排列。此外,通孔交叠平行于导电层的迹线延伸。因此,可减少因通孔阵列而被牺牲的迹线的数目,且集成电路可因改善的可布线性而具有增强的性能及减小的面积。

技术研发人员:金容德

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!