一种芯片结构及其形成方法、芯片封装结构及其形成方法与流程

本申请涉及芯片,尤其涉及一种芯片结构及其形成方法、芯片封装结构及其形成方法。

背景技术:

1、打线封装技术(wb,wire bonding)是芯片与封装基板之间电路互联的最常用的使用方式。打线封装时需要使用焊接工艺通过金属引线将芯片上的金属焊垫与基板上的金属焊垫进行焊接实现电连接。然而,在金属焊垫上进行焊接工艺时,焊接工艺产生的高温会导致金属焊垫以及金属焊垫下方的位置产生不可控的应力变化,该应力变化可能导致介质层破裂甚至介质层中的金属走线失败等问题。

2、因此,有必要提供一种更有效、更可靠的技术方案,避免在打线焊接时导致芯片上层间介质层破裂以及金属互连结构失效,提高打线封装可靠性。

技术实现思路

1、本申请提供一种芯片结构及其形成方法、芯片封装结构及其形成方法,可以避免在打线焊接时导致芯片上层间介质层破裂以及金属互连结构失效,提高打线封装可靠性。

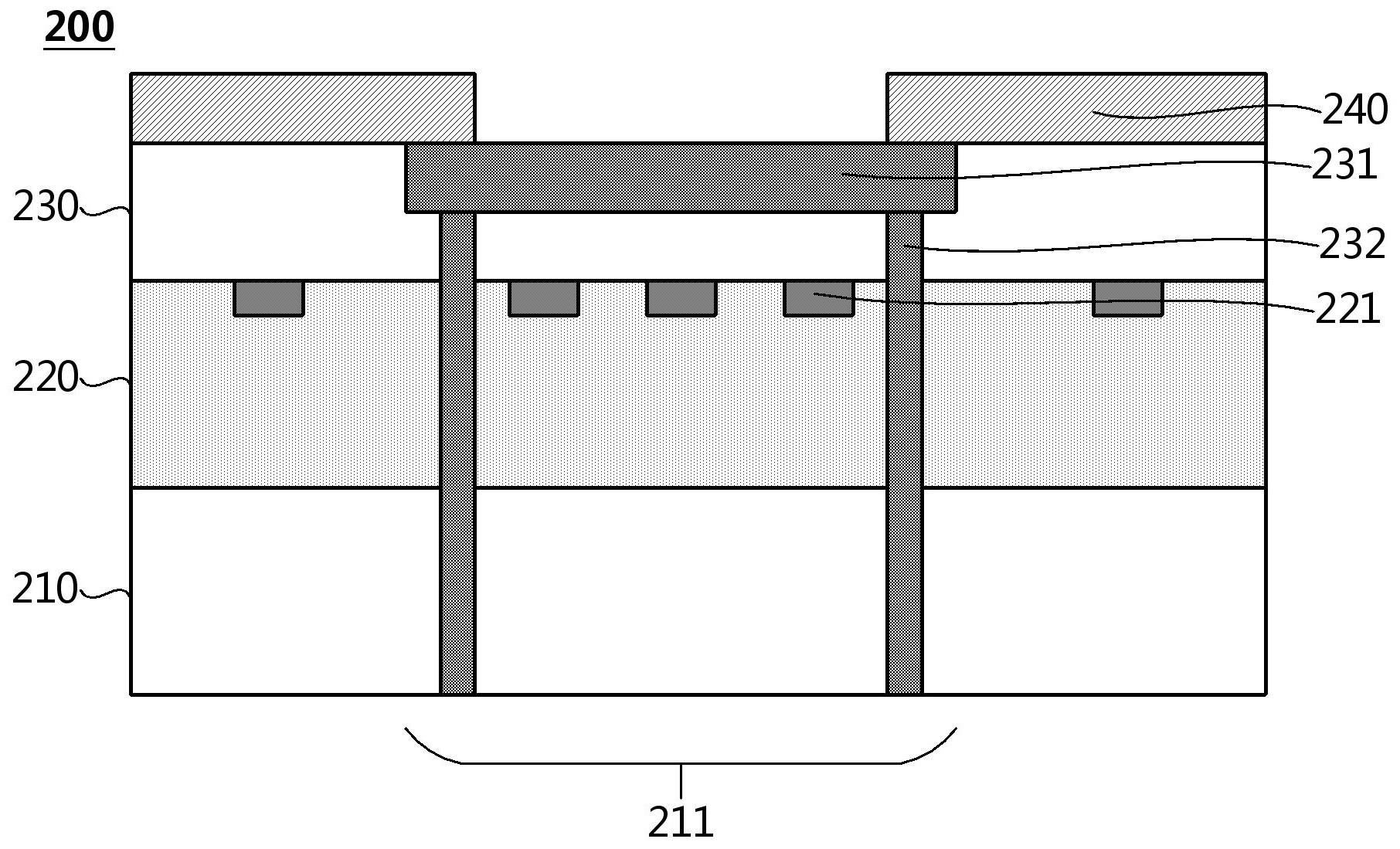

2、本申请的一个方面提供一种芯片结构的形成方法,包括:提供基底,所述基底中包括有源器件以及输入/输出端口,所述基底包括若干焊垫区;在所述基底表面形成层间介质层以及位于所述层间介质层中电连接所述有源器件的金属互连结构,所述金属互连结构包括顶层金属层,其中,部分所述顶层金属层位于所述若干焊垫区中;在所述层间介质层表面形成封装介质层以及位于所述封装介质层中与所述若干焊垫区位置对应的封装焊垫,所述封装焊垫与所述输入/输出端口电连接,所述封装焊垫的厚度大于等于18纳米;在所述封装介质层表面形成钝化层,所述钝化层暴露部分所述封装焊垫。

3、在本申请的一些实施例中,位于所述若干焊垫区中的部分顶层金属层在所述若干焊垫区的投影均匀分布。

4、在本申请的一些实施例中,位于每个焊垫区中的部分顶层金属层在所述焊垫区的投影的总面积占所述焊垫区的面积的占比大于50%。

5、在本申请的一些实施例中,所述层间介质层中还形成有若干位于所述焊垫区中与所述顶层金属层同层的虚拟金属层,位于所述若干焊垫区中的部分顶层金属层以及若干虚拟金属层在所述若干焊垫区的投影均匀分布,位于每个焊垫区中的部分顶层金属层以及若干虚拟金属层在所述焊垫区的投影的总面积占所述焊垫区的面积的占比大于50%。

6、本申请的一个方面还提供一种芯片结构,包括:基底,所述基底中包括有源器件以及输入/输出端口,所述基底包括若干焊垫区;位于所述基底表面的层间介质层以及位于所述层间介质层中电连接所述有源器件的金属互连结构,所述金属互连结构包括顶层金属层,其中,部分所述顶层金属层位于所述若干焊垫区中;位于所述层间介质层表面的封装介质层以及位于所述封装介质层中与所述若干焊垫区位置对应的封装焊垫,所述封装焊垫与所述输入/输出端口电连接,所述封装焊垫的厚度大于等于18纳米;位于所述封装介质层表面的钝化层,所述钝化层暴露部分所述封装焊垫。

7、在本申请的一些实施例中,位于所述若干焊垫区中的部分顶层金属层在所述若干焊垫区的投影均匀分布。

8、在本申请的一些实施例中,位于每个焊垫区中的部分顶层金属层在所述焊垫区的投影的总面积占所述焊垫区的面积的占比大于50%。

9、在本申请的一些实施例中,所述层间介质层中还包括若干位于所述焊垫区中与所述顶层金属层同层的虚拟金属层,位于所述若干焊垫区中的部分顶层金属层以及若干虚拟金属层在所述若干焊垫区的投影均匀分布,位于每个焊垫区中的部分顶层金属层以及若干虚拟金属层在所述焊垫区的投影的总面积占所述焊垫区的面积的占比大于50%。

10、本申请的另一个方面提供一种芯片封装结构的形成方法,包括:提供封装基板,所述封装基板表面包括金属焊垫;将如上述所述的芯片结构封装于所述封装基板上;通过金属引线将所述芯片结构上的封装焊垫与所述金属焊垫电连接。

11、本申请的另一个方面还提供一种芯片封装结构,包括:封装基板,所述封装基板表面包括金属焊垫;如上述所述的芯片结构,封装于所述封装基板上;金属引线,将所述芯片结构上的封装焊垫与所述金属焊垫电连接。

12、本申请提供一种芯片结构及其形成方法、芯片封装结构及其形成方法,可以避免在打线焊接时导致芯片上层间介质层破裂以及金属互连结构失效,提高打线封装可靠性。

技术特征:

1.一种芯片结构的形成方法,所述芯片结构用于打线封装,其特征在于,包括:

2.如权利要求1所述的芯片结构的形成方法,其特征在于,位于所述若干焊垫区中的部分顶层金属层在所述若干焊垫区的投影均匀分布。

3.如权利要求2所述的芯片结构的形成方法,其特征在于,位于每个焊垫区中的部分顶层金属层在所述焊垫区的投影的总面积占所述焊垫区的面积的占比大于50%。

4.如权利要求1所述的芯片结构的形成方法,其特征在于,所述层间介质层中还形成有若干位于所述焊垫区中与所述顶层金属层同层的虚拟金属层,位于所述若干焊垫区中的部分顶层金属层以及若干虚拟金属层在所述若干焊垫区的投影均匀分布,位于每个焊垫区中的部分顶层金属层以及若干虚拟金属层在所述焊垫区的投影的总面积占所述焊垫区的面积的占比大于50%。

5.一种芯片结构,所述芯片结构用于打线封装,其特征在于,包括:

6.如权利要求5所述的芯片结构,其特征在于,位于所述若干焊垫区中的部分顶层金属层在所述若干焊垫区的投影均匀分布。

7.如权利要求6所述的芯片结构,其特征在于,位于每个焊垫区中的部分顶层金属层在所述焊垫区的投影的总面积占所述焊垫区的面积的占比大于50%。

8.如权利要求5所述的芯片结构,其特征在于,所述层间介质层中还包括若干位于所述焊垫区中与所述顶层金属层同层的虚拟金属层,位于所述若干焊垫区中的部分顶层金属层以及若干虚拟金属层在所述若干焊垫区的投影均匀分布,位于每个焊垫区中的部分顶层金属层以及若干虚拟金属层在所述焊垫区的投影的总面积占所述焊垫区的面积的占比大于50%。

9.一种芯片封装结构的形成方法,其特征在于,包括:

10.一种芯片封装结构,其特征在于,包括:

技术总结

本申请提供一种芯片结构及其形成方法、芯片封装结构及其形成方法,所述芯片结构包括:基底,所述基底中包括有源器件以及输入/输出端口,所述基底包括若干焊垫区;位于所述基底表面的层间介质层以及位于所述层间介质层中的金属互连结构,所述金属互连结构包括顶层金属层,部分所述顶层金属层位于所述若干焊垫区中;位于所述层间介质层表面的封装介质层以及位于所述封装介质层中与所述若干焊垫区位置对应的封装焊垫,所述封装焊垫的厚度大于等于18纳米;位于所述封装介质层表面的钝化层,所述钝化层暴露部分所述封装焊垫。本申请的技术方案可以避免在打线焊接时导致芯片上层间介质层破裂以及金属互连结构失效,提高打线封装可靠性。

技术研发人员:戴佼容

受保护的技术使用者:芯耀辉科技有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!