一种共晶烧结工艺用工装的制作方法

本发明涉及半导体器件封装,具体地说就是一种共晶烧结工艺用工装。

背景技术:

1、随军用、航空、航天、汽车电子等领域,对电子产品提出了严苛的可靠性、小型化、低成本要求,传统非气密的塑封封装难以满足可靠性要求,而陶瓷可伐一体化封装管壳、金属一体化封装管壳成为一个优选,其优异的气密性保证了产品的可靠性,相对紧凑且制造成本较低,可满足绝大部分高可靠性器件的要求。该类型封装产品的最后一道工序是封盖,如何高质量、高效的完成气密封盖是保证产品可靠性的关键。

2、共晶烧结封盖工艺用于实现盖板和管壳之间的气密焊接, 是一种气密性高、可靠性高的气密封装技术,可实现1mm以上一定尺寸范围的各种矩形和圆形产品封装,以及成本低廉等,在陶瓷可伐一体化管壳、金属一体化封装管壳封装领域得到广泛应用。

3、共晶烧结的工作原理是熔封,通过在盖板与管壳之间加夹装焊料片,通过高温使焊料环熔融,降温后形成高可靠性气密性封装的封接区域。目前共晶烧结设备主要有两种,一种为炉管加热共晶烧结,其热传导方式主要为氮气环境下的气体传导热量与真空环境下的热辐射传导热量;另一种为加热板形式的共晶烧结设备,其热传导方式主要为热板与材料间的热传递。

4、但现阶段共晶封装电路通过钼夹夹装电路实现共晶烧结,使用钼夹夹装电路存在管壳本体受热需要通过钼夹导热,钼夹与电路管壳本体接触面积较小,且夹装时难以保证夹装在管壳正中心,容易使管壳本体受热传递不均匀而出现焊料熔融不均,从而导致产品检漏不合格或成品外观不合格。

技术实现思路

1、本发明就是为了克服现有技术中的不足,提供一种共晶烧结工艺用工装。

2、本申请提供以下技术方案:

3、一种共晶烧结工艺用工装,其特征在于:它包括对应配合的上模和下模,在下模上均布有一组芯片放置槽,在上模上均布有一组与芯片放置槽对应分布的插孔,在每个插孔还插设有可移动的压杆。

4、在上述技术方案的基础上,还可以有以下进一步的技术方案:

5、在所述的上模上架体,在架体均布有一组与插孔对应分布的压杆插孔,压杆的上端部穿套在插孔内。

6、在所述芯片放置槽的槽底面上还设有芯片引脚放置槽,所述的芯片放置槽与芯片引脚放置槽的中心点为同轴分布。

7、在所述插孔下端的孔壁上伸出一对工件限位齿。

8、所述的一对工件限位齿为对称分布,并沿水平方向伸出。

9、在所述压杆的下端部设有直径缩小段。

10、在所述上模和下模的厚度端面上均布有一组水平分布的气流孔。

11、所述上模和下模石墨制成,在上模和下模的表面上还设有碳化硅镀层。

12、在所述下模设置有一组对位柱,在上模上设有一组与对位柱对应配合u形卡槽。

13、发明优点:

14、本发明结构简单、使用方便能有效的提高电路共晶烧结过程中,器件四周升温均匀性,有效的提升了器件的封装效率和封装质量。

技术特征:

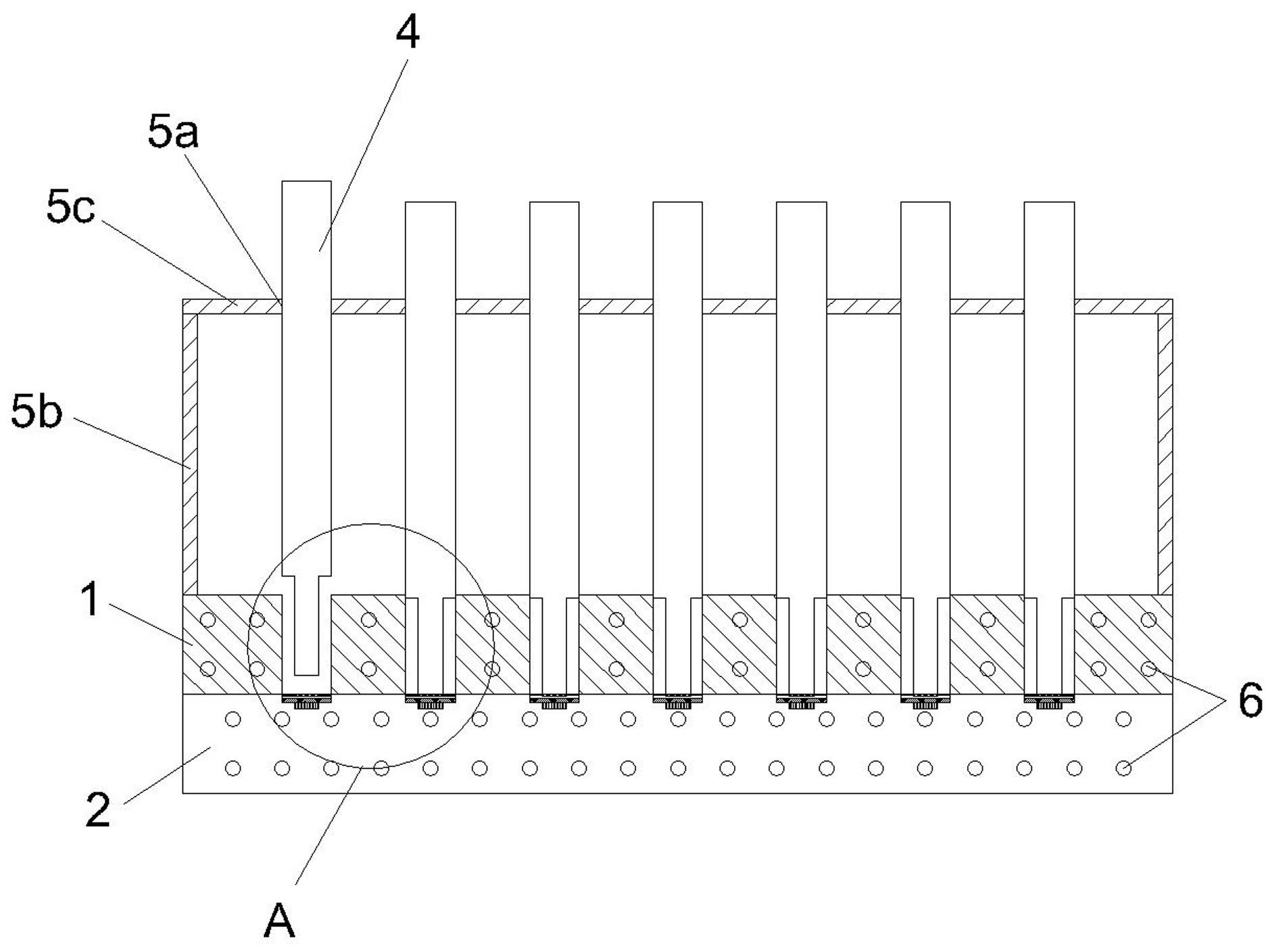

1.一种共晶烧结工艺用工装,其特征在于:它包括对应配合的上模(1)和下模(2),在下模(2)上均布有一组芯片放置槽(2a),在上模(1)上均布有一组与芯片放置槽(2a)对应分布的插孔(1a),在每个插孔(1a)还插设有可移动的压杆(4)。

2.根据权利要求1中所述的一种共晶烧结工艺用工装,其特征在于:在所述的上模(1)上设有架体(5),在架体(5)均布有一组与插孔(1a)对应分布的压杆插孔(5a),压杆(4)的上端部穿套在插孔(5a)内。

3.根据权利要求1中所述的一种共晶烧结工艺用工装,其特征在于:在所述芯片放置槽(2a)的槽底面上还设有芯片引脚放置槽(2b),所述的芯片放置槽(2a)与芯片引脚放置槽(2b)的中心点为同轴分布。

4.根据权利要求1中所述的一种共晶烧结工艺用工装,其特征在于:在所述插孔(1a)下端的孔壁上伸出一对工件限位齿(1b)。

5.根据权利要求4中所述的一种共晶烧结工艺用工装,其特征在于:所述的一对工件限位齿(1b)为对称分布,并沿水平方向伸出。

6.根据权利要求1-5中任意项所述的一种共晶烧结工艺用工装,其特征在于:在所述压杆(4)的下端部设有直径缩小段(4a)。

7.根据权利要求6中所述的一种共晶烧结工艺用工装,其特征在于:在所述上模(1)和下模(2)的厚度端面上均布有一组水平分布的气流孔(6)。

8.根据权利要求7中所述的一种共晶烧结工艺用工装,其特征在于:所述上模(1)和下模(2)石墨制成,在上模(1)和下模(2)的表面上还设有碳化硅镀层。

9.根据权利要求8中所述的一种共晶烧结工艺用工装,其特征在于:在所述下模(2)设置有一组对位柱(2c),在上模(1)上设有一组与对位柱(2c)对应配合u形卡槽(1c)。

技术总结

本发明提供一种共晶烧结工艺用工装,其特征在于:它包括对应配合的上模(1)和下模(2),在下模(2)上均布有一组芯片放置槽(2a),在上模(1)上均布有一组与芯片放置槽(3)对应分布的插孔(1a),在每个插孔(1a)还插设有可移动的压杆(4)。本发明结构简单、使用方便能有效的提高电路共晶烧结过程中,器件四周升温均匀性,有效的提升了器件的封装效率和封装质量。

技术研发人员:曹燚,刘文军,向圆,陈龙鑫

受保护的技术使用者:华东光电集成器件研究所

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!